Оптимизатор режима работы интегрирующего

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 368553

Авторы: Вительленинградский, Донецка, Нтки, Ситкин

Текст

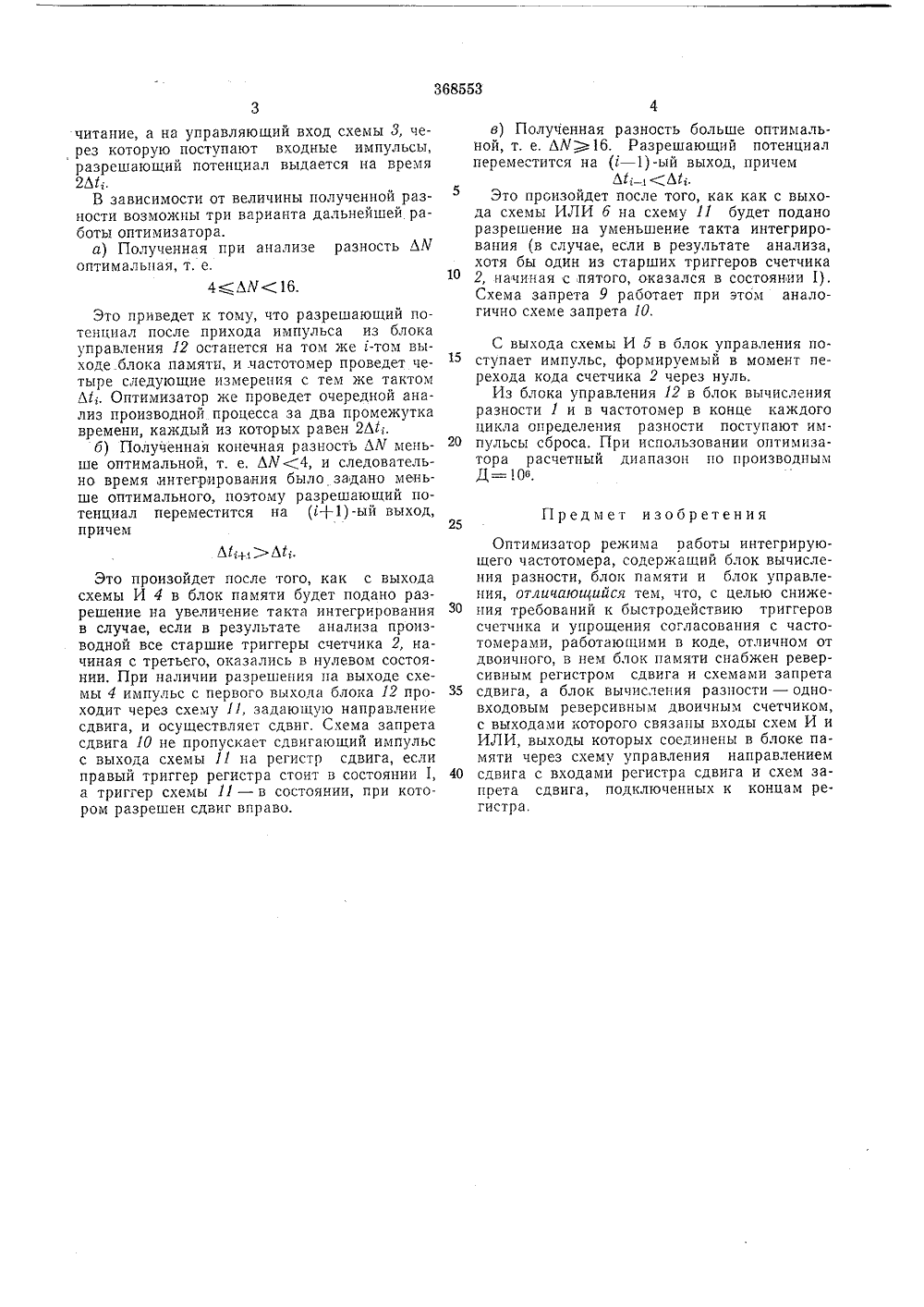

ОПИСАНИЕ 368553ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советскин Социалистнческиз реолтблинвисимое от авт. свидетельстваявлено 18 Х.1971 ( 1658199118-10) 1. Кл 1 г 23 ением заявкиприсоед делам Комитет иаобретеми ори Советиоритет Р и открытие МинистровССР 73. БюллетеньК 621.317.761(088,8) публиковано ата опубликования описания 6.1 К 193. В, Донецкая, Д, Е, Звонков и Ю. В, Ситкин Ленинградский политехнический институт им. М. И, КалининаЗаявител ТИМИЗАТОР РЕЖИМА РАБОТЫ ИНТЕГРИРУЮЩЕГО ЧАСТОТОМЕРАНа чертеже приведена блок-схема оптимизатора.Оптимизатор состоит из блока вычисленияразности 1, образованного одновходовым реверсивным двоичным счетчиком 2, схемами И 8, 4, б и схемой ИЛИ б, блока памяти 7, образованного реверсивным регистром сдвига 8, схемами запрета 9, 10 и схемой управления направлением сдвига 11, блока управления 12.Оптимизатор работает следующим образом.Если в результате анализа динамическихсвойств исследуемого процесса в течение предыдущего цикла оптимизатором был выбран 15 1-тый режим работы частотомера, то на 1-томвыходе блока памяти 7 установится потенциал, разрешающий работу частотомера с тактом Л 1 и анализ производной процесса в течение 20 Л Блок управления товых импульса, по вход и следующих с два промежутка вр 25 первого из которых рует импульсы част рого - импульсы ча полученной суммы. дает на шины знака 30 потенциал либо на сИзобретение относится к области электроизмерительной техники и может быть использовано для снижения требований к быстродействию триггеров счетчика оптимизатора и упрощения согласования оптимизатора с частотомерами, работающими в коде, отличном от двоичного.Известный оптимизатор режима работы интегрирующего частотомера, содержащий блок вычисления разности, блок памяти и блок управления, характеризуется повышенными требованиями к быстродействию триггеров счетчика и сложностью согласования с частотомерами, работающими в коде отличном от двоичного. Предлагаемый оптимизатор, отличается тем, что в нем блок памяти снабжен реверсивным регистром сдвига и схемами запрета сдвига, а блок вычисления разности - одновходовым реверсивным двоичным счетчиком, с выходами которого связаны входы схем И и ИЛИ, выходы которых соединены в блоке памяти через схему управления направлением сдвига с входами регистра сдвига и схем запрета сдвига, подключенных к концам регистра. Это снижает требования к быстродействию триггеров счетчика и упрощает согласование с частотомерами, работающими в коде, отличном от двоичного,т;=4 М;12, используя четыре такступающих на его первыйпериодом Л 1 формирует емени по 2 Л 1 ь в течение счетчик 2 блока 1 суммиоты Р(1), а в течение втостоты г(1) вычитаются из Блок управления 12 высчетчика 2 разрешающий уммирование, либо на вычитание, а на управляющий вход схемы 3, через которую поступают входные импульсы, разрешающий потенциал выдается на время 2 М;,В зависимости от величины полученной разности возможны три варианта дальнейшей работы оптимизатора.а) Полученная при анализе разность ЛМ оптимальная, т. е,4(ЛМ(16.Это приведет к тому, что разрешающий потенциал после прихода импульса из блока управления 12 останется на том же -том выходе. блока памяти, и.частотомер проведет четыре следующие измерения с тем же тактом Л 1;. Оптимизатор же проведет очередной анализ производной процесса за два промежутка времени, каждый из которых равен 2 Л 1;.б) Полученная конечная разность ЛУ меньше оптимальной, т. е. ЛУ(4, и следовательно время интегрирования было задано меньше оптимального, поэтому разрешающий потенциал переместится на (+1) -ый выход, причем Это произойдет после того, как с выхода схемы И 4 в блок памяти будет подано разрешение на увеличение такта интегрирования в случае, если в результате анализа производной все старшие триггеры счетчика 2, начиная с третьего, оказались в нулевом состоянии. При наличии разрешения па выходе схемы 4 импульс с первого выхода блока 12 проходит через схему 11, задающую направление сдвига, и осуществляет сдвиг. Схема запрета сдвига 10 не пропускает сдвигающий импульс с выхода схемы 11 на регистр сдвига, если правый триггер регистра стоит в состоянии 1, а триггер схемы 11 - в состоянии, при котором разрешен сдвиг вправо. в) Полученная разность больше оптимальной, т. е, ЛМ)16. Разрешающий потенциал переместится на (1 - 1)-ый выход, причемЛ 1(Л 1;.Это произойдет после того, как как с выхода схемы ИЛИ б на схему 11 будет подано разрешение на уменьшение такта интегрирования (в случае, если в результате анализа, хотя бы один из старших триггеров счетчика 2, начиная с пятого, оказался в состоянии 1).Схема запрета 9 работает при этом аналогично схеме запрета 10.С выхода схемы И 5 в блок управления по ступает импульс, формируемый в момент перехода кода счетчика 2 через нуль.Из блока управления 12 в блок вычисленияразности 1 и в частотомер в конце каждого цикла определения разности поступают им.20 пульсы сброса. При использовании оптимизатора расчетный диапазон по производным Д= 106,Предмет изобретения25Оптимизатор режима работы интегрирующего частотомера, содержащий блок вычисления разности, блок памяти и блок управления, отличающийся тем, что, с целью снижеЗО ния требований к быстродействию триггеровсчетчика и упрощения согласования с частотомерами, работающими в коде, отличном отдвоичного, в нем блок памяти снабжен реверсивным регистром сдвига и схемами запрета35 сдвига, а блок вычисления разности - одновходовым реверсивным двоичным счетчиком,с выходами которого связаны входы схем И иИЛИ, выходы которых соединены в блоке памяти через схему управления направлением40 сдвига с входами регистра сдвига и схем запрета сдвига, подключенных к концам регистра,. Устиноваачева Корректоры; С. Сатагулован Е Сапунова оставител Редактор В, фельдм ехред 1 пография, пр. Сапунова, 2 аказ 622/7 Изд.172 Тираж 755 ПодписноеЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР Москва, Ж, Раушская наб., д. 45

СмотретьЗаявка

1658199

Авторы изобретени

Т. В. Донецка Д. Е. Звонков, Ю. В. Ситкин, НТки ИХШ, вительЛенинградский политехнический институт М. И. Калинина

МПК / Метки

МПК: G01R 23/10

Метки: интегрирующего, оптимизатор, работы, режима

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/3-368553-optimizator-rezhima-raboty-integriruyushhego.html" target="_blank" rel="follow" title="База патентов СССР">Оптимизатор режима работы интегрирующего</a>

Предыдущий патент: Автоматический измеритель частоты заполнения

Следующий патент: Фазометр — частотомер

Случайный патент: Поворотно-делительный стол