331392

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 331392

Текст

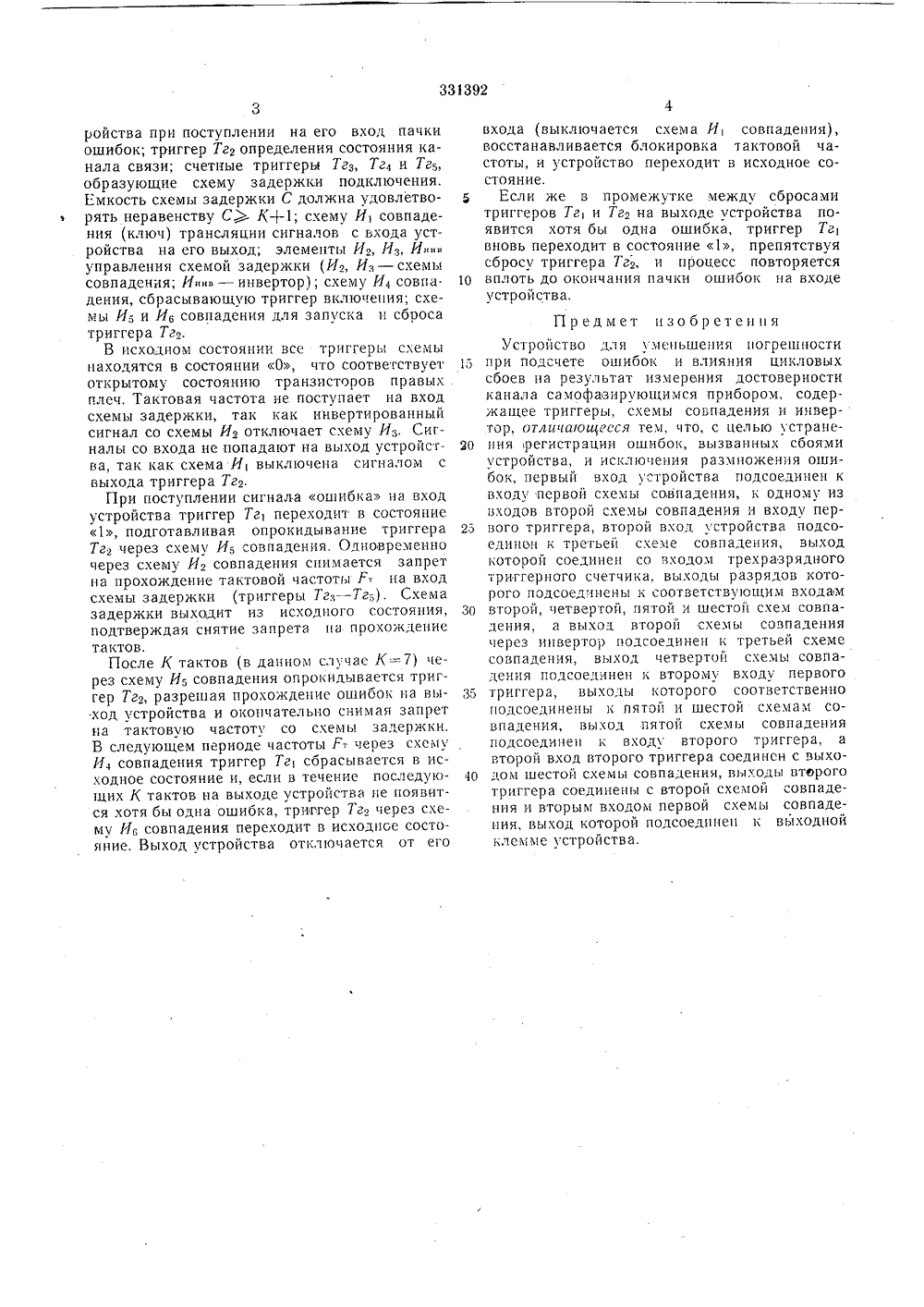

ОПИСАНИЕ 333392ИЗОБРЕТЕН ИЯ Саюз Саветааиа Свциалиатичаааиа РеавтбдяаК АВТОРСНОМУ СВИДЕТЕЛЬСТВУ Зависимое от авт. свидетельства М -Заявлено 10.1 Х.1970 ( 1474429/18-24) М.Кл, 6 06 15/46 с присоединением заявки-1 тветтвт аа двиват ивааратвиий и атирыти 11 ври Саввтв Иииивтрав СССРПриоритет -Опубликовано 07111.192. Бюллетень9Дата опубликования описания 13.17.192 УДК 658,562 (088,8) СГ(;01ЯР ю стЙ Т, 1 : . г 7(" тпиот(тна Б Авторыизобретения М.М,ский и И. А. Лепту явител УСТРОЙСТВО ДЛЯ УМЕНЬШЕНИЯ ПОГРЕШНОСТИ ПРИ ПОДСЧЕТЕ ОШИБОК И ВЛИЯНИЯ ЦИКЛОВЫХ БОЕВ НА РЕЗУЛЬТАТ ИЗМЕРЕНИЯ ДОСТОВЕРНОСТКАНАЛА САМОфАЗИРУ 1 ОЩИМСЯ ПРИБОРОМ иборам измере вязи систем ие т не в состояие в каналерасфазироера рассматривается случай, исследуется реку р рентной ью длиной 2 т - 1 симво: триггер Тг включения устуст- риИзобрете тпе относится к прния достоверности в каналах средачи данных.Известные приборы для измерения достоверности каналов связи можно разделить на две группы: приборы, содержащие эталонный датчик и устройство циклового фазирования, и автоматически фазирующиеся приборы, проверяющие входйую информацию только на рекуррентность.Приборы первой группы требуют при реализации дополнительных затрат для обеспечения уверенности в цикловой синфазности принимаемого и эталонного тест-сигналов.Приборы второй группы значительно проще, но вносят плюсовую погрешность в результате измерения тем большую, чем короче пораженные интервалы.При этом,и те и другие приборьнии отличить ошибки, возникающсвязи от ошибок из-за цикловогования.Цель изобретения - создание устройства, совместная работа которого с прибором второй группы позволяет уменьшить погрешность измерения достоверности, возникающую в результате расфазирования, с одновременным уменьшением смещений оценок.Это достигается тем, что предлагаемое ройство подключает самофазирующийся п бор к счетчику ошибок ровно через К тактов 1 где К - разрядность рагистра рекуррентной последовательности) после появления первой и отключает его не ранее, чем через К тактов 5 после появления последней ошибки пачки.Поэтому ошибки, возникающие на входе самофазирующегося прибора в результате циклового сбоя, не попадают на вход счетчика ошибок, в то время как ошибки, появляющиеся 10 в исследуемом канале, обязательно будут подсчитаны.Это объясняется тем, что ошибки, образующиеся на выходе компаратора самофазирующегося прибора в результате циклового сбоя, 15 вызывают перефазирование прибора, которое. заканчивается не позднее, чем через К тактов,в то время как ошибки, возникающие в канале связи, обязательно появляются на выходе компаратора через К+1 такт. Одновременно уст раняется смещение оценки канала благодаряисключению первых К символов пачки и подсчета К последних, выделяющихся в процессе восстановления цикловой синфазности.На чертеже показана функциональная схема 25 предлагаемого устройства.В качестве примкогда канал связипоследовательностчов30 Схема содержитройства при поступлении на его вход пачки ошибок; триггер Тг 2 определения состояния канала связи; счетные триггеры Тгз, Тг 4 и Тгв, образующие схему задержки подключения. Емкость схемы задержки С должна удовлетво- й рять неравенству С) К+1; схему И 1 совпадения (ключ) трансляции сигналов с входа устрОЙСТВа На ЕГО ВЫХОД; ЭЛЕМЕНТЫ Ио, И, Илвв управления схемой задержки (И., Из - схемы совпадения; И . - инвертор); схему И 4 совпа дения, сбрасывающую триггер включения; схемы И; и И совпадения для запуска и сброса триггера Тг.В исходном состоянии все триггеры схемы находятся в состоянии 0, что соотвегствует 15 открытому состоянию транзисторов правых плеч, Тактовая частота не поступает на вход схемы задержки, так как инвертированный сигнал со схемы И отключает схему Из. Сигналы со входа не попадают на выход устройст ва, так как схема И 1 выключена сигналом с выхода триггера Тг 2.При поступлении сигнала ошибка на вход устройства триггер Тг 1 переходит в состояние 1, подготавливая опрокидывание триггера 25 Тг 2 через схему И, совпадения, Одновременно через схему И 2 совпадения снимается запрет на прохождение тактовой частоты Р на вход схемы задержки (триггеры Тг - Тг-,). Схема задержки выхсдит из исходного состояния, 30 подтверждая снятие запрета па прохождение тактов.После К тактов (в данном случас К=-7) через схему И совпадения опрокидывается триггер Тг 2, разрешая прохождение ошибок па вы ход устройства и окончательно снимая запрет на тактовую частоту со схемы задержки. В следующем периоде частоты Р 1 через схему И 4 совпадения триггер Тг сбрасывается в исходное состояние и, если в течение последую щих К тактов на выходе устройства не появится хотя бы одна ошибка, триггер Тгг через схему Иб совпадения переходит в исходное состояние. Выход устройства отключ ается от его входа (выключается схема И 1 совпадения), восстанавливается блокировка тактовой частоты, и устройство переходит в исходное состояние.Если же в промежутке между сбросами триггеров Тг и Тг на выходе устройства появится хотя бы одна ошибка, триггер Тг 1 вновь переходит в состояние 1, препятствуя сбросу триггера Тг 2, и процесс повторяется вплоть до окончания пачки ошибок на входе устройства,Предмет изобретенияУстройство для уменьшения погрешности при подсчете ошибок и влияния цикловых сбоев на результат измерения достоверности канала самофазирующимся прибором, содержащее триггеры, схемы совпадения и инвертор, отличаощесся тем, что, с целью устранения регистрации ошибок, вызванных сбоями устройства, и исключения размножения ошибок, первый вход устройства подсоединен к входу первой схемы совпадения, к одному из входов второй схемы совпадения и входу первого триггера, второй вход устройства подсоединен к третьей схеме совпадения, выход которой соединен со входом трехразрядного триггерного счетчика, выходы разрядов которого подсоединены к соответствующим входам второй, четвертой, пятой и шестой схем совпадения, а выход второй схемы совпадения через инвертор подсоединен к третьей схеме совпадения, выход четвертой схемы совпадения подсоединен к второму входу первого триггера, выходы которого соответственно подсоединены к пятой и шестой схемам совпадения, выход пятой схемы совпадения подсоединен к входу второго триггера, а второй вход второго триггера соединен с выходом шестой схемы совпадения, выходы второго триггера соединены с второй схемой совпадения и вторым входом первой схемы совпадения, выход которой подсоединен к выходной клемме устройства.оотавятель И. Василенк Текред Л. Евдонов актер И Корректор Е. МихееЬ узо тная типография Костромского управления по печати Заказ 1458 Изд,303ЦНИИПИ Комитета по делам изобретенийМосква, Ж.35, Рауш Тираж 473открытий при Совеая наб., д. 4/5 Подписноинистров ССС

СмотретьЗаявка

1474429

МПК / Метки

МПК: G08C 25/04

Метки: 331392

Опубликовано: 01.01.1972

Код ссылки

<a href="https://patents.su/3-331392-331392.html" target="_blank" rel="follow" title="База патентов СССР">331392</a>

Предыдущий патент: Система автоконтроля закона распределения случайных функций

Следующий патент: Устройство для автоматического контроляопераций

Случайный патент: Экстрагент для извлечения меди