Аналого-цифровой преобразователь; ., ” -хк11нш

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

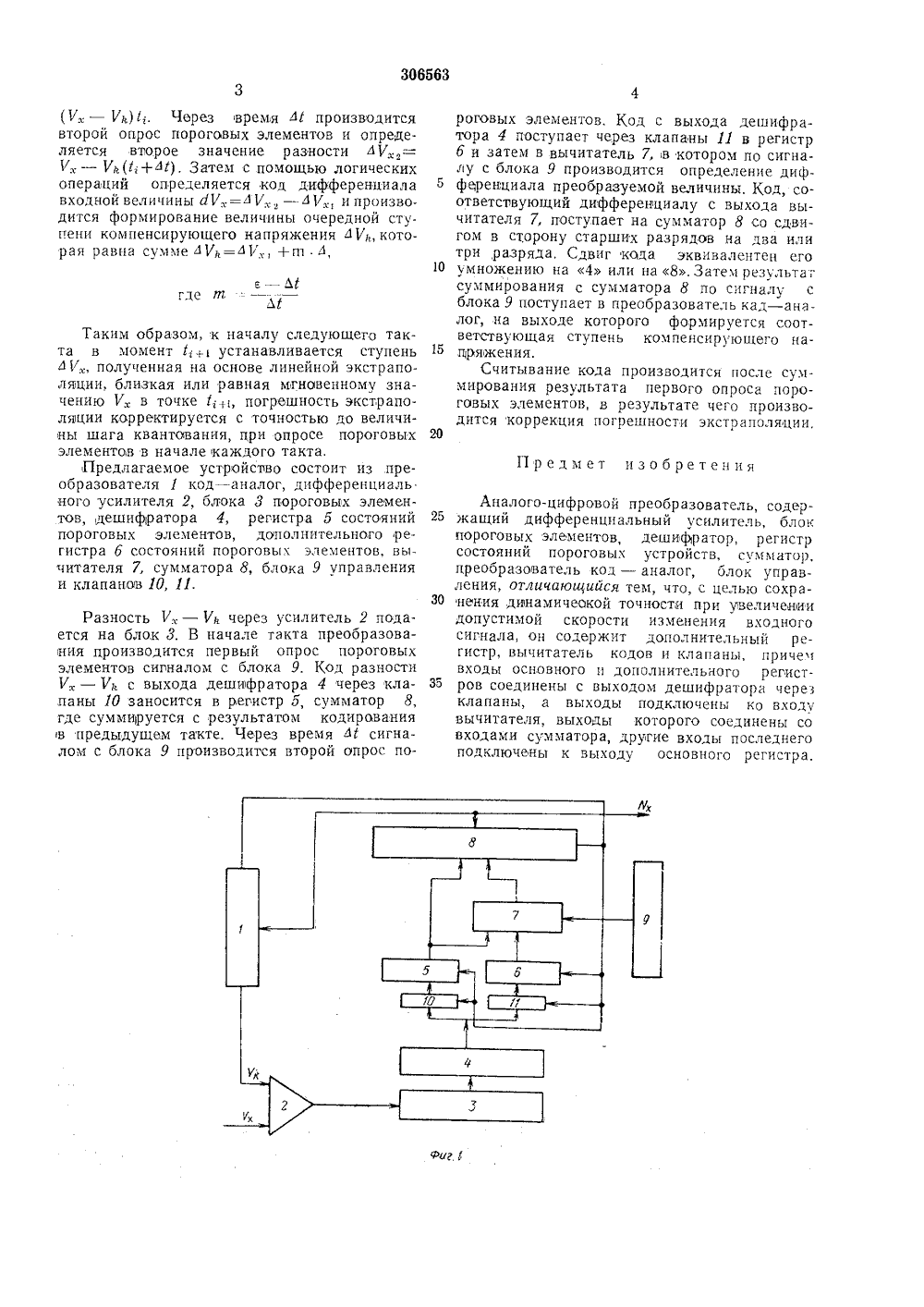

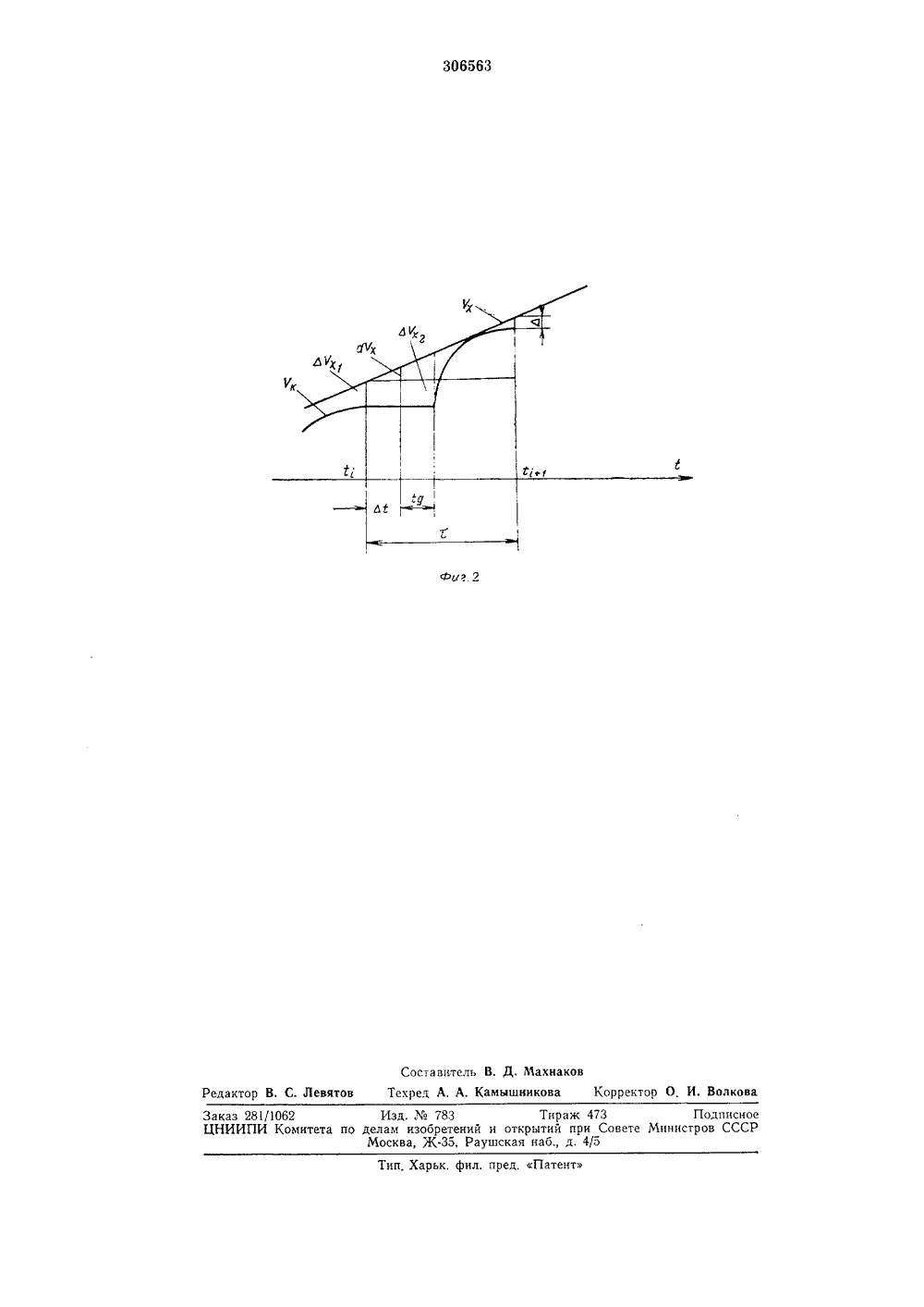

ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 306563 Сова Советскив Социалнстическик РеспубликНомитет по делам иоритет -изобретений н открытии при Совете Министров СССР,П,С ов, К. В, Сафронова, А. Г. Рыжевский, М, П, Шадрин и В. М, Шляндин Заявител Пензенский политехнический институ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЪ ра, ема амИзобретение относится к области вычислительной техники и автоматикиИзвестны аналого-цифровые преобразователи (АЦП), содержащие дифференциальный усилитель, блок пороговых элементов, регистр состояний пороговых устройств, сумматор, преобразователь код в анал, блок управления. В таких преобразователях величина ступени компенсирующего напряжения пропорциональна приращению преобразуемого нацряжения за время такта. Выбор значений порогов срабатывания пороговых элементов и их количество определяет как допустимую скорость /, изменения, так и динамическую погрешность.Все известные АЦП накладывают ограничения на скорость изменения входного сигнала, которые вызваны тем. что компенсация вводится с учетом величины разбаланса в момент опроса. Увеличение скорости (/приводит к существенному увеличению величины разбаланса в момент опроса. Поэтому для уменьшения динамической погрешности необходимо значительно увеличить число, пороговых элементов.Целью изобретения является уменьшение динамической погрешности (увеличение динамической точности) следящих АЦП путем ведения процесса компенсации с учетом скорости изменения входной величины без увеличения числа пороговых элементов и при сохранении такта преобразования.Эта задача решается с помощью двойного опроса состояний пороговых элементов с 5 заданным интервалохт времени, выделениякода дифференциала входного сигнала и соответствующих логических операций, приводящих к тому, что величина ступеней компенсирующего напряжения выдается с таким расчетом, чтобы величина разбаланса в момент опроса была минимально возможной и не накапливалась за время такта. Кроме того, перед выдачей результата преобразования осуществляется коррекция динамической по грешности.,Предложенное устройство отличается отизвестных тем, что содержит дополнительный, регистр, вычитатель кодов и клапаны, причем входы основного и дополнительного регистров 20 соединены с выходом дешифратор а черезклапаны, а,выходы - подключены ко входу вычитателя, выходы которого соединены со входами сумматора, Другие входы сумматора подключены к выходу основного регист 25 На фиг, 1 изображена структурная схустройства; на фиг. 2 - временная диатр ма такта преобразования.В начале такта (момент /т) производитсяопрос состояний пороговых элементов и опре- ЗО деляется первое значение разности лу,=(., - Р) ;. Чврез время Л 1 производится второй опрос пороговых элементов и определяется второе значение разности Л 1= Г,. - "(1;+М). Затем с помощью логических операций определяется код дифференциала входной величины дГ,.=Л Г - А 1 и производится формирование величины очередной ступени компенсирующего напряжения Ъь которая равна сумме 1 Ъ=1) +гп Л,Таким образом, к началу следующего такта в момент 1,+ устанавливается ступень Л 1 полученная на основе линейной экстраполяции, близкая или равная мгновенному значению 1,. в точке 1,+ь погрешность экстраполяции корректируется с точностью до величины шага квантования, при опросе пороговых элементов в начале каждого такта.Предлагаемое устройство состоит из преобразователя 1 код - аналог, дифференциаль ного усилителя 2, блока 8 пороговых элементов, дешифратора 4, регистра 5 состояний пороговых элементов, дополнительного регистра б состояний пороговых элементов, вычитателя 7, сумматора 8, блока 9 управления и клапанов 10, 11. Разность Г -через усилитель 2 подается на блок 8. В начале такта преобразования производится первый опрос пороговых элементов сигналом с блока 9. Код разности Г., - У с выхода дешифратора 4 через кла,паны 10 заносится в регистр 5, сумматор 8, где сумми 1 руется с результатом кодирования в предыдущем такте. Через время 41 сигналом с блока 9 производится второй опрос пороговых элементов. Код с выхода дешифратора 4 поступает через клапаны 11 в регистр б и затем в вычитатель 7, в котором по сигналу с блока 9 производится определение диф ференциала преобразуемой величины, Код, соответствующий дифференциалу с выхода вычитателя 7, поступает на сумматор 8 со сдвигом в сторону старших разрядов на два или три,разряда, Сдвиг кода эквивалентен его 10 умножению на 4 или на 8.Затем результатсуммирования с сумматора 8 по сигналу с блока 9 поступает в преобразователь кад в аналог, на выходе которого формируется соответствующая ступень компенсирующего на гряжени я.Считывание кода производится после суммирования результата первого опроса пороговых элементов, в результате чего производится коррекция погрешности экстраполяции.20 Предмет изобретения Аналого-цифровой преобразователь, содер жащий дифференциальный усилитель, блокпороговых элементов, дешифратор, регистр состояний пороговых устройств, сумматор, преобразователь код - аналог, блок управления, отличающийся тем, что, с целью сохра- ЗО нения дннамичеокой точности при увеличеннидопустимой скорости изменения входного сигнала, он содержит дополнительный регистр, вычитатель кодов и клапаны, причем входы основного и дополнительного регист ров соединены с выходом дешифратора черезклапаны, а выходы подключены ко входу вычитателя, выходы которого соединены со входами сумматора, другие входы последнего подключены к выходу основного регистра.306563 2 ахнак Сост а вите С. Левитов Техред А. А. Камышникова Корректор О. И. Волков акто Тип. Х Ф тент аз 281/1062 Изд, Хо 788 Т ИИПИ Комитета по делам изобретений и открыт Москва, Ж.35, Раушская наж 473 Подписно при Совете Министров ССС д. 4/5

СмотретьЗаявка

1379853

В. П. Сафронов, К. В. Сафронова, А. Г. Рыжевский, М. П. Шадрин, В. М. ндин, Пензенский политехнический институт

МПК / Метки

МПК: H03M 1/48

Метки: аналого-цифровой, хк11нш

Опубликовано: 01.01.1971

Код ссылки

<a href="https://patents.su/3-306563-analogo-cifrovojj-preobrazovatel-khk11nsh.html" target="_blank" rel="follow" title="База патентов СССР">Аналого-цифровой преобразователь; ., ” -хк11нш</a>

Предыдущий патент: Регенеративный ретранслятор для трансляции сигналов дискретной информации по каналамсвязи

Следующий патент: Распределитель импульсов

Случайный патент: Устройство для укладки дренажа из пленки