Устройство для последовательного вьшолнения логических операций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

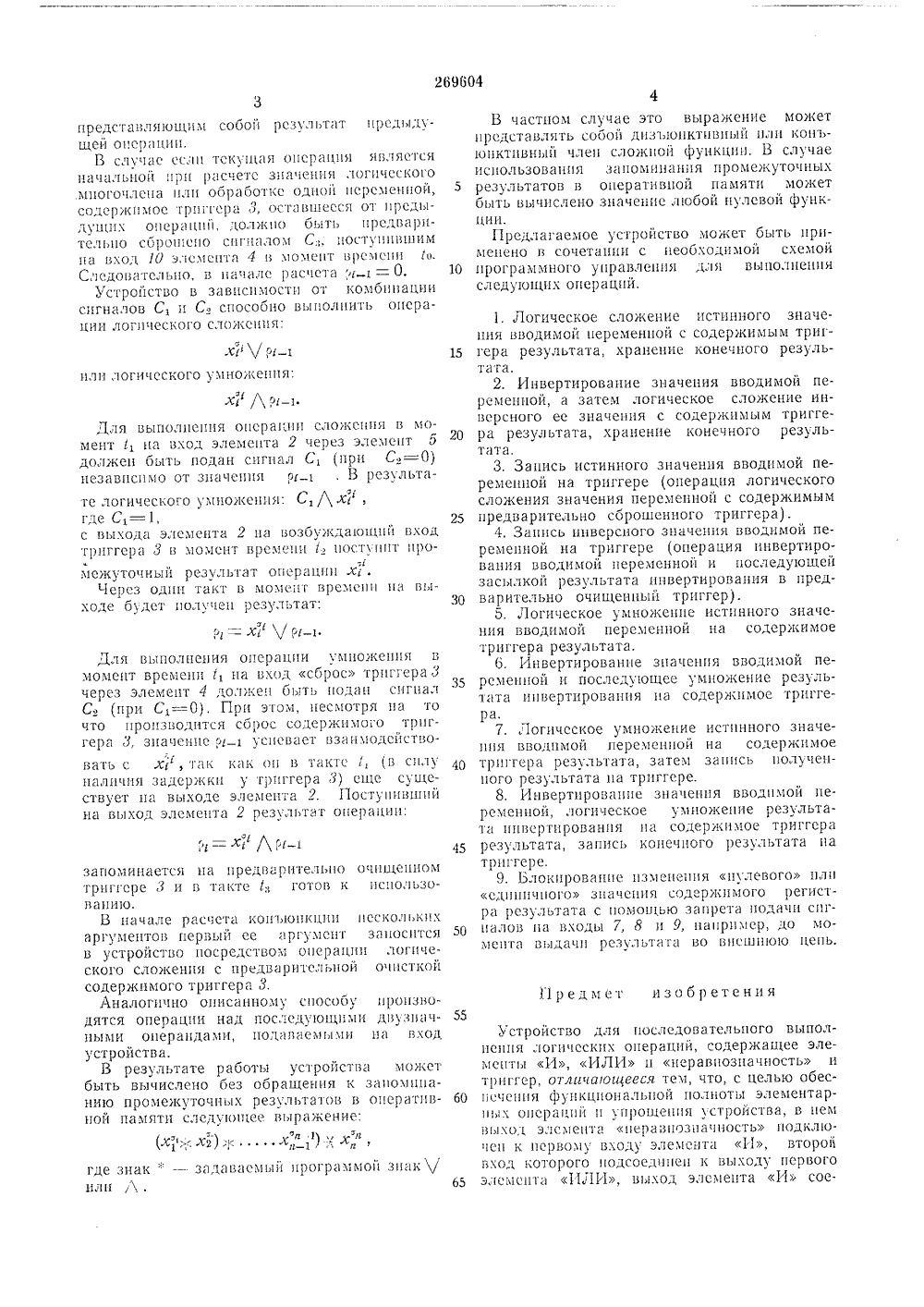

ОПИСАНИЕ ИЗОБРЕТЕ Н М вт Союз Советских Социалистических РеспубликК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ симое от авт, свидетельстваКл. 42 птз, тт 3 1964 ( 925013 тт 18-24) влец с присоедицением заявки1 Пх 6 06 7/3 Комитет по делам обретений и открытий ри Совете тйинистров ССОРриоритет публиков УДК 681,325 6.(088,8 члетень15 я 3 Л 1.1970 17.1 У,1970, Бто Дата опубликования описан Авторизобретени М, Юнчи Научно-исслед вычательскии институт управляющихслительных машин аявител СТРОЙСТВО ДЛЯ ПОСЛЕДОВАТЕЛЬНОЕ ВЫПОЛНЕНИЯ ЛОГИЧЕСКИХ ОПЕРАЦИ ного сцгттл.тл сброс тттхол лля входтот ве,ч 111111Устройство вылцецологттческцх элемсцтлх У.5задержкой в олин такт,па лттолцой сбокц Бподается зцлчсцце вхв то кс вемя пл вход 7пцогрлхтмпьтй сцгпллВ хтомсцт т цл гыхо теГЯ ттСЗ 1 ЬТЛТ тт 11 ГСРТ.РОВрованя): ггсл ты р. ттл т 2 т Я, точтс цт стцтхронцт.тхобладаюних элевтетттлх тцттл вход б ВЕЛтттттттттт Х 1 лпоступает ровать" С .об 1 з ет тц теттттвепттто:тт оц элехсцт ц т т тт Е 11 Т 11 элемент ;итти т 11 де -., - условотсутствия зна 15 ил будет: результат с. х; 7. ХНа чертетсе предс емого устройства, гд значность; 2 - эле ческий триггер; 4 и б вход для входной ве граммцого сигнала 8 - вход для прогр жить С,; 9 - вход лл умножить С,инфор- обра- правлядующие любом взлцмоера 3,ерепаботкл входнот" СХОЛЦтЬ РЛЗЛттттцттхот тсомбпнлццп тутающих нл после ты устройства. В емля ттелцчццл х, жимым рттригг тецщем п жет прот цсцмости ллоц, ос с элс и ст 11 лб ты ил с солерВ дллы.маццц мозом в злвемых сттгтЛОГ 11 ттСС 1; Цслучае обдействх ет Изобретение относится к области вычислительной техники.Известны устройства для последовательного выполнения арифметических операций, содержатцие логические элементы И, ИЛИ НЕ, триггеры и устройство управления. Однако известные устройства вьтполттяют только арифметические операции.Предлагаемое устройство отличается тем, что в нем выход элемента неравнозцачттость подключен к первому входу элемента И. второй вход которого подсоединен к выходу первого элемента ИЛИ, выход элемента И соединен с возбуклатощим вхолом триггера, вход установка нуля которого подключен к выходу второго элемента ИЛИ, а выход триггера подсоединен к одному пз входов первого элемента ИЛИ.Это позволяет обеспечить функционально полноту операций и упростить устройство,тавлена схема предлагае 1 - элемент неравно- тент И; т - динами - элементы ИЛИ; б - личины х; 7 - вход проинвертировать С ; аммпого сигнала слодля программного сигца - вход для програмое обозначение цллпчсл отрицания.е уклзлцттого лействпях; если С, = 0 цлипредсталяющцм собой результат црсдьдущей оцсицип.В случ 1 с ссгп текцдя Оцсряцц 51 5 ц)ляс 1 с 51 начальной црц расчете значения лоп)чсского мцогочлсца )ьш обработке одной цсрсмеццой, содсрткпмос трп 1 Гсрд ), ОС 1 двшесс 51 От црсдь)- ду)ццх опер)цп)1, дол)кцо быть црсдярцтсльцо сброшено сппгалом С;остуццшим цд вход 10 элсмсцтя 4 момент врсмсцц Ь.Следовательно, в цачялс рас)ста; 1= О, 10Устройство в зависимости от комбинации сигналов С, и С. способно выполнить опера- ЦИИ ЛОГИЕСКОГО СЛОКСЦЦЯ.15цли логического умножения:1 л/- 1Для выполпсцпя Опсрацпи сложсцц 51 в момент 1, ца вход элемента 2 через элемент 5г 20должен быть подан сигнал С, (при С -- 0)независимо от зцачсцця рг. В результате логического умножения: С, / ХР,где С,=1,25с выхода элемента 2 ца возбуждающий входтриггера 3 в момент рсмс)ш Ь постуИп промежуточный результат операции х; .Через один такт в момсцг врсмсш ца ыходе б) дст получен результат: 30Р 1: Х) Рг - 1(ля выполнения операции умножения в момент времениИа вход сброс триггера 3 через элемент 4 должен Оыть подан сигнал35 С (при С,=О). При этом, несмотря ца то что производится сброс содержимого триггера 3, зцачснцс р) 1 успевает взяцмодсйствогать с Х 1, тдк кяк Оц в такте, (в силу 40 наличия задержки у тршггера 3) еще существует пд выходе элемента 2. Постушгвшцй ца выход элемента 2 результат операции:запоминается ца предварительно Очищенном триггере 3 и в тактеготов к использованию.В начале расчета коцъ)оцкццц нескольких аргументов первый ее аргумент заносится 50 в устройство посредством операции логического сложения с предварительной очисткой содержимого триггера 3.Лналоги ц)о описанному способу произодятся операции над последующими дузцч ными Операндами, цодяяемыми цд ход устройства.В результате работы устройства может быть вычислено без обращения к запоминанию промежуточш,х результатов в опсратцв- б 0 цой памяти следуюцее выражение(Х"хХ 2):,-Х,) ", Х где знак " - задаваемый программой зцяк/ или 65 В частном случае это выражение может представлять собой дизьюцктцвцый илц коньюцктивный члсц сложной функции. Б случае исцользоваш)я зИощшдиия промежуточных результатов в оперативной памяти может быть вычислено значешс любой нулевой функции.Предлагаемое устройство может быть применено в сочетании с необходимой схемой программного уцравлсшгя для выполнения следу)ощих операций.1. Логическое сложение истшшого значения вводимой переменной с содержимым триггера результата, хранение конечного результата.2. Инвертирование значения вводимой переменной, а затем логическое сложение инверсного ее значения с содержимым триггера результата, хранение конечного результата.3. Запись истинного значения вводимой переменной на триггере (операция логического сложения значения переменной с содержимым предварительно сброшенного триггера).4. Запись инверсного значения вводимой переменной ца триггере (операция инвертирования вводимой переменной и последующей засылкой результата инвертирования в предварительно очищенньш триггер).5, Логическое умножение истинного значения вводимой переменной на содержимое триггера результата.6. Инвертирование значения вводимой переменной и последу)ощее умножение результата инвертирования ца содержимое триггера,7. Логическое умножение истинного значения вводимой переменной на содержимое триггера результата, затем запись полученного результата ца триггере.8. Ицвертироваше значения вводимой переменной, логическое умножение результата ицвсртированпя ца содержимое триггера результата, запись конечного результата па триггере,9. Ьлокцровацце измене )ця пулевого плц единичного значения содержимого реп)стра результата с помощью запрета цодяц сигналов ца входы 7, 3 и 9, например, до момента выдачи результата во внешнюю цепь,11 редмет изобретенияУстройство для последовательного выполнения логических операций, содержащее элементы И, ИЛИ и неравнозначность и триггер, отлича)ощееся тем, что, с целью обеспечения функциональной полноты элементарных операций и упрощения стройства, в цем ыход элемента церав)юзцачцость подключен к первому входу элемента И, второй вход которого подсоединен к выходу первого элемента ИЛИ, выход элемента И сое269604 Составитель А, А, ПлащииТскрсл Т. П. Курилко Корректор С. Ч. Сигал 1 с,тиор 3. Громова Заказ 2087,17 Тираж 480 11 оаиисицс 111 ИИ 1 И Коцитсга ио;слам изойрстсии и окргии ири Сов с Мииитр в ССС 1 Москва, Ж, Раугискаи ио., л. 4,5 Тииогра 1)ии, и 1. Савинова, 2 дннен с возбужаоним вхолом трнггера, вход установка нуля которого нодкгночен к в- ходу второго элемента ИЛИ, а выход трнггер; ноЛсоедннен к оЛном; нв вхЛов ервогоэлеменп а 11 ЛИ,

СмотретьЗаявка

925013

А. М. Юнчик, Научно исследовательский институт управл ющих вычислительных машин

МПК / Метки

МПК: G06F 7/00

Метки: вьшолнения, логических, операций, последовательного

Опубликовано: 01.01.1970

Код ссылки

<a href="https://patents.su/3-269604-ustrojjstvo-dlya-posledovatelnogo-vsholneniya-logicheskikh-operacijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для последовательного вьшолнения логических операций</a>

Предыдущий патент: Устройство для возведения в квадр. м чис-ла, представленного в унитарнол коде

Следующий патент: Устройство для устранения неоднозначности

Случайный патент: Ручная сажалка