Устройство для микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

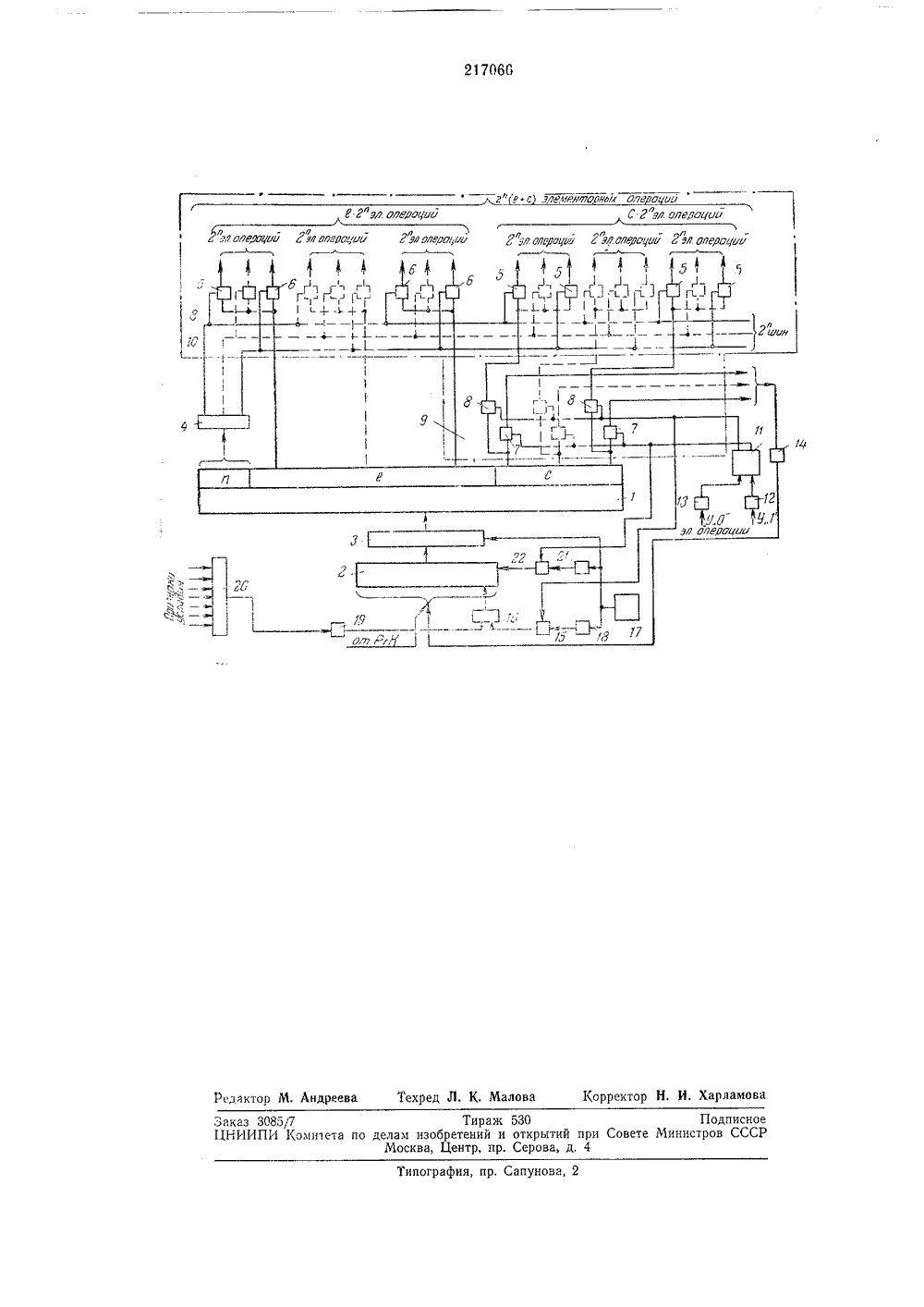

ОПИСАН ИИЗОБРЕТЕНИЯ Саюа Советских Социалистических Республиквисимое от авт. свидетельства111,1967 ( 1142914/26 аявле трисоединением заявкиПриоритетОпубликовано 26.17,1968. БюллетеньДата опубликования описания 18.Х,19 б 8 Комитет по делам изобретений и открыт при Совете кчинистро СССРАвторыизобретени Овсепян и П, А. Сагателя вител УСЛРОЙС 1 ВО ДЛЯ М Известны устройства для микропрограммного управления, содержащие запоминающие устройства, генератор тактовых импульсов, регистры, дешифраторы, блок распределения элементарных операций, блок переключения, вентили, задержки и триггеры.В предлагаемом устройстве генератор тактовых импульсов соединен с управляющим входом дешифратора и через задержки и вентили, управляющие входы которых подключены соответственно к нулевому и единичному выходам триггера управления, с регистром адреса запоминающего устройства. Входы регистра адреса запоминающего устройства подсоединены через вентили к выходам регистра команд и через другие вентили, управляющие входы которых соединены с триггером управления, к С выходам разрядов запоминающего устройства, другие п выходов запоминающего устройства подключены ко входу дешифратора.Каждый выход последнего подсоединен ко входам (1+с) вентилей, другие входы (1+с) вентилей соединены с 1-выходами запоминающего устройства и с с-вентилями блока переключения, управляющие входы которых подключены к выходу триггера управления. При таком выполнении устройства сокр ается его разрядность, уменьшается обь РОГРАММНОГО УПРАВЛЕН запоминающего устройства и объем микропрограммНа чертеже приведена функциональная схема предлагаемого устройства.В устройство входят следующие узлы.Запоминающее устройство 1, предназначенное для хранения и выдачи микрокоманд и связанное по входу с регистром адреса 2 (РгАЗУ) через дешифратор 3, а по выходу в 10 зависимости от разрядов.Так, по разрядам и с дсшифратором 4, навыходе которого образуются шины выбора элементарных операций в количестве 2", соединенные с клапанами 5 и 6 блока распреде ления элементарных операций; по разрядам 1со вторыми входами 1 2" клапанов 5 блока распределения, а по разрядам С с клапанами 7, 8 блока переключения 9.Блок переключения 9, служащий для засыл ки с разрядного кода либо в РгЛЗУ 2, либо вблок распределения 10 элементарных операций и связанный с входами РгЛЗУ по клапанам 7 и с клапанами 5 блока распределения по клапанам 8. Клапаны 7 и 8 по входам так же связаны с триггером 11, разрешающим засылку кода либо в (РгАЗУ) 2, либо в блок распределения. По входу триггер 11 через элементы задержки 12 н 13 управляется в соответствии с поступающей двоичной инфор м а циеи.Блок распределения элементарных операций, предназначенный для образования 2" (1+с) элементарных операций и связанный по входам клапанов 5 и б с выходами дешифратора 4 и с запоминающим устройством, а по выходам с различными устройствами цифровой вычислительной машины.Регистр 2 (РгАЗУ), служащий для приема и хранения текущего адреса микрокоманды и имеющий возможность принимать коды с регистра команд, являющиеся начальными адресами микропрограммы, а также с выхода клапана 7 переключения через элементы задержки 14 в зависимости от состояния триггера 11, Через клапан 15 и сборку 1 б адрес текущей микрокоманды в регистре (РгАЗУ) может быть изменен на единицу. В зависимости от состояния триггера 11 клапан 15 либо разрешает прохождение импульса, поступающего от генератора 17 через элемент задержки 18, либо запрещает,На сборку 1 б от элемента задержки 19 через сборку 20 поступают сигналы признаков условий.Предлагаемое устройство работает следующим образом. Сигналы на выходе генератора 17 используются как сигналы считывания с запоминающего устройства. Импульсы с генератора после определенной задержки на элементах 18 и 21 опрашивают клапаны 15 и 22 либо для прибавления единицы к содержимому (РгАЗУ), либо для установки его на нуль (в зависимости от состояния триггера 11), В регистр 2 из регистра команды (не показанного на чертеже) передается адрес первой микро- команды. С приходом очередного импульса чтения с запоминающего устройства считывается первая микрокоманда.Первоначальное состояние триггера 11 обеспечивает последовательную выборку микро- команд. Считанный по разряду и код через дешифратор 4 выбирает соответствующую шину элементарных операций, Коды с разрядов 1 и с поступают на входы всех клапанов 5 и б. Из них срабатывают те клапаны, на вторых входах которых имеется разрешение от выбранной шины.Задержанный импульс с выхода элемента задержки 18 изменяет содержимое (РгАЗУ) на +1. Следующий импульс генератора вызывает чтение микрокоманд по новому адресу.При безусловном переходе по произвольному адресу микрокоманды в предыдущем такте меняется состояние триггера 11 с помощью соответствующей элементарной операции через элемент задержки 12. В следующем такте количество разрядов микрокоманды, отведенное для элементарных операций, уменьшается до 10 1 разрядов, а разряды с передаются в заранееочищенный через элемент задержки 21 и клапан 22 (РгЛЗУ), образуя адрес следующей микроком анды,Условные переходы реализуются увеличени ем адреса микрокоманды на единицу черезсборку 20 и элемент задержки 19 при наличии соответствующего признака выполнения условия.20Предмет изобретенияУстройство для микропрограммного управления, содержащее запоминающее устройство, генератор тактовых импульсов, регистры, де шифраторы, блок распределения элементарных операций, блок переключения, вентили, задержки и триггеры, отличающееся тем, что, с целью сокращения разрядности устройства, уменьшения объема запоминающего устрой ства и микропрограмм, в нем генератор тактовых импульсов соединен с управляющим входом дешифратора и через задержки и вентили, управляющие входы которых подключены соответственно к нулевому и единичному выходам триггера управления, с регистром адреса запоминающего устройства, входы регистра адреса запоминающего устройства подсоединены через вентили к выходам регистра команд и через другие вентили, управляющие 40 входы которых соединены с триггером управления, к с выходам разрядов запоминающего устройства, другие п выходов запоминающего устройства подключены ко входу дешифратора, каждый выход которого подсоединен ко 45 входам (1+с) вентилей, другие входы (1+с)вентилей соединены с 1-выходами запоминающего устройства и с с вентилями блока переключения, управляющие входы которых подключены к выходу триггера управления,.аказЦНИИ 5/7И Коми ра,оо 3 мвперааоо 2 ь щщауи 2 ияперал 7 ои 2 м аперооо хред Л. К. Малова Корректор Н. И, Харламова Тираж 530 Поди испоа по делам изобретений и открытий при Совете Министров СССМосква, Центр, пр. Серова, д, 4

СмотретьЗаявка

1142914

Г. Е. Овсеп, П. А. Сагател

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 01.01.1968

Код ссылки

<a href="https://patents.su/3-217066-ustrojjstvo-dlya-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для микропрограммного управления</a>

Предыдущий патент: Устройство для определения среднего значения статистического распределения

Следующий патент: Устройство для обработки результатов исследований объектов

Случайный патент: Пособ получения бис-(хелат)-диалкоксититанов