Помехоустойчивый способ измерения аналоговых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1472833

Авторы: Федоров, Человечков

Текст

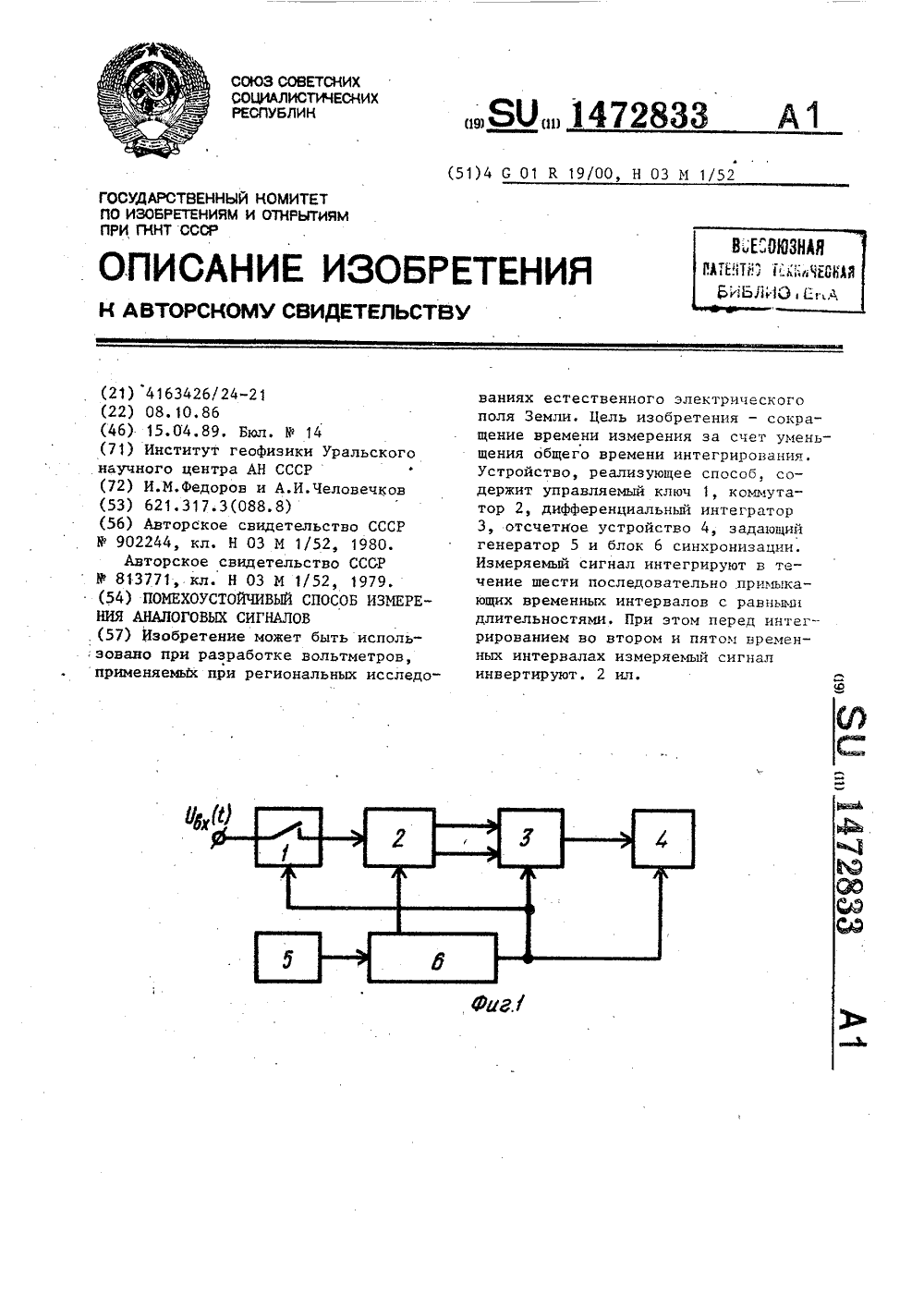

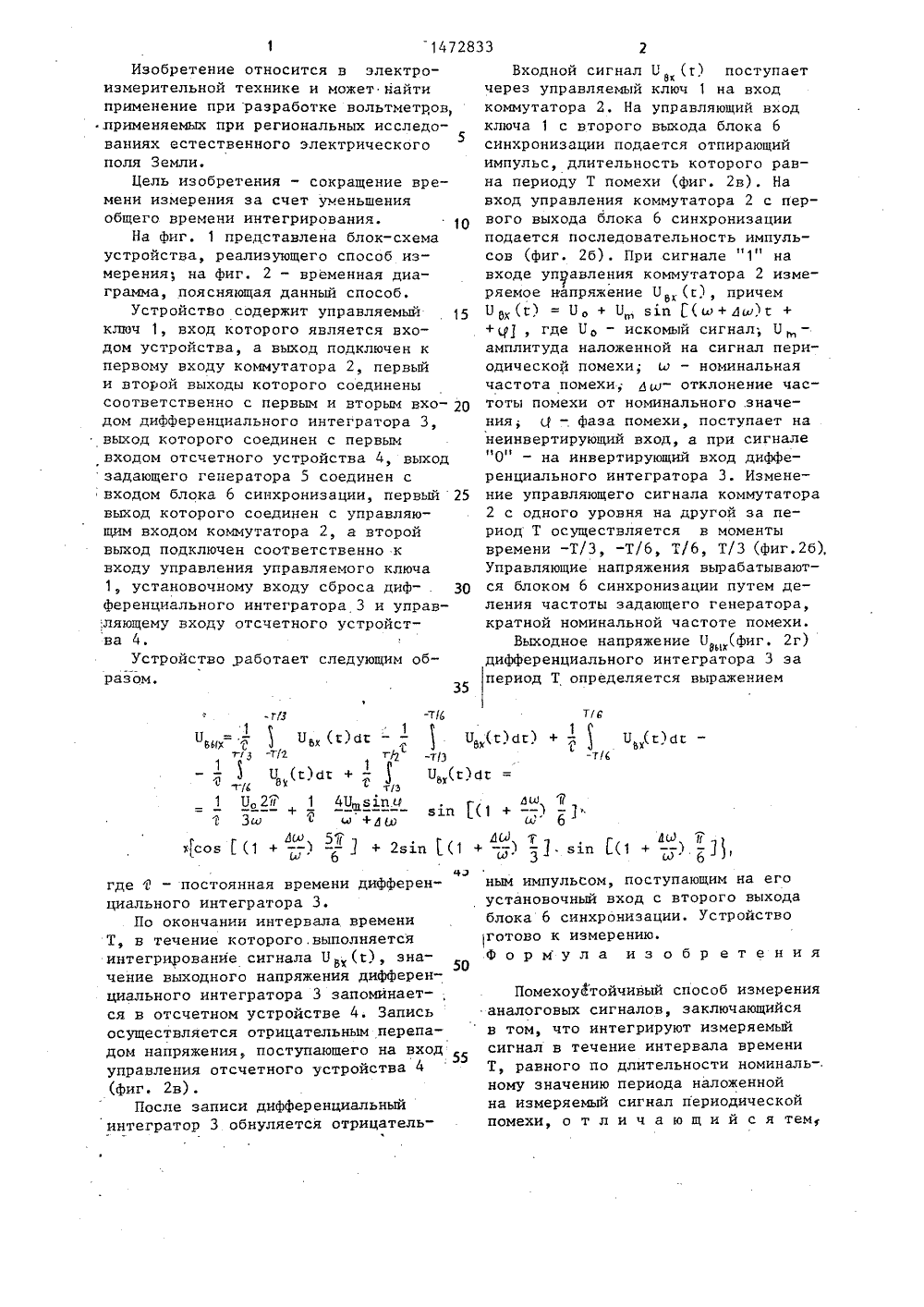

ТСНИХТИЧЕСКИХ СОЮЗ СОВСОЦИАЛРЕСПУ 6 А 1 09) 3 М 1/52 14 СО 9 0 ОПИСАНИЕ ИЗОБРЕТЕН ИДЕТЕЛЬСТВ ВТОРСНОМ ского СССР80.СР79.ИЗМЕР спольтров,исследо, Фиг,ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБ ЕТЕНИЯМ И ОЩРЫТИПРИ ГКНТ СССР(71) Институт геофизики Уралнаучного центра АН СССР(54) ПОМЕХОУСТОЙЧИВЫЙ СПОСОБНИЯ АНАЛОГОВЫХ СИГНАЛОВ.(57) Изобретение может быть и:зовано при разработке вольтмприменяемых при региональных ваниях естественного электрического поля Земли. Цель изобретения - сокращение времени измерения за счет умень- щения общего времени интегрирования. Устройство, реализующее способ, содержит управляемый ключ 1, коммутатор 2, дифференциальный интегратор 3, отсчетное устройство 4, задающий генератор 5 и блок 6 синхронизации. Измеряемый сигнал интегрируют в течение шести последовательно .примыкающих временных интервалов с равными длительностями. При этом перед интегрированием во втором и пятом временных интервалах измеряемый сигнал инвертируют, 2 ил.ЯИзобретение относится в электро- измерительной технике и может найти применение при разработке вольтметров, лрименяемых при региональных исследованиях естественного электрического5 поля Земли.Цель изобретения - сокращение времени измерения за счет уменьшения общего времени интегрирования. 10На фиг. 1 представлена блок-схема устройства, реализующего способ измерения; на фиг. 2 - временная диаграмма, поясняющая данный способ.Устройство содержит управляемый 15 ключ 1, вход которого является входом устройства, а выход подключен к первому входу коммутатора 2, первый и второй выходы которого соединены соответственно с первым и вторым вхо дом дифференциального интегратора 3, выход которого соединен с первым входом отсчетного устройства 4, выходзадающего генератора 5 соединен с входом блока 6 синхронизации, первый 25 выход которого соединен с управляющим входом коммутатора 2, а второй выход подключен соответственно к входу управления управляемого ключа 1, установочному входу сброса диф Ференциального интегратора 3 и управ;ляющему входу отсчетного устройства 4.Устройство работает следующим образом. 1472833 2Входной сигнал Ц (г) поступаетчерез управляемый ключ 1 на входкоммутатора 2. На управляющий входключа 1 с второго выхода блока 6синхронизации подается отпирающийимпульс, длительность которого равна периоду Т помехи (фиг. 2 в). Навход управления коммутатора 2 с первого выхода блока 6 синхронизацииподается последовательность импульсов (фиг. 2 б). При сигнале "1" навходе уп 7 павления коммутатора 2 измеряемое напряжение О 8,(г 1, причемБ 8 х(г) = Оо + Б з 1.п Г(г+Лги)г ++ г, где Бх - искомый сигнал;амплитуда наложенной на сигнал периодической помехи; ь - номинальнаячастота помехи; ди- отклонение частоты помехи от номинального .значения; г 1 - Фаза помехи, поступает нанеинвертирующий вход, а при сигнале"0 - на инвертирующий вход дифференциального интегратора 3. Изменение управляющего сигнала коммутатора2 с одного уровня на другой за период Т осуществляется в моментывремени -Т/3, -Т/6, Т/6, Т/3 (фиг.2 б),Управляющие напряжения вырабатываются блоком 6 синхронизации путем деления частоты задающего генератора,кратной номинальной частоте помехи.Выходное напряжение О (фиг. 2 г)дифференциального интегратора 3 эапериод Т определяется выражением+ жЯ,вп (1 + - ,)3+1 г 6ф 57 АИихсоз Г (1 + - ) - 3 + 2 здп Г(1 + - 1 -з 2 п Г(1 + - ) - 3с б д 3 д 6ЧЭгде Г - постоянная времени дифферен- ным импульсом, поступающим на егоиального интегратора 3. установочный вход с второго выходаПо окончании интервала времени блока б синхронизации. Устройство Т, в течение которого. выполняется готово к измерению. интегрирование сигнала П (г 1 зна- Ф о р м у л а и з о б р е т е н и я8 х .фчение выходного напряжения дифференциального интегратора 3 запоминает-, ПомехоуЕтойчивый способ измеренияч ся в отсчетном устройстве 4Запись аналоговых сигналов, заключающиися осуществляется отрицательным перепа- в том, что интегрируют измеряемыи дом напряжения, поступающего на вход сигнал в течение интервала времени, 55управления отсчетного устройства 4 Т, равного по длительности номиналь(фиг. 2 в). ному значению периода наложеннойПосле записи дифференциальный на измеряемый сигнал периодическойн интегратор 3 обнуляется отрицатель- помехи, о т л и ч а ю щ и и с я тем472833 Составитель А.Комиссароведактор О.Спесивых Техред М.дидык Корректор М,Максимишине Тираж 711твенного комитета по изобретениям113035, Москва, Ж, Раушская на аказ 1704/4 НИИПИ Госуд одписно КНТ СССР открытиям и, д. 4/5 Производственно-издательский комбинат "Патент", г. Ужгор Гагарина, 1 О з 1 что, с целью сокращения времени измерения, интегрирование измеряемого сигнала осуществляют в течение шести последовательных примыкающих временных интервалов с равными длительностями, причем перед интегрированиемво втором и пятом временных интервалах измеряемый сигнал инвертируют.

СмотретьЗаявка

4163426, 08.10.1986

ИНСТИТУТ ГЕОФИЗИКИ УРАЛЬСКОГО НАУЧНОГО ЦЕНТРА АН СССР

ФЕДОРОВ ИГОРЬ МИХАЙЛОВИЧ, ЧЕЛОВЕЧКОВ АЛЕКСАНДР ИВАНОВИЧ

МПК / Метки

МПК: G01R 19/00, H03M 1/52

Метки: аналоговых, помехоустойчивый, сигналов

Опубликовано: 15.04.1989

Код ссылки

<a href="https://patents.su/3-1472833-pomekhoustojjchivyjj-sposob-izmereniya-analogovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Помехоустойчивый способ измерения аналоговых сигналов</a>

Предыдущий патент: Трансформаторный мост переменного тока

Следующий патент: Преобразователь напряжение ток

Случайный патент: Торцовое уплотнение