Устройство для формирования сигналов прерывания при отладке программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1405061

Авторы: Богданова, Будовский, Бурковский

Текст

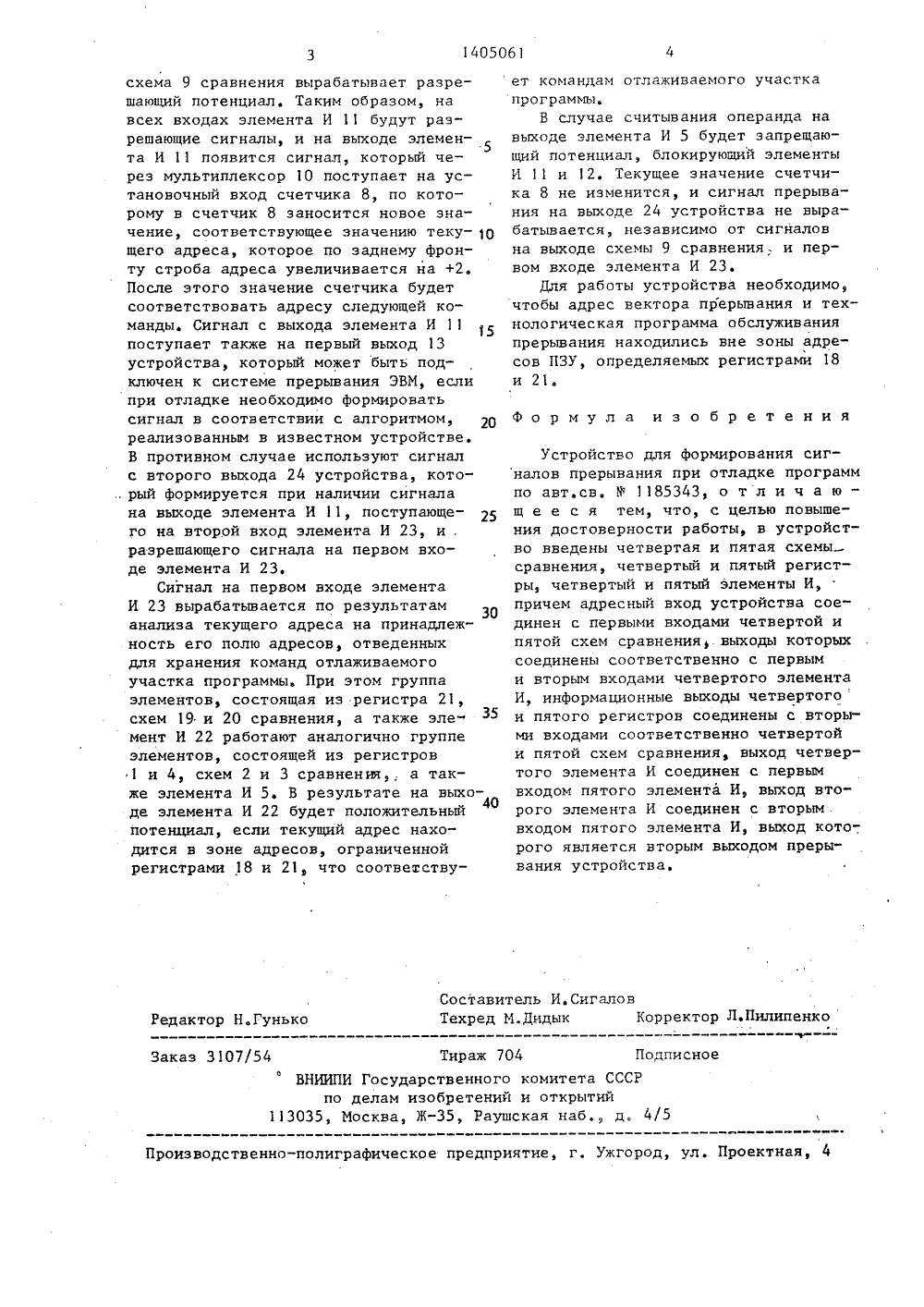

ОЮЗ СОВЕТСНИХ ОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 1191 (11) 05061.И 4 ОСУДАРСТНЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ ЕТЕ Н АВТОРСНОМУ СВИ ЕПЬСТВ/24-2 Бюл.ский, Бурковс ов тельство СССР Р 11/28, 1985 ое свидл.ОО(54) УС СИГНАЛО ГРАММ (57) Из вой выч начено програм ОИСТВО ДЛЯ ФОРМИРОВАНИЯПРЕРЫВАНИЯ ПРИ ОТЛАДКЕ ПРО ретен слителдля ис ои техни ьзования изирован е(6 ) 1185343 (21) 4162765 (22) 15.128 (46) 23.06.8 (72) Я,М,Буд и К.В,Богдан (53) 681.3(0 (56) Авторск У 1185343, к относится к цифроке и предназпри отладке ных вычисли тельных систем реального времени.Цель изобретения - повышение досто"верности работы устройства, Цель достигается тем, что в устройство, содержащее первый 1, второй 4, третий6 регистры, первую 2, вторую 3 итретью 9 схемы сравнения, первый 5,второй 11 и третий 12 элементы И,счетчик 8, мультиплексор адреса 7,введены четвертый 18 и пятый 21 регистры, четвертая 19 и пятая 20 схемы сравнения, четвертый 22 и пятый23 элементы И. За счет введения новых элементов и их связей обеспечивается получение более достовернойинформации о переходах на выбранномучастке отлаживаемой программы. 1 ил,Изобретение относится к вычислительной технике, может быть использовано при отладке программ специализированных цифровых вычислительныхсистем (СЦВС) реального времени и является усовершенствованием устройства по авт.св. Р 1185343.Целью изобретения является повышение достоверности работы устройства за счет запрета формированиясигнала прерывания при возврате в от. - ,лаживаемый участок программы черезего нижнюю границу.На чертеже представлена структурная схема устройства.Устройство содержит первый регистр1, первую 2 и вторую 3 схемы сравнения, второй регистр 4, первый элементИ 5, третий регистр 6, мультиплексор,7 адреса, счетчик 8, третью схему 9сравнения, мультиплексор 10 сигналазаписи, второй 11 и третий 12 элементы И, первый выход 13 прерывания устройства, адресные входы 14 устройст-. 25ва, вход 15 строба адреса, вход 16начальной установки устройства, вход17 установки режима, четвертый регистр 18, четвертую 19 и пятую 20схемы сравнения, пятый регистр 21, 30четвертый 22 и пятый 23 элементы И,второй выход 24 прерывания устройства,Рассмотрим работу устройства совместно с отлаживаемой СЦВС, построен-ной на базе ЭВМ типа Электроника.Адресные входы 14 устройства подключены к магистрали микро-ЭВМ, ккоторой подключены также постоянноезапоминающее устройство (ПЗУ) для 40хранения команд и оперативное запоминающее устройство. (ОЗУ) для храненияоперандов программ (не показаны).ОЗУ и ЙЗУ имеют различные адреса ведином адресном пространстве магистрали микро-ЭВМ,Работа устройства начинается сустановки на регистрах 1 и 4 верхнейи нижней границ области памяти, отведенной для хранения команд, нарегистре б - начального адреса отлаживаемой программы, а на регистрах18 и 21 - верхней и нижней границобласти памяти, отведенной для хранения команд отлаживаемого участка программы. В простейшем случае регистры1, 4 и б выполняются в виде тумблерных наборников на лицевой панели устройства,С входа 17 устройства на управляющие входы мультиплексоров 7 и 10 поступает управляющий потенциал, соответствующий вводу начального адресас регистра б через мультиплексор 7 всчетчик 8 под управлением сигнала,поступающего с входа 16 устройствачерез мультиплексор 10 на установоч-,ный вход счетчика 8.Управляющие сигналы на входы 16 и17 подаются с лицевой панели устройства.После занесения начального адресапрограммы в счетчик 8 изменениемуправляющего потенциала на входе 17устройства информационные входы счетчика 8 через мультиплексор 7 подключаются к адресным входам 14 устройства, а установочный вход - через мультиплексор 10 к выходу второго элемента И 11.После запуска программы при появлении на. входах 14 устройства кодаадреса в сопровождении строба адресана входе 15 производится его анализна принадлежность полю адресов ПЗУ,т.е. определяется, считывается ли вданный момент команда или операнд.Текущий адрес с входов 14 устройства поступает на первые входы схем2 и 3 сравнения, На выходе схемы 2сравнения присутствует положительныйпотенциал, если текущий адрес меньшеадреса верхней границы, установленногона регистре 1, а на выходе схемы Усравнения - если больше адреса нижней границы, зафиксированного в регистре 4. На выходе элемента 5 И будетположительный потенциал, если текущий адрес находится в зоне адресов,ограниченной регистрами 1 и 4, чтосоответствует считыванию команды.Одновременно с этим текущий адрес сравнивается с содержимым счетчика 8. В случае равенства этих значений с выхода схемы 9 сравнения натретий вход элемента И 11 поступаетзапрещающий потенциал, блокирующийпоявление сигнала на его выходе. Приэтом по заднему фронту строба адреса с входа 15 устройства через элемент И 12 сигнал поступает на счетный вход счетчика 8 и увеличивает егосодержимое на +2 (для ЭВМ Электроника-бО),В случае несовпадения текущего адреса на первых входах схемы 9 сравнения с текущим содержимым счетчика 814050 б 1 Формула изобретения Составитель И.СигаловТехред М.Дидык Корректор Л.ПилипенкоРедактор Н.Гунько Заказ 3107/54 Тираж 704 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д, 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 схема 9 сравнения вырабатывает разрешающий потенциал, Таким образом, навсех входах элемента И 11 будут разрешающие сигналы, и на выходе элемента И 11 появится сигнал, который через мультиплексор 1 О поступает на установочный вход счетчика 8, по которому в счетчик 8 заносится новое значение, соответствующее значению текущего адреса, которое по заднему фронту строба адреса увеличивается на +2.После этого значение счетчика будетсоответствовать адресу следующей команды, Сигнал с выхода элемента И 11поступает также на первый выход 13устройства, который может быть подключен к системе прерывания ЗВМ, еслипри отладке необходимо формироватьсигнал в соответствии с алгоритмом,реализованным в известном устройстве.В противном случае используют сигналс второго выхода 24 устройства, кото, рый формируется при наличии сигналана выходе элемента И 11, поступающего на второй вход элемента И 23, и .разрешающего сигнала на первом входе элемента И 23,Сигнал на первом входе элементаИ 23 вырабатывается по результатаманализа текущего адреса на принадлежность его полю адресов, отведенныхдля хранения команд отлаживаемогоучастка программы. При этом группаэлементов, состоящая из регистра 21,схем 19 и 20 сравнения, а также злемент И 22 работают аналогично группеэлементов, состоящей из регистров1 и 4, схем 2 и 3 сравнения а также элемента И 5, В результате на выходе элемента И 22 будет положительныйпотенциал, если текущий адрес находится в зоне адресов, ограниченнойрегистрами 18 и 21, что соотвехству ет командам отлаживаемого участкапрограммы,Б случае считывания операнда навыходе элемента И 5 будет запрещающий потенциал, блокирующий элементыИ 11 и 12. Текущее значение счетчика 8 не изменится, и сигнал прерывания на выходе 24 устройства не вырабатывается, независимо от сигналовна выходе схемы 9 сравнения, и первом входе элемента И 23.Для работы устройства необходимо,чтобы адрес вектора прерывания и технологическая программа обслуживанияпрерывания находились вне зоны адресов ПЗУ, определяемых регистрами 18и 21. Устройство для формирования сигналов прерывания при отладке программпо авт.св. 9 1185343, о т л и ч а ю -щ е е с я тем, что, с целью повышения достоверности работы, в устройство введены четвертая и пятая схемысравнения, четвертый и пятый регистры, четвертый и пятый элементы И,причем адресный вход устройства соединен с первыми входами четвертой ипятой схем сравнения, выходы которыхсоединены соответственно с первыми вторым входами четвертого элементаИ, информационные выходы четвертогои пятого регистров соединены с вторыми входами соответственно четвертойи пятой схем сравнения, выход четвертого элемента И соединен с первымвходом пятого элемента И, выход второго элемента И соединен с вторым .входом пятого элемента И, выход кото"рого является вторым выходом прерывания устройства,

СмотретьЗаявка

4162765, 15.12.1986

ПРЕДПРИЯТИЕ ПЯ Г-4152

БУДОВСКИЙ ЯКОВ МОИСЕЕВИЧ, БУРКОВСКИЙ ИГОРЬ ВЛАДИМИРОВИЧ, БОГДАНОВА КИРА ВИКТОРОВНА

МПК / Метки

МПК: G06F 11/28

Метки: отладке, прерывания, программ, сигналов, формирования

Опубликовано: 23.06.1988

Код ссылки

<a href="https://patents.su/3-1405061-ustrojjstvo-dlya-formirovaniya-signalov-preryvaniya-pri-otladke-programm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования сигналов прерывания при отладке программ</a>

Предыдущий патент: Генератор тестов

Следующий патент: Устройство для измерения частот появления групп команд

Случайный патент: Устройство рабочих камер для пневматических радиальных двигателей