Приемник дискретных частотно-модулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1385317

Авторы: Вариводский, Моисеенко, Ткачев, Чердынцев

Текст

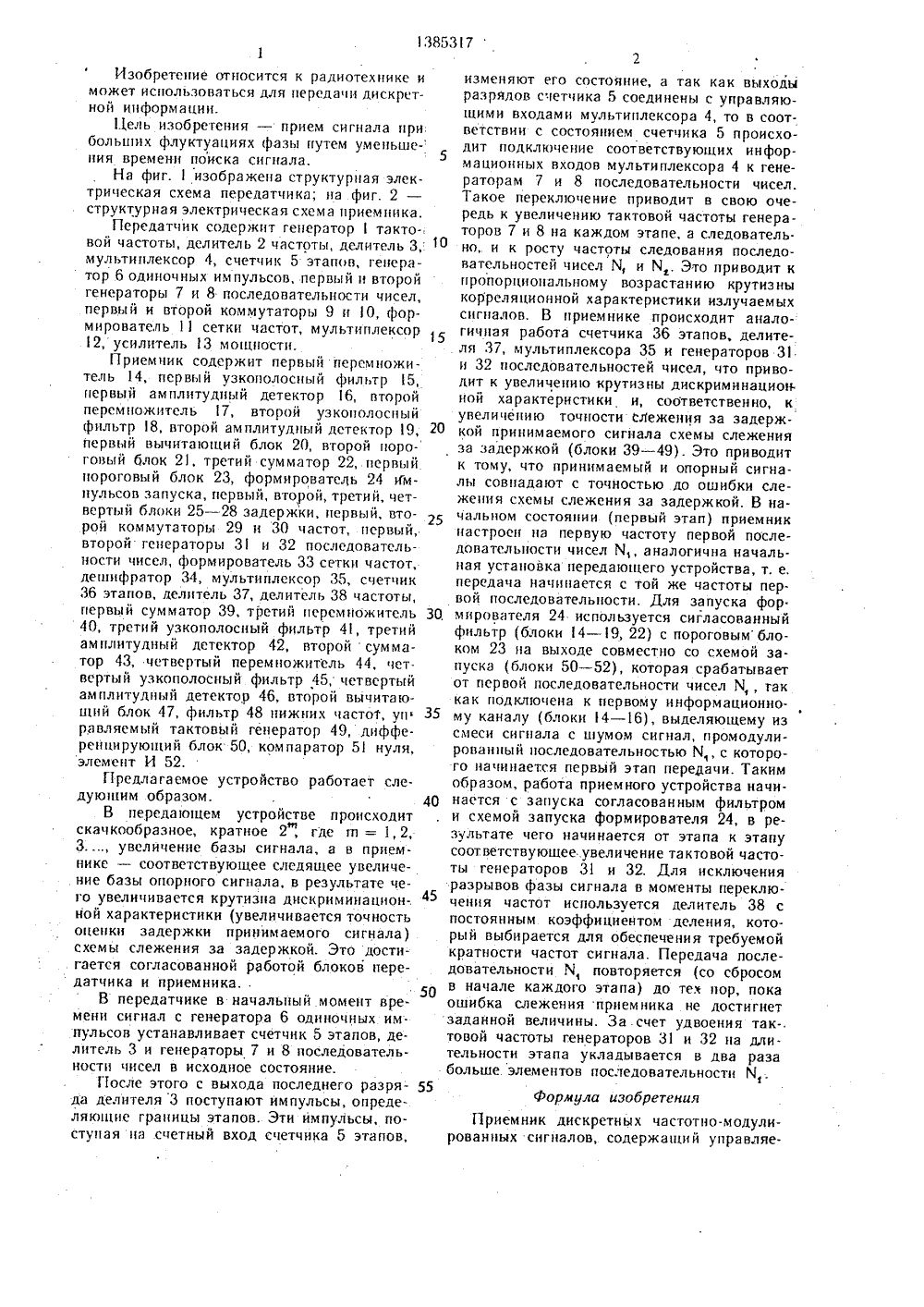

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 01385317 А 119) 504 Н 04 1.27 1ОПИСАНИЕ ИЗОБРЕТЕНИЯд ВТОРСНОМУ СВИДЕТЕЛЬСТВУ"Ф-г,ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ фвам(7 ) Минский радиотехнический институт(56) Чердыш 1 ев В. А. Статистическая теория совмещенных радиотехнических, систем.Минск: Высшая школа, 980, с. 7.(57) Изобретение относится к радиотехнике.Цель изобретения - прием сигнала прибольших флуктуациях фазы путем уменьшения времени поиска сигнала. Приемник содержит перемножители 4, 17, 40 и 44, блоки 25 - 27 задержки, коммутаторы 29 и 30,частот, г-ры 31 и 32 последовательности чисел, формирователь 33 сетки частот, делитель 38 частоты, сумматоры (С) 39 и 43, управляемый тактовый г-р 49. Введены уз;, кополосные фильтры 15, 18, 41 и 45, амплитудные детекторы 6, 19, 42 и 46, вычитаю-. гцие блоки 20 и 47, пороговые блоки 21 и 23 С 22, формирователь 24 импульсов запуска, блок 28 задержки, дешифратор 34, мультиплексор 35, счетчик 36 этапов, делитель 37, фильтр 48 нижних частот, диф. блок 50, компаратор 51 нуля, эл-т И 52. В передающем уст-ве происходит скачкообразное кратное 2 (гп = 1,2,) увеличение базы сигнала, в приемнике - соответствующее следящее увеличение базы опорного сигнала, в результате чего увеличивается крутизна дискриминац. х-ки (увеличивается точность оценки задержки принимаемого сигнала) схемы слежения за задержкой. Это достига .ется согласованной работой блоков передат чика и приемника. 2 ил.Изобретение относится к радиотехнике иможет использоваться для перслачи лискретной информации.Цель изобретения - прием сигнала при, больцгих флуктузциях фазы путем уменьше- ния времени поиска сигнала.На фиг. 1 изображена структурцая электрическая схема перелатчика; ца фиг. 2 - структурная электрическая схема приемника,Передатчик содержит генератор 1 тактовой частоты, делитель 2 частоты, делитель 3, мультиплексор 4, счетчик 5 этапов, генератор 6 одиночных импульсов, первый и второй генераторы 7 и 8 последовательности чисел, первый и второй коммутаторы 9 иО, формирователь 11 сетки частот, мультиплексор 5 12, усилитель 3 могццости.Приемник содержит первый псрсмцожитель 14, первый узкополосный фильтр 15, первый амплитудцый детектор 16, второй персмцожцтсль 17, второй узкополосный фильтр 18, второй амплитулцый лстектор 19, 20 первый вычитзющий блок 20, второй поро- говый блок 21, третий сумматор 22, первый пороговый блок 23, формирователь 24 Импульсов запуска, первый, второц, третий, четвертый блоки 25 - 28 задержки, первый, второй коммутаторы 29 и 30 частот, псрвый, второй генераторы 3 и 32 последовательности чисел, формирователь 33 сетки частот, лешифратор 34, мультиплексор 35, счетчик 36 этапов, лелцтель 37, делитель 38 частоты, первый сумматор 39, третий псрсмцожитсль 30 40, третий узкополосный фильтр 41, третий ам плитулцый лстсктор 42, второй сум матор 43, четвертый перемцожитсль 44, чст. всртый узкополосный фильтр 45, четвертый амплитулцый детектор 46, второй вычитающий блок 47, фильтр 48 нижних частот, уп 35 равлясмый тактовый генератор 49, диффе. реццирующий блок 50, компаратор 51 нули, элемент И 52.Предлагаемое устройство работает следуюгцим образом. 40В перелающем устройстве происходит скачкообразное, кратное 2 глс гп = 1, 2, 3 увеличение базы сигнала, а в приемнике - соответствующее следящее увеличение базы опорного сигнала, в результате чего увеличивается крутизна дискримицаццон ной характеристики (увеличивается точность оценки задержки принимаемого сигнала) схемы слежения за задержкой. Это достигается согласованной работой блоков передатчика и приемника 50В передатчике в начальцый.момент времени сигнал с генератора 6 одиночных импульсов устанавливает счетчик 5 этапов, делитель 3 и генераторы 7 и 8 последовательности чисел в исходное состояние.Госле этого с выхода последнего разря да делителя 3 поступают импульсы, определяющие границы этапов. Эти импульсы, поступая цз счетный вход счетчика 5 этапов,изменяют его состояние, а так как выходы разрялов счетчика 5 соединены с управляющими входами мультиплексора 4, то в соответствии с состоянием счетчика 5 происхолит полключецие соответствующих информационных входов мультиплексора 4 к генераторам 7 и 8 последовательности чисел. Такое переключение приводит в свою очередь к увеличению тактовой частоты генераторов 7 и 8 на каждом этапе, а следовательно, и к росту частоты следования последовательностей чисел Я, и 1 Ч,. Это приводит к пропорциональному возрастанию крутизны корреляционной характеристики излучаемых сигналов. В приемнике происхолит аналогичная работа счетчика 36 этапов, делителя 37, мультиплексора 35 и генераторов 31 и 32 последовательностей чисел, что приволит к увеличению крутизны дискриминационной характеристики и, соответственно, к увеличению точности слежения за задержкой принимаемого сигнала схемы слежения за залсржкой (блоки 39 - 49). Это приводит к тому, что принимаемый и опорный сигналы совпалают с точностью до ошибки слежения схемы слежения за задержкой. В начальном состоянии (первый этап) приемник настроен ца первую частоту первой последовательности чисел 1 Ч аналогична начальная установка передающего устройства, т. е. передача начинается с той же частоты пер. вой последовательности. Для запуска фор мирователя 24 используется сигласованный фильтр (блоки 14 - 19, 22) с пороговымблоком 23 ца выходе совместно со схемой запуска (блоки 50 - 52), которая срабатывает от первой последовательности чисел Х так как полключена к первому информационному каналу (блоки 14 - 16), выделяющему из смеси сигнала с шумом сигнал, промодулироваццый последовательностью М, с которого начинается первый этап передачи. Таким образом, работа приемного устройства начинается с запуска согласованным фильтром и схемой запуска формирователя 24, в результате чего начинается от этапа к этапу соответствующее. увеличение тактовой частоты генераторов 31 и 32. Для исключения разрывов фазы сигнала в моменты переключения частот используется делитель 38 с постоянным коэффициентом деления, кото. рый выбирается для обеспечения требуемой кратности частот сигнала, Перслача последовательности Х, повторяется (со сбросом в начале каждого этапа) до тех пор, пока ошибка слежения прием ника не лостигнет заданной величины. За.счет удвоения так-, товой частоты генераторов 31 и 32 ца длительности этапа укладывается в два раза больше.элементов последовательности Я,;Формула изобретенияПриемник дискретных частотно-модулированных сигналов, содержащий управляе138537 Фиг. 7 Составитель Н. ЛазареваРедактор Т. Парфенова Техред И. Верес Корректор М. ШарошиЗаказ 1124/55 Тираж 660 ПодписноеВНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж - 35, Раушская наб., д. 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул, Проектная, 4 3мый тактовый генератор, выход которого соединен с входами делителя частоты и формирователя сетки частот, выходы которого соединены с первыми входами первого и второго коммутаторов частот, вторые входы которых соединены с выходами первого и второго генераторов последовательностей чисел, первый, второй, третий блоки задержки, первый, второй, третий, четвертый перемножители, первые входы которых объединены и являются входом приемника дискретных частотно-модулированных сигналов, первый, второй сумматоры, отличающийся тем, что; с целью приема сигнала при больших флуктуациях фазы, путем уменьшения времени поиска, введены первый, второй, третий и четвертый узкополосные фильтры, первый, второй, третий и четвертый амплитудные детекторы, первый и второй вычитающие блоки, первый и второй пороговые блоки, формирователь импульса запуска, дешифратор, мультиплексор, счетчик этапов, делитель, фильтр нижних частот, третий сумматор, четвертый блок задержки, дифференцкрующий блок компаратор нуля, элемент И, вторые входы первого и второго перемножителей соединены с выходами третьего и четвертого блоков задержки, выход первого перемножителя через последовательно соединенные первый узкополосный фильтр и первый амплитудный детектор соединен с первыми входами первого вычитающего блбка и третьего сумматора, выход второго перемножителя через последовательно соединенные второй узкополосный фильтр и второй амплитудный детектор соединен с вторыми входами первого вычитающего блока и третьего сумматора, выход первого амплитудного детектора через последовательно соединенные дифференцирующий блок и компаратор нуля соединен с первым входом элемента И, выход третьего сумматора через первый пороговый блок соединен с вторым 4входом элемента И и первым входом формирователя импульса запуска, второй и тре тий входы которого соединены соответствен.но с выходом элемента И и выходом управляемого тактового генератора, выход третьего блока задержки через последовательно соединенные первый блок задержки, второй сумматор, четвертый перемножитель, четвертыи узкополосный фильтр и четвертый амплитудный детектор соединен с первым входом второго вычитающего блока, выход четвертого блока задержки через второй блок задержки соединен с вторым входом второго сумматора, выход первого коммутатора частот соединен с входом третьего 15 блока задержки и первым входом первогосумматора, выход второго коммутатора частот соединен с входом четвертого блока за- держки и вторым входом первого сумматора, выход которого через последовательно соединенные третий перемножитель, третий узкополосный фильтр и третий амплитудный детектор соединен с вторым входом второго вычитающего блока, выход которого через фильтр нижних частот соединен с входом управляемого тактового генератора, выход 25 формирователя импульсов запуска соединенс первыми входами счетчика этапов, делителя, обоих генераторов последовательностей чисел, вторые входы которых соединены с выходом мультиплексора, выход делителя частоты соединен с вторым входом делителя, один выход которого соединен с входом счетчика этапов, а другие выходы - с первыми входами мультиплексора, вторые входы которого и входы дешифратора соединены с выходами счетчика этапов, выход первого вычитающего блока соединен с входом второго порогового блока, выход которого является первым выходом приемника дис.кретных частотно-модулированных сигналов, вторым выходом которого является выход дешифратора,

СмотретьЗаявка

4020616, 06.02.1986

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ЧЕРДЫНЦЕВ ВАЛЕРИЙ АРКАДЬЕВИЧ, МОИСЕЕНКО МИХАИЛ ИВАНОВИЧ, ВАРИВОДСКИЙ АЛЕКСАНДР ОЛЕГОВИЧ, ТКАЧЕВ АЛЕКСАНДР ГЕННАДЬЕВИЧ

МПК / Метки

МПК: H04L 27/14

Метки: дискретных, приемник, сигналов, частотно-модулированных

Опубликовано: 30.03.1988

Код ссылки

<a href="https://patents.su/3-1385317-priemnik-diskretnykh-chastotno-modulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Приемник дискретных частотно-модулированных сигналов</a>

Предыдущий патент: Устройство приема сигналов с амплитудно-фазовой модуляцией

Следующий патент: Устройство для приема частотно-манипулированных сигналов

Случайный патент: Патронный фильтр для жидкости