Демодулятор фазоманипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

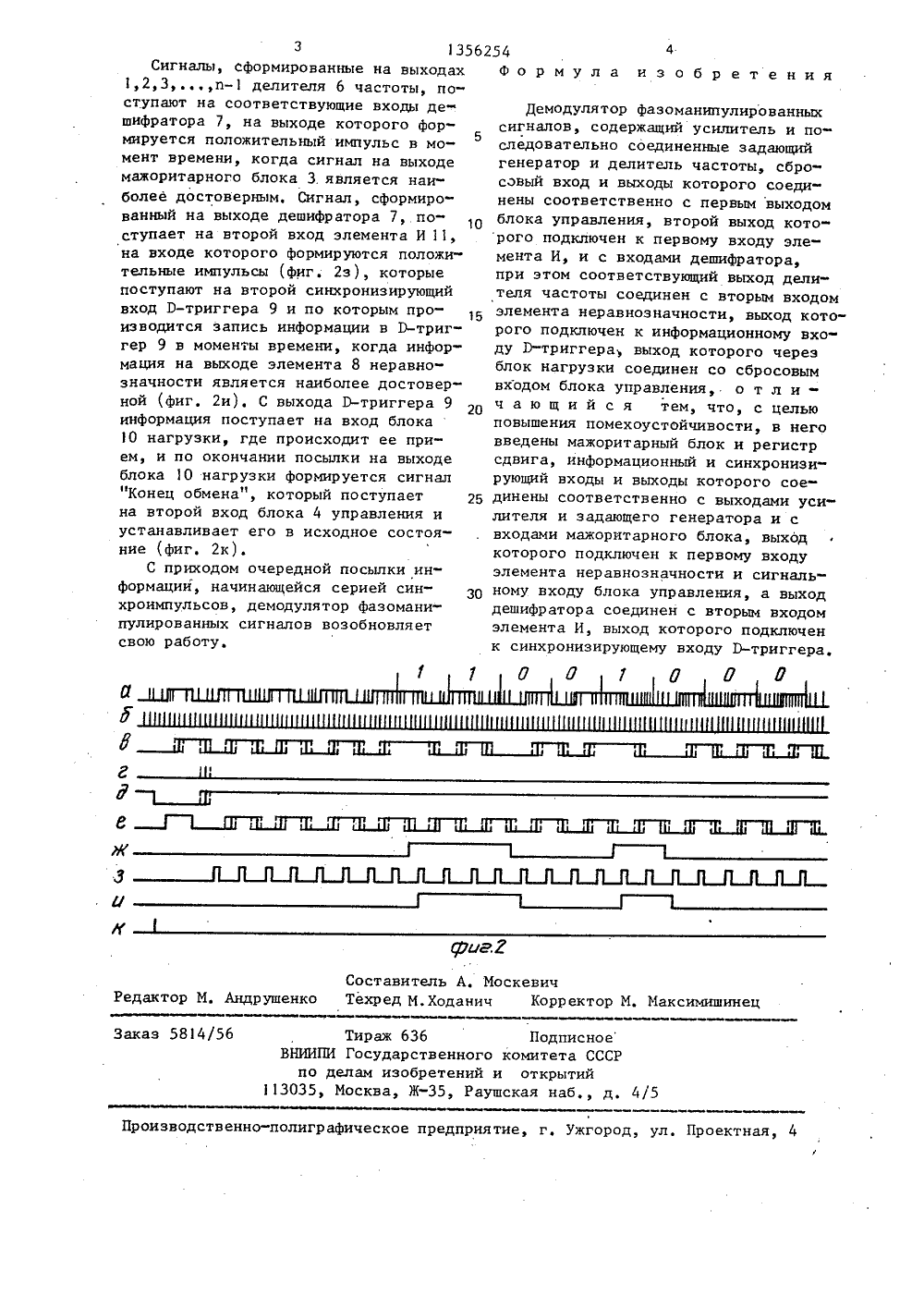

)4 Н ОСУДАРСТВЕННЫЙ НО О ДЕЛАМ ИЗОБРЕТЕНИ ТЕТ СССРИ ОТНРЫТИЙ САНИЕ ИЗОБРЕТЕ У 44 И Елаг ина,ив и Л. С. Иванцив088.8)видетельство СССР03 К 9/04, 1980,ок М СЬ К АВТОРСКОМУ СВИДЕТЕЛЬС( 54 ) ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ(57) Изобретение относится к техниксвязи и повышает помехоустойчивостьУстройство содержит усилитель 1, бл4 управления, задающий генератор 5,делитель 6 частоты, дешифратор 7,элемент 8 неравнозначности, Э-триггер 9, блок 10 нагрузки, элементИ 1, Вновь введены регистр 2 сдвигаи мажоритарный блок 3. 2 ил.При наличии случайной помехи во входном сигнале возможно появление дополнительного Фазового сдвига между сигналом, сформированным на выходе мажоритарного блока 3, и эталонным, формируемым на выходе и делителя частоты 6, что приводит к недостоверности информации на фронтах сигнала, сформированного на выходе элемен- та 8 неравнозначности,1 13562Изобретение относится к техникесвязи и может использоваться в приемныхустройствах систем передачиинформации.Цель изобретения - повышение поме 5хоустойчивости.На Фиг, 1 представлена структурнаяэлектрическая схема предложенногодемодулятора; на фиг, 2 - эпюры напряжений, поясняющие его работу,Демодулятор фазоманипулированныхсигналов содержит усилитель 1, регистр 2 сдвига, мажоритарный блок 3,блок 4 управления, задающий генератор 5, делитель 6 частоты, дешифратор 7, элемент 8 неравнозначности,;0-триггер 9, блок 10 нагрузки, элемент И 11.Демодулятор работает следующим образом.Каждая информационная посылка состоит из импульсов синхронизации иопределенного числа бит информации,Блок 10 нагрузки представляет собой 25приемное устройство, которое принимает информацию, определяет конецпосылки и формирует сигнал "Конецобмена". Задающий генератор 5 выбирается с частотой, близкой к частотеслучайной помехи (фиг, 1), присутствующей во входном сигнале, причемтактовая частота должна быть в 2 шраз выше частоты входного сигнала,где ш - целое нечетное число, что35необходимо для обеспечения правильной работы мажоритарного блока 3,разрядность .которого, а также разрядность регистра 2 сдвига равна ш,Блок 4 управления устанавливаетсяв исходное состояние сигналом "Конецобмена", .поступающим на его второйвход с выхода блока 10 нагрузки вначале работы и после завершения кажцой посылки информации, т,е на егопервом и втором выходе устанавливается состояние 0". Информационнаяпосылка в виде Фазоманипулированногосигнала несущей частоты с входа устройства поступает на вход усилителян и 501, усиливается до уровня 1 и с выхода усилителя(Фиг, 2 а) поступаетна первый информационный вход регистра 2 сдвига, на второй синхронизирующий вход которого поступают импульсы55тактовой частоты с выхода задающегогенератора 5 (фиг, 2 б), по которым врегистр 2 сдвига производится записьочередного значения входного сигнала,542поступающего на первый информационный вход, и сдвиг на один разряд информации, записанной в предыдущих тактах, С выходов регистра 2 сдвига информация поступает на входы мажоритарного блока 3, на выходе которого формируется сигнал уровня "1", если большинство разрядов регистра 2 сдвига находится в состоянии "1", и уровня "0", если большинство разрядов регистра 2 сдвига находится в состоянии "0" (фиг, 2 в), который поступает на первый вход блока 4 управления и на первый вход элемента 8 неравнозначности. При поступлении на первый вход блока 4 управления первого спада первого синхроимпульса данной посылки на первом выходе его формируется положительный импульс сброса (фиг. 2 г), который поступает на второй сбросовый вход делителя 6 частоты и устанавливает на его выходах состояние "0", на втором выходе блока 4 управления в то же время формируется уровень "1" (Фиг. 2 д), который поступает на первый вход элемента И 11 и разрешает его работу,С приходом импульсов тактовой частоты с выхода задающего генератора 5 на первый, счетный вход делителя 6 частоты на его выходе и формируется сигнал с периодом, равным периоду сигнала, сформированного на выходе мажоритарного блока .3, и с минимальным Фазовым сдвигом относительно этого сигнала при кодировании "0", С выхода и делителя 6 частоты сигнал поступает на второй вход элемента 8 неравнозначности (фиг, 2 е) на выходе которого при поступлении на первый вход кода "0" формируется уровень "0" при поступлении кода "1" на выходе формируется уровень, Сигнал, сформированный на выходе элемента 8 не-,: равнозначности (фиг. 2 ж), поступает на первый информационный вход Б-триггера 9.6254 Формула изобретения а Х Р г Р е и Составитель А. МоскевичРедактор М. Андрушенко Техред М.Ходанич Корректор М. Максимишинец Тираж 636 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 13035, Москва, Ж, Раушская наб., д. 4/5Заказ 5814/56 Производственно-полиграфическое предприятие, г, Ужгород, ул. Проектная, 4 з 135Сигналы, сформированные на выходах1,2,3пделителя 6 частоты, поступают на соответствующие входы дешифратора 7, на выходе которого формируется положительный импульс в момент времени, когда сигнал на выходемажоритарного блока 3 является наиболее достоверным. Сигнал, сформированный на выходе дешифратора 7, поступает на второй вход элемента И 11,на входе которого формируются положительные импульсы (фиг, 2 з), которыепоступают на второй синхронизирующийвход Р-триггера 9 и по которым производится запись информации в 13-триггер 9 в моменты времени, когда информация на выходе элемента 8 неравнозначности является наиболее достоверной (фиг, 2 и). С выхода 0-триггера 9информация поступает на вход блока10 нагрузки, где происходит ее прием, и по окончании посылки на выходеблока 1 О нагрузки формируется сигнал"Конец обмена", который поступаетна второй вход блока 4 управления иустанавливает его в исходное состояние (фиг. 2 к).С приходом очередной посылки информации, начинающейся серией синхроимпульсов, демодулятор фазоманипулированных сигналов возобновляетсвою работу,Демодулятор фазоманипулированныхсигналов, содержащий усилитель и последовательно соединенные задающийгенератор и делитель частоты, сбросовый вход и выходы которого соединены соответственно с первым выходомблока управления, второй выход которого подключен к первому входу элемента И, и с входами дешифратора,при этом соответствующий выход делителя частоты соединен с вторым входомэлемента неравнозначности, выход которого подключен к информационному входу Э-триггера выход которого черезблок нагрузки соединен со сбросовымвходом блока управления, о т л ич а ю щ и Й с я тем, что, с цельюповышения помехоустойчивости, в неговведены мажоритарный блок и регистрсдвига, информационный и синхрониэирующий входы и выходы которого сое динены соответственно с выходами усилителя и задающего генератора и свходами мажоритарного блока, выходкоторого подключен к первому входуэлемента неравнозначности и сигнальЗ 0 ному входу блока управления, а выходдешифратора соединен с вторым входомэлемента И, выход которого подключенк синхронизирующему входу Э-триггера,

СмотретьЗаявка

4087175, 11.05.1986

ПРЕДПРИЯТИЕ ПЯ В-8751

ДУРДА ЯРОСЛАВ ПЕТРОВИЧ, ЕЛАГИНА ЛЮДМИЛА ИВАНОВНА, ИВАНЦИВ РОМАН-АНДРЕЙ ДМИТРИЕВИЧ, ИВАНЦИВ ЛЮДМИЛА СТЕПАНОВНА

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, сигналов, фазоманипулированных

Опубликовано: 30.11.1987

Код ссылки

<a href="https://patents.su/3-1356254-demodulyator-fazomanipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Демодулятор фазоманипулированных сигналов</a>

Предыдущий патент: Устройство для приема сигналов с относительной фазовой модуляцией

Следующий патент: Коммутационное устройство групповой связи

Случайный патент: Грейферная подача к прессу