Демодулятор сигналов относительной фазовой манипуляции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1336267

Автор: Царев

Текст

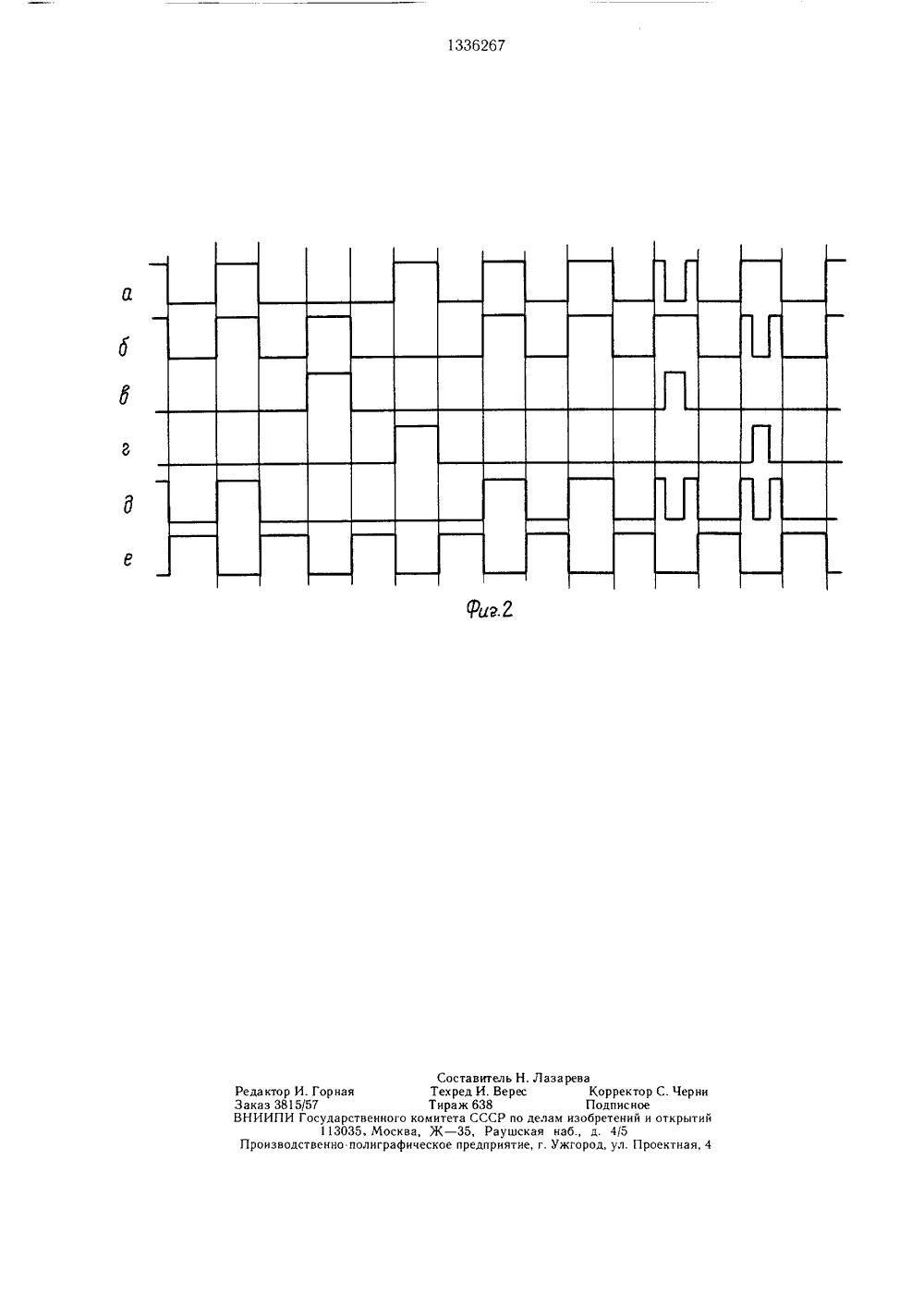

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКРЕСПУБЛИК А 1. 27 22 ПИСАНИЕ ИЗОБРЕТЕНИЯ АВТОРСКОМУ С ЕЛЬСТВУ В ОТНО- НИПУЛЯнике связи при больмирователя т сигнал с цией. С его жения поов (К) 2 и К 2 и 3 исной частоСВ ГОСУДАРСТВЕННЫИ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) ДЕМОДУЛЯТОР СИГНАЛСИТЕЛЬНОЙ ФАЗОВОЙ МАЦИИ(57) Изобретение относится к техи повышает помехоустойчивостьшом уровне шумов. На вход фор1 парафазного сигнала поступаеотносительной фазовой манипулявыхода два парафазных напрядаются на 2-е входы компаратор3. Сигналы с инверсных выходовпользуются для получения двой ЯО 1336267 ты. С этой целью эти сигналы логически перемножаются в эл-те И - НЕ 14. При наличии искажений в сигнале удвоенной частоты появляются сбои. Далее сигнал с выхода эл-та 14 поступает на логич. блок 15. На выходе блока 22 задержки формируется сигнал, задержанный на 1/2 периода входного сигнала. После логич. обработки сигналов на выходе эл-та ИЛИ - НЕ 21 восстанавливается сигнал удвоенной частоты, к-рый запускает триггер 6. С триггера 6 снимаются два сигнала основной частоты, сдвинутые по фазе на 180. На эл-тах И - НЕ 10 - 13 производится логич. перемножение сигналов с прямых выходов К 2 и 3, Результат перемножения, содержащий информацию о фазе входного сигнала, фиксируется в триггерах 4 и 5, На эл-тах И - НЕ 7 и 8 происходит выделение модулирующего сигнала 2 ил. 1 табл.10 15 20 формула изобретения 25 30 35 40 45 Изобретение относится к технике связи и является усовершенствованием изобретения по авт. св. Мо 1099411.Цель изобретения - повышение помехоустойчивости при большом уровне шумовНа фиг. 1 изображена структурная электрическая схема предлагаемого демодулятора; на фиг. 2 - временные диаграммы, поясняющие работу логического блока обработки сигнала.Демодулятор содержит формирователь 1 парафазных сигналов, компараторы 2 и 3, первый 4, второй 5 и третий 6 триггеры, первый 7, второй 8, третий 9, четвертый 10, пятый 11, шестой 12, седьмой 13, восьмой 14 элементы И - НЕ, логический блок 15 обработки сигнала, состоящий из первого 16 и второго 17 элементов НЕ, третьего 18, первого 19, второго 20 и четвертого 21 элементов ИЛИ - НЕ, блока 22 задержки,Демодулятор работает следующим об. разом.На вход формирователя 1 парафазного сигнала поступает сигнал с относительной фазовой манипуляцией, а с его выхода два противофазных напряжения подаются на вторые входы компараторов 2 и 3, которые формируют сигналы, пригодные для их обработки на цифровых интегральных микросхемах, Порог срабатывания обоих компараторов задается напряжением 11 о. Сигналы с инверсных выходов компараторов используются для получения двойной частоты, С этой целью сигналы с инверсных выходов компараторов 2 и 3 логически перемножаются в элементе И - НЕ 14. Сигнал двойной частоты формируется на выходе элемента И - НЕ 14 только при отсутствии искажений формы входного сигнала, при наличии искажений в сигнале удвоенной частоты появляются сбои. Далее сигнал с выхода элемента И - НЕ 14 поступает на логический блок 15. На выходе блока 22 задержки формируется сигнал, задержанный на 1/2 периода входного сигнала.Далее происходит логическая обработка сигналов а и б (фиг. 1) в соответствии с таблицей истинности На фиг. 2 поясняется работа логического блока 15, где а - сигнал на выходе элемента НЕ 16, б - на выходе элемента НЕ 17, в - на выходе элемента ИЛИ - НЕ 18, г - на выходе элемента ИЛИ - НЕ 19 д - на выходе элемента ИЛИ - НЕ 20, е - на выходе элемента ИЛИ - НЕ 21.Таким образом, после логической обработки на выходе элемента ИЛИ - НЕ 21 восстанавливается сигнал удвоенной частоты, который запускает триггер 6, С выходов триггера снимаются два сигнала основной частоты (несущей) сдвинутые по фазе на 180. На элементах И - НЕ 10 - 13 производится логическое перемножение сигналов с прямых выходов компараторов 2 и 3 с противофазными сигналами несущей. Результат перемножения, содержащий информацию о фазе входного сигнала, фиксируется в первом 4 и втором 5 триггерах. На элементах И - НЕ 7 и 8 происходит выделение модулирующего сигнала. В элементе И - НЕ 9 происходит объединение двух возможных вариантов выявления модулирующего сигнала. Демодулятор сигналов относительной фазовой манипуляции по авт, св, Мо 1099411, отличающийся тем, что, с целью повышения помехоустойчивости при большом уровне шумов, введен логический блок обработки сигнала, включенный между выходом восьмого элемента И - НЕ и входом третьего триггера и состоящий из блока задержки, двух элементов НЕ и четырех элеметов ИЛИ - НЕ, причем вход блока задержки соединен с входом первого элемента НЕ и первыми входами первого и второго элементов ИЛИ - НЕ и. является входом логического блока обработки сигнала, выход блока задержки соединен с входом второго элемента НЕ, первым входом третьего элемента ИЛИ - НЕ и вторым входом второго элемента ИЛИ - НЕ, выход первого элемента НЕ соединен с вторым входом третьего элемента ИЛИ - НЕ, выход второго элемента НЕ соединен с вторым входом первого элемента ИЛИ - НЕ, выходы первого, второго и третьего элементов ИЛИ - НЕ соединены с соответствующими входами четвертого элемента ИЛИ - НЕ, выход которого является выходом логического блока обработки сигнала.1336267Риа 2Составитель Н, ЛазареваРедактор И. Горная Техред И. Верее Корректор С. ЧерниЗаказ 3815/57 Тираж 638 ПодписноеВНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж - 35, Раушская наб., д. 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

4030801, 20.12.1985

ПРЕДПРИЯТИЕ ПЯ Р-6254

ЦАРЕВ АНАТОЛИЙ БОРИСОВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, манипуляции, относительной, сигналов, фазовой

Опубликовано: 07.09.1987

Код ссылки

<a href="https://patents.su/3-1336267-demodulyator-signalov-otnositelnojj-fazovojj-manipulyacii.html" target="_blank" rel="follow" title="База патентов СССР">Демодулятор сигналов относительной фазовой манипуляции</a>