Аналоговое запоминающее устройство

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

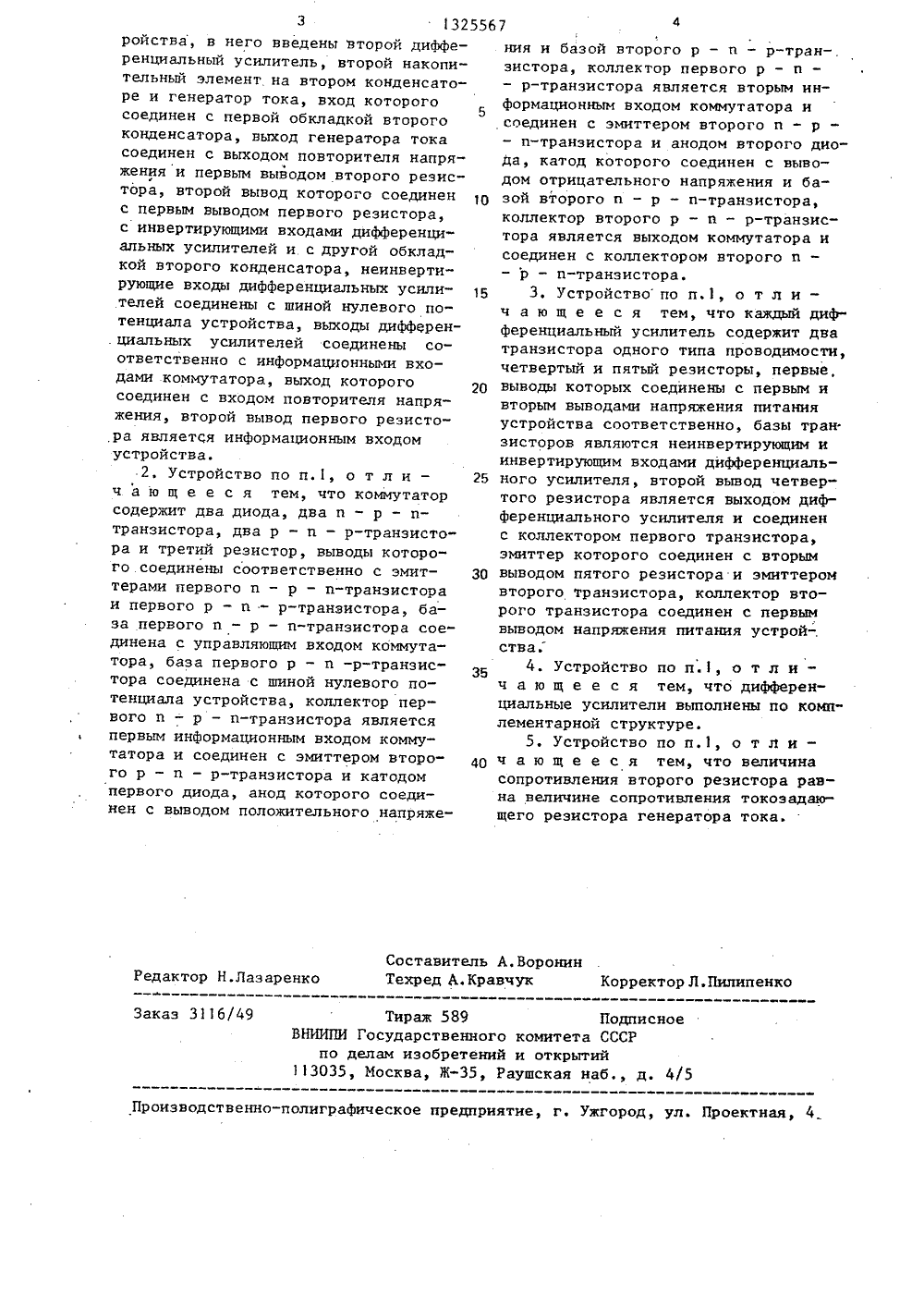

) ГОСУДАРСТВЕННЫЙ КОМИТЕТ. СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ ОПИСАНИЕ ИЗОБРЕТЕНИЯ , 3,Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(21) 4034459/24-24 (22) 10.0386 (46) 23.07,87, Бюл . (72) Л,Ю.Равер, Ю, И.И.Иноземцев и В. (53) 681.327.66(08 (56) Патент США У кл. С 11 С 27/02,Авторское свиде Ф 754481, кл. С. 11 У 27В. Тимкин,Б.Капранов8,8)4321488,1982,тельство. СССРС 27/00, 1977,(54) АНАЛОГОВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО(57) Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может бытьиспользовано в аналого-циФровых преобразователях. Цель изобретенияповышение быстродействия - достигнута за счет введения в устройство второго дифференциального усилителя,второго накопительного элемента навтором конденсаторе, генератора тока и их связей с известными элементами. Появление на.входе 2 положительного напряжения (логической единицы) приводит к отпиранию транзисторов 14 и 16 коммутатора 1, которые замыкают выходной ток усилителей 11 и 19. С конденсатора 4 нагряжение передается на выход б устройства и, в случае изменения выходного напряжения, оно компенсируется генератором 10 тока, Появление на входе 2 логического нуля приводит к запиранию транзисторов 14 и 16 и отпиранию транзисторов 15 и 1, в результате чего на входах усилителей 11 и 12 появляется напряжение, которое усиливается ими и вызывает изменение напряжения на конденсаторе 4. Выполнение усилителей 11 и 12 комплементарными обеспечивает симметричность передачи напряжения, что обеспечивает повьппение быстродействия устройства. 4 з.п. ф-лы 14 50 55 1132Изобретение относится к вычислительной технике, в частности к запоминающим устройствам, и может бытьиспользовано в аналого-циФровых преобразователях.Целью изоб 1 етения является повыше."ние быстродействия устройства.На чертеже изображена функциональная схема предлагаемого устройства.Устройство содержит коммутатор 1,вход 2 режима выборки - хранения у тройства, повторитель 3 напряжения,накопительные элементы на конденсато-.рах 4 и 5, выход 6, ограни-д.:.тельныйэлемент и элемент обра.нои связи на. резисторах 7 и 8 шину 9 нулевого потенциала, генератор 10 тока, диФФеренциальные усилители 11 и 12, информационный вхоц 3,Коммутатор 1 выполнен на п - ри-транзисторах 14 и 15, р - и в ртранзисторах 16 и 17, диодах 18 и19, резисторе 20 и имеет выводы 21и 22 положительного и отрицательного напряжений,Каждый диФФеренциальный усилитель11 или 12 вьполнен на транзисторах23 и 24, резисторах 25 и 26 и имеетвыводы 27 и 28 напряжения пигания,Генератор 10 тока выполнен на. транзисторе 29 токозадающем резисторе 30 и резисторе 31 и имеет выводы32 и 33 напряжения питания.Аналоговое запоминаящее устройст-во работает следующим образок,В исходном состоянии (в реымехранения) на вход 2 поступает голожительное напряжение, например, с выхода логического (ТТП) элемента.Транзисторы 16 й 14 коммутатора 1оказываются открьггыми и замыкаютвыходной ток усилителей 11 и 12транзисторы 5 и 17 коммутатора 1закрыты, и через диоды 18 и 19 протекает ток от источников питания соответственно с выводов 21 и 22. Напряжение с конденсатора 4 через повторитель 3 передается на выход 6. 11 зменения входного напряжения на входе13 не передаются на выя:эд 6 так каккомпенсируются инвертированнь 1 м сигналом транзистора 29 генератора 10тока, на который сигнал подается через конденсатор 5. Поягление нулевого (логического) уровня на входе 2приводит к запиранию транзисторов 14.и 16 коммутатора 1 и отпираьгию транзисторов 15 и 17 коммутатора 1. Пос 5 10 15 20 25 д г 3 ч ледние оказываются включенными по схеме с общей базой, что обеспечивает высокое быстродействие собственно коммутатора 1 Неравенство напряжений на входе 13 и выходе 6 (с учетом значений сопротивлений резисторов 7 и 8) приводит к появлению напряжения на инвертирующих входах усилителей 11 и 12, которое усиливается указанными усилителями и вызывает соответствующее изменение напряжения на конденсаторе 4. Выполнение усилителей 11 и 12 комплементарными обеспечива-. ет симметричность передачи напряжений различных. полярностей, что ведет к повьппению быстродействия всего устройства и не требует дополнительных корректирующих элементов,Появление на входе 2 положительного напряжения переводит устройство в исходное состояние.,4 тя повьппевия точности в режиме хранения повторитель 3 может быть выполнен с использованием МОП-транзистора, Транзистор 29 генератора 8 тока должен иметь большой коэФФициент передачи по току.Повьннеьие быстродействия устройства обеспечивается за счет использованная двух (комплеменгарных) диФФеренциальных усилителей, балансного построения коммутатора 1 и за счет использования генератора 10 тока для компенсапии паразитного прохокдения входного сигнала на выход устройства. При заданной точности устройство позволяет повысить быстродействие практически в 5-10 разФормула изобретения1, Аналоговое запоминающее устройство, содержащее коммутатор, управляющий вход когорого является. входом режима выборки-хранения устройства, повторитель напряжения, выход которого является выходок устройства, первый накопительный элемент на первом конденсаторе, первая обкладка которого соединена с шиной нулевого потенциала устройства, вторая обкладка первого конденсатора соединена с входом повторителя напряжения, первый диФФеренциальный усилитель, ограничительный элемент и элемент обратной связи на первом и втором резисторах, о т л и ч а ю щ е е с я тем, что с целью повьпнения быстр одей с твия уст5567 Составитель А.ВоронинТехред А.Кравчук Корректор Л. Пилипенко Редактор Н.Лазаренко Заказ 3116/49 Тираж 589 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб д. 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4 з 32 ройства, в него введены второй дифференциальный усилитель, второй накопительный элемент на втором конденсаторе и генератор тока, вход которого соединен с первой обкладкой второго конденсатора, выход генератора тока соединен с выходом повторителя напряжения и первым выводом второго резистора, второй вывод которого соединен с первым выводом первого резистора, с инвертирующими входами дифференциальных усилителей и с другой обкладкой второго конденсатора, неинвертирующие входы дифференциальных усилителей соединены с шиной нулевого потенциала устройства, выходы дифферен. циальных усилителей соединены соответственно с информационными входами коммутатора, выход которого соединен с входом повторителя напряжения, второй вывод первого резистора является информационным входом устройства.2. Устройство по п.1, о т л и ч а ю щ е е с я тем, что коммутатор содержит два диода, два п - р - и- транзистора, два р - и - р-транзистора и третий резистор, выводы которого.соединены соответственно с эмиттерами первого п - р - п-транзистора и первого р - п - р-транзистора, база первого и - р - и-транзистора соединена с управляющим входом коммутатора, база первого р - п -р-транзистора соединена с шиной нулевого потенциала устройства, коллектор первого и - р - и-транзистора является первым информационным входом коммутатора и соединен с эмиттером второго р - и - р-транзистора и катодом первого диода, анод которого соединен с выводом положительного напряжения и базой второго р - и - р-транзистора, коллектор первого р - и -- р-транзистора является вторым информационным входом коммутатора исоединен с эмиттером второго и - р -- п-транзистора и анодом второго диода, катод которого соединен с выводом отрицательного напряжения и базой второго и - р - п-транзистора,коллектор второго р - и - р-транзистора является выходом коммутатора исоединен с коллектором второго ив- р - а-транзистора.15 3. Устройствопо п.1, о т л и -ч а ю щ е е с я тем, что каждый диф"ференциальный усилитель содержит дватранзистора одного типа проводимости,четвертый и пятый резисторы, первые, 20 выводы которых соединены с первым ивторым выводами напряжения питанияустройства соответственно, базы транзисторов являются неинвертирующим иинвертирующим входами дифференциаль ного усилителя, второй вывод четвертого резистора является выходом дифференциального усилителя и соединенс коллектором первого транзистора,эмиттер которого соединен с вторым ЗО выводом пятого резистора и эмиттеромвторого транзистора, коллектор второго транзистора соединен с первымвыводом напряжения питания устрой-.ства.4. Устройство по п.1, о т л и -ч а ю щ е е с я тем, что дифференциальные усилители выполнены по комплементарной структуре.5. Устройство по п.1, о т л и - 4 О ч а ю щ е е с я тем, что величинасопротивления второго резистора равна величине сопротивления токозадающего резистора генератора тока.

СмотретьЗаявка

4034459, 10.03.1986

ПРЕДПРИЯТИЕ ПЯ А-1845

РАВЕР ЛЕВ ЮДОВИЧ, ТИМКИН ЮРИЙ ВИКТОРОВИЧ, ИНОЗЕМЦЕВ ИВАН ИЛЬИЧ, КАПРАНОВ ВЛАДИМИР БОРИСОВИЧ

МПК / Метки

МПК: G11C 27/00

Метки: аналоговое, запоминающее

Опубликовано: 23.07.1987

Код ссылки

<a href="https://patents.su/3-1325567-analogovoe-zapominayushhee-ustrojjstvo.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговое запоминающее устройство</a>

Предыдущий патент: Аналоговое запоминающее устройство

Следующий патент: Устройство для контроля блоков постоянной памяти

Случайный патент: Абразивный зубчатый инструмент