Полифазный интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1167618

Автор: Тетерин

Текст

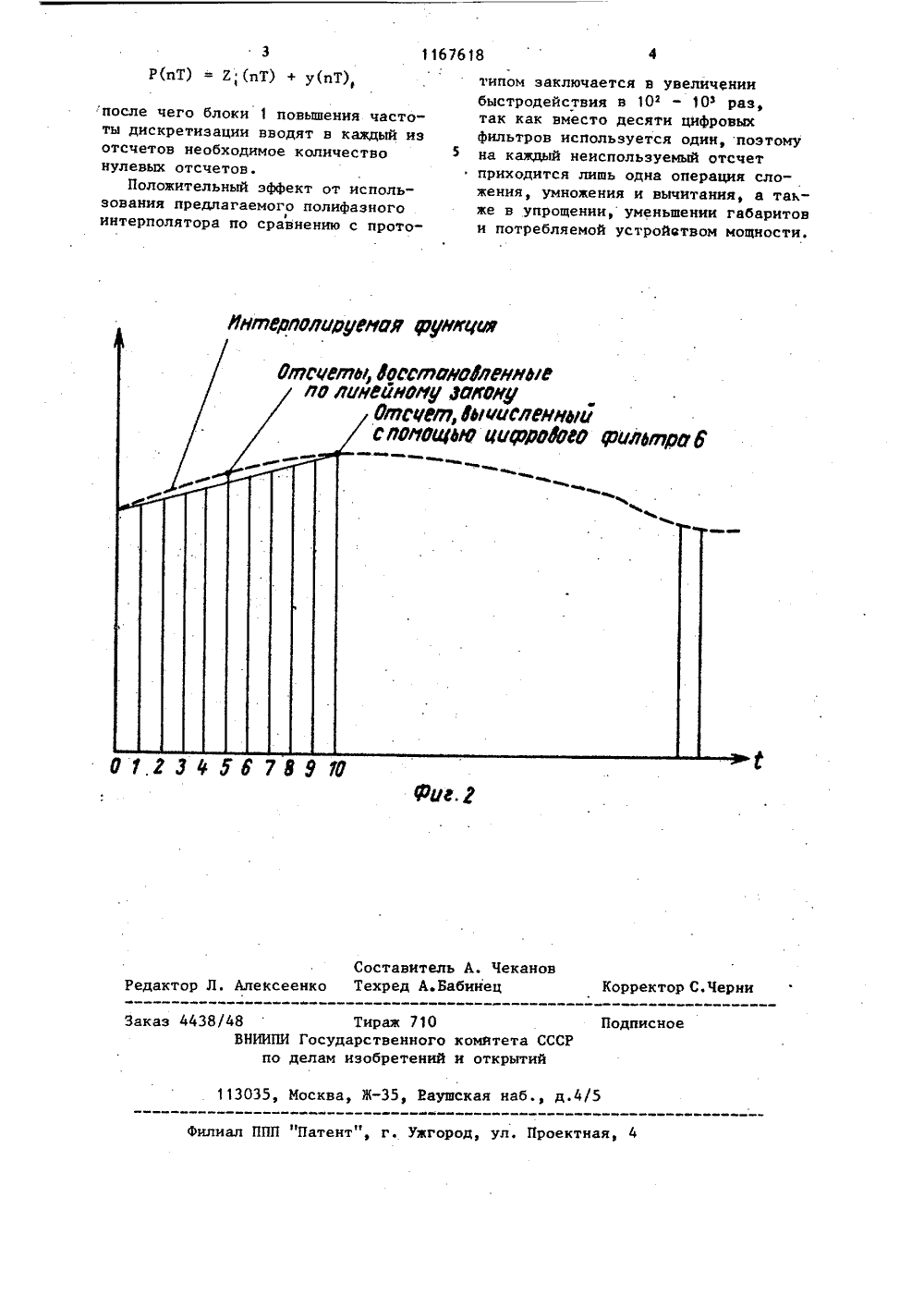

(9) (И) 26 во СС 1978. теригнап с ров 1ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССР ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ ИЗОБ К АВТОРСКОМУ СВИДЕТЕЛЬСТ(54)(57) ПОЛИФАЗНЬЙ ИНТЕРПОЛЯТОР,содержащий цифровой фильтр и П блоков повышения частоты дискретизации (где п - число фаз интерполяции), причем информационный входинтерполятора подключен ко входуцифрового фильтра, выход которого соединен с входом первого блока повьппения частоты дискретизациивыходы блоков повышения частотыдискретизации соединены с выходами интерполятора, о т л и ч а ю щ и йс я тем, что, с целью повышения быстродействия устройства, в него введены и -1 блоков умножения, и -1Ъсумматоров и блок вычитания, причем информационный вход интерполятора соединен с входом уменьшаемого блока вычитания, вход вычитаемого кото рого подключен к выходу цифрового фильтра, а выход - к входам первых сомножителей блоков умножения, вход второго сомножителя 1-го (1=Г и -1) блока умножения соединен с входом задания-го коэффициента интерполяции интерполятора, а выход .соединен с первым входом-го сумматора, выход которого подключен ко входу (1+1)-го блока повышения частоты дискретизации, выход которого подключен к (1+1)-му выходу интеролятора, выход цифрового фильтра оединен с вторыми входами суммато 1 116761Изобретение относится к вычислительной технике и может бытьиспользовано в системах передачи иобработки дискретной информации,гидро" и радиолокации, в телевиде-нии, электросвязи и другой аппара"туре и оуеугройсЪва, где необходимоаосущесв 8 лящунтеполяцию сигналов.Известен многоканальный цифровойфильтр, содержфйй сумматор и в10,каждом канапб оселедовательно сое"диненные. ура тры, выходы которыхподклтюяйИ квходам соответствую"щих устройств умножения, входы первого регистра и первого устройства 15умножения в первом канале соединены с входом фильтра, выход сумматораподключен к выходу фильтра и к входу первого регистра другого канала,коммутаторы, вход каждого из которых соединен с входом установки коэффициентов фильтра, а выход подключен к входу соответствующегоустройства умножения, причем выходкаждого устройства умножения в каждом канале через соответствующуюгруппу последовательно соединенныхрегистров подключен к входу сумматора 11 .Данное устройство не обеспечи" З 0вает режим параллельной обработкиинформации, вследствие чего характеризуется низким быстродействием .Наиболее близким к предлагаемомуявляется устройство полифазной интерполяции, содержащее Ь параллельно соединенных цепочек, каждая изкоторых представляет собой последовательно соединенные цифровой Фильтрнижних частот и устройство повышения частоты дискретизации Я .Известное устройство имеет большой объем вычислительных операций,вследствие чего характеризуетсянизким быстродействием. 451Цель изобретения - повышение быстродействия,Поставленная цель достигаетсятем, что в полифазный интерполятор,содержащий цифровой фильтр и и блоков повышения частоты дискретиза-.ции (где и - число фаэ интерполяции),причем информационный вход интерполятора подключен к входу цифрового фильтра, выход которого соединен 55с входом первого блока повышениячастоты дискретизации, выходы блоков повышения частоты дискретиэа 8ции соединены с выходами интерполятора, введены иблоков умножения, исумматоров и блок вычитания, причем информационный вход интерполятора соединен с входом уменьшаемого блока вычитания, вход вычитаемого которого подключен к выходу цифрового фильтра, а выход - к входам первых сомножителей блоков умножения вход второго сомножителя 1-го (г, облока умножения соединен с входом задания 1-го коэффициента интерполяции интерполятора, а выход соединен с первым входом д-го. сумматора, выход которого подключен к входу (1+1)-го блока повышения частоты дискретизации, выход цифрового фильтра соединен с вторыми входами сумматоров.На фиг. 1 приведена блок-схема предлагаемого устройства; на фиг.2. - временная диаграмма формирования интерполируемых отсчетов в предлагаемом устройстве.Полифазный интерполятор содержит а блоков 1 повышения частоты диск-ретизации, исумматоров 2,пблоков 3 умножения, блок 4 вычитания, блок 5 памяти констант и цифровой фильтр 6.Устройство работает следующим образом.В момент времени С = С входной отсчет х(пТ) поступает на входы цифрового фильтра 6 и блока 4На выходе цифрового фильтра 6 .Формируется один из восстановленных отсчетов у(пТ) ; В момент временина выходе блока 4 формируется раэность Е(пТ), Далее в момент времени С = С из блока 5 па 2мяти констант на вход умножителей 3 поступают отсчеты для вычисления тангенса угла линейной интерполяции. На выходе умножителей 3 формируются в момент времени С " С 5 результаты Е 1(пТ) по формулеЕ(пт) 1Е (пТ)где- 1, 2,;Е(пТ) = х(пТ) - у(пТ)рЬ - величина повышения частотыдискретизации.В момент времени С =. С на выходде сумматоров формируются результаты интерполированных отсчетов (Р(пТ)1167618 Р(пТ) = 2; (пТ) + у(пТ),Составитель А. ЧекановРедактор Л. Алексеенко Техред А.Бабинец Корректор С,ЧерниПодписное Заказ 4438/48 Тираж 710 ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 1 13035, Москва, Ж, Иаушская наб., д.4/5 Филиал ППП "Патент", г. Ужгород, ул. Проектная, 4 после чего блоки 1 повышения частоты дискретизации вводят в каждый из отсчетов необходимое количество нулевых отсчетов.Положительный эффект от использования предлагаемого полифазного3интерполятора по сравнению с прототипом заключается в увеличениибыстродействия в 10 - 10 раз,так как вместо десяти цифровыхфильтров используется один, поэтомуна каждый неиспользуемый отсчетприходится лишь одна операция сложения, умножения и вычитания, а также в упрощении, уменьшении габаритови потребляемой устройатвом мощности.

СмотретьЗаявка

3689750, 09.01.1984

ПРЕДПРИЯТИЕ ПЯ М-5209

ТЕТЕРИН ВАЛЕРИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 17/17

Метки: интерполятор, полифазный

Опубликовано: 15.07.1985

Код ссылки

<a href="https://patents.su/3-1167618-polifaznyjj-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Полифазный интерполятор</a>

Предыдущий патент: Система для оптимального решения задачи определения параметров линейных неоднородных материалов

Следующий патент: Устройство для прогнозирования случайных событий в технической системе

Случайный патент: Устройство для поперечной резки полосового проката