Устройство для ввода информации в процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1156081

Авторы: Винников, Любочанинов, Попов, Седов, Урывский

Текст

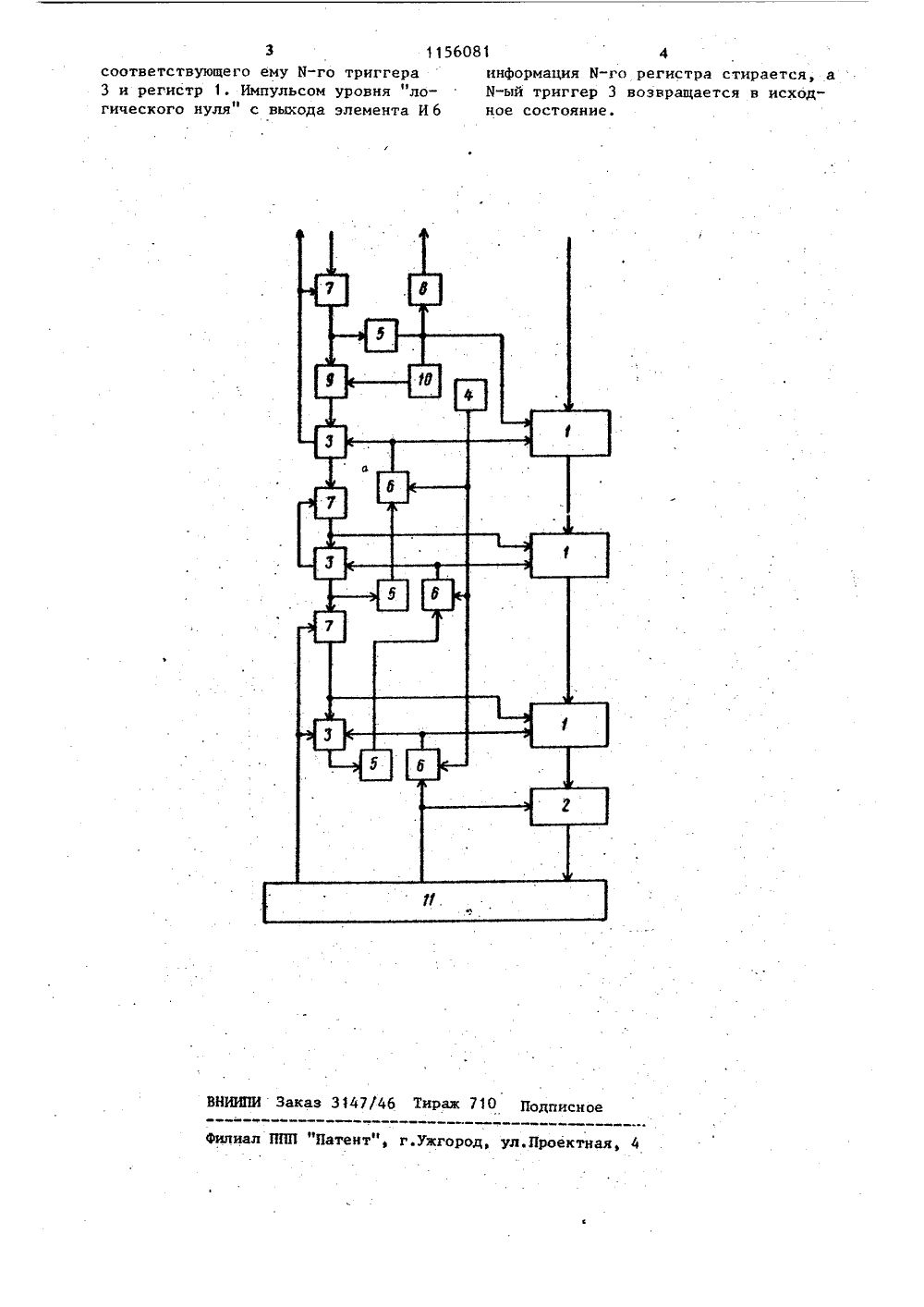

,115608 13/00 ГОСУД А ПО ДЕЛ ВЕННЫЙ НОМИТЕТ СССРИЗОБРЕТЕНИЙ И ОТНРЫТИЙСАНИЕ ИЗОБРЕТЕН КА СВИДЕТЕЛЬ ТОРСК ом(54)(57) УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ В ПРОЦЕССОР, содержащее. группу регистров, соединенных последовательно, информационный вход первогорегистра является информационнымвходом устройство, информационныйвыход которого через коммутаторсоединен с выходом последнего регистра группы, узел начальной установки,выход которого соединен с первымивходами элементов И первой группы,выход каждого из которых соединен сустановочным входом соответствующего регистра группы и с первым входом соответствующего триггера группы,о т л и ч а ю щ е е с я тем, что,с целью повышения достоверности, внего введены вторая группа элементовИ, группа формирователей импульса,элемент И, элемент задержки, формирователь импульса, причем первыйвыход каждого предыдущего триггерагруппы, кроме последнего, соединенс первым входом элемента И второйгруппы, соответствующего каждомупоследующему триггеру группы, выходкаждого из элементов И второй группы,кр е соответствующего первому триггеру, соединен с управляющим входомсоответствующего регистра группы ивторым входом соответствующего триггера группы, первый вход элемента Ивторой группы, соответствующего первому триггеру группы, является входоразрешения записи устройства, второйвыход каждого триггера группы соединен с вторым входом соответствующегоэлемента И второй группы, первый выход каждого последующего триггерагруппы через соответствующий Формирователь импульса группы соединенс вторым, входом элемента И первойгруппы, соответствующего предыдущему триггеру группы, выход элемента Ивторой группы, соответствующего первому разряду, соединен с первымвходом элемента И н через соответствующий формирователь импульса группыс входами элемента задержки, управляющим входом соответствующего регистра группы и входом формирователя импульса, выход которого является выходом признака конца записи устройства, выход элемента задержки сое-:динен с вторым входом элемента И,выход которого соединен с вторымвходом первого триггера группы, вто- .рой внход которого является выходомпризнака начала записи устройства,второй выход последнего триггерагруппы является выходом готовностиввода устройства, вход разрешенияввода которого соединен с вторымвходом элемента И первой группы,соответствующего последнему триггеру группы, и управляющим входом коммутатора..С первого триггера 3 подают уровень "логической единицы" - сигнал "Разрешение записи". Если данные готовы, то они сразу же устанавливаются на входах первого регистра 1. На элемент. И 7 поступает сигнал "Разрешение записи", с выхода кото 55 1 115608Изобретение относится к вычислительной технике и может быть использовано, в частности, в измерителе толщины эпитаксиальных слоев на полупроводниковых пластинах, работающем в комплекте с ЭВМ, а также может быть использовано для временного хранения и передачи.данных из.аналого-цифрового преобразователя (АЦП) в ЭВМ, например в измерительных и 1 О вычислительных комплексах и системах, работа составных частей которых по передаче данных асинхронна и когда возникает необходимость временного хранения данных на линиях передачи 15 при сохранении нормальной работоспособности составных частей.Цель изобретения - повышение достоверности передачи информации.На чертеже приведена блок-схема предлагаемого устройствг.Устройство содержит регистры 1 группы, коммутатор 2, триггеры 3 группы, узел 4 начальной установки, Формирователи 5 импульса группы, р 5 элементы И 6 первой группы элементы. И 7 второй группы, формирователь 8 импульса элемент И 9, элемент 10 задержки.На чертеже приведена электронная вычислительная машина (ЭВМ) 11.Работа устройства происходит следующим образом.При включении питания узел 4 задерживает на некоторое время ка выходе установку уровня "логической35 единицы", что соответствует выработке одиночного отрицательного импульса начьльной установки, которыйоступает на вход элементов И 6. На вы-,40 ходе каждого элемента И 6 некоторое время после включения напряжения питания удерживается уровень "логического нуля", которым все триггеры 3 и, регистрь 1по входу "Сброс" уста 45 навливаются в исходное состояние, По ,истечении временй задержки на сбросовых входах триггеров 3 устанавливается уровень "логической единицы",разрешающий запись инФормации в триггеуы 3 и регистры 1. 1 грого через элемент И 9 сигнал "Запись" поступает на вход первого триггера 3 и опрокидывает его. Одновременно с этим запускается формирователь 5, который по переднему фронту входного сигнала вырабатывает одиночный импульс, по которому производится запись информации, стоящей на входе первого регистра 1. Одновременно запускается формирователь 8 и элемент 10, который образует, совместно с элементом схему блокировки первого триггера 3.При опрокидывании первого тригге- . ра 3 на его единичном выходе появляется уровень "логической единицы", на нулевом выходе - "логического нуля", т;е. сразу же снимается сигнал "Разрешение записи", поступающий на выход устройства и элемент И 7. С первого триггера 3 уровень "логической,единицы" поступает на элемент И 7, При наличии сигнала разрешения записи во второй триггер 3 и второй регистр 1 сигнал с выхода элемента Ипоступает на вход второго триггера 3, опрокидывая его, и на вход второго регистра. Информация из первого регистра переписывается во второй регистр. Сигнал с выхода второго триггера 3 подают на вход элемента И 7 соответствующего ему третьего триггера 3 и одновременно на вход формирователя 5, который вырабатывает одиночный импульс уровня "логи ческого нуля", поступающий на элемент И 6 соответствующего ему пер" вого триггера 3 и первого регистра 1. На время длительности импульса формирователя 5 на выходе элемента И 6 устанавливается уровень "логического нуля", которым первый триггер 4 возвращаетсяв исходное состоя-, ние, информация в первом регистрестирается.1Таким образом, информация из второго регистра 1 последовательно переписывается в последующий третийрегистр 1, пока не достигнет Н-го.При записи информации в Н-ый регистр 1 с выхода И-го триггера,3 в ЭВМ 11 подают сигнал "Готовность данных", ЭВМ отвечает сигналом "Считывание", который поступает на коммутатор 2, и информация из И-го регистра передается в ЭВМ 11 По зад-. нему фронту сигнала "Считывание" импульс подается на элемент И 6

СмотретьЗаявка

3542598, 18.01.1983

ПРЕДПРИЯТИЕ ПЯ Р-6707

ПОПОВ ВИКТОР АЛЕКСЕЕВИЧ, ВИННИКОВ ИВАН РОМАНОВИЧ, ЛЮБОЧАНИНОВ ВИКТОР НИКОЛАЕВИЧ, СЕДОВ АНАТОЛИЙ НИКОЛАЕВИЧ, УРЫВСКИЙ ЮРИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 13/00

Метки: ввода, информации, процессор

Опубликовано: 15.05.1985

Код ссылки

<a href="https://patents.su/3-1156081-ustrojjstvo-dlya-vvoda-informacii-v-processor.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для ввода информации в процессор</a>

Предыдущий патент: Двухпортовое устройство сопряжения в вычислительной системе

Следующий патент: Устройство для сопряжения электронно-вычислительной машины с накопителями на магнитных носителях

Случайный патент: 333934