Устройство для кодирования звуковых сигналов с инерционным компандированием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1197085

Авторы: Анисимов, Ванде-Кирков, Матвеев

Текст

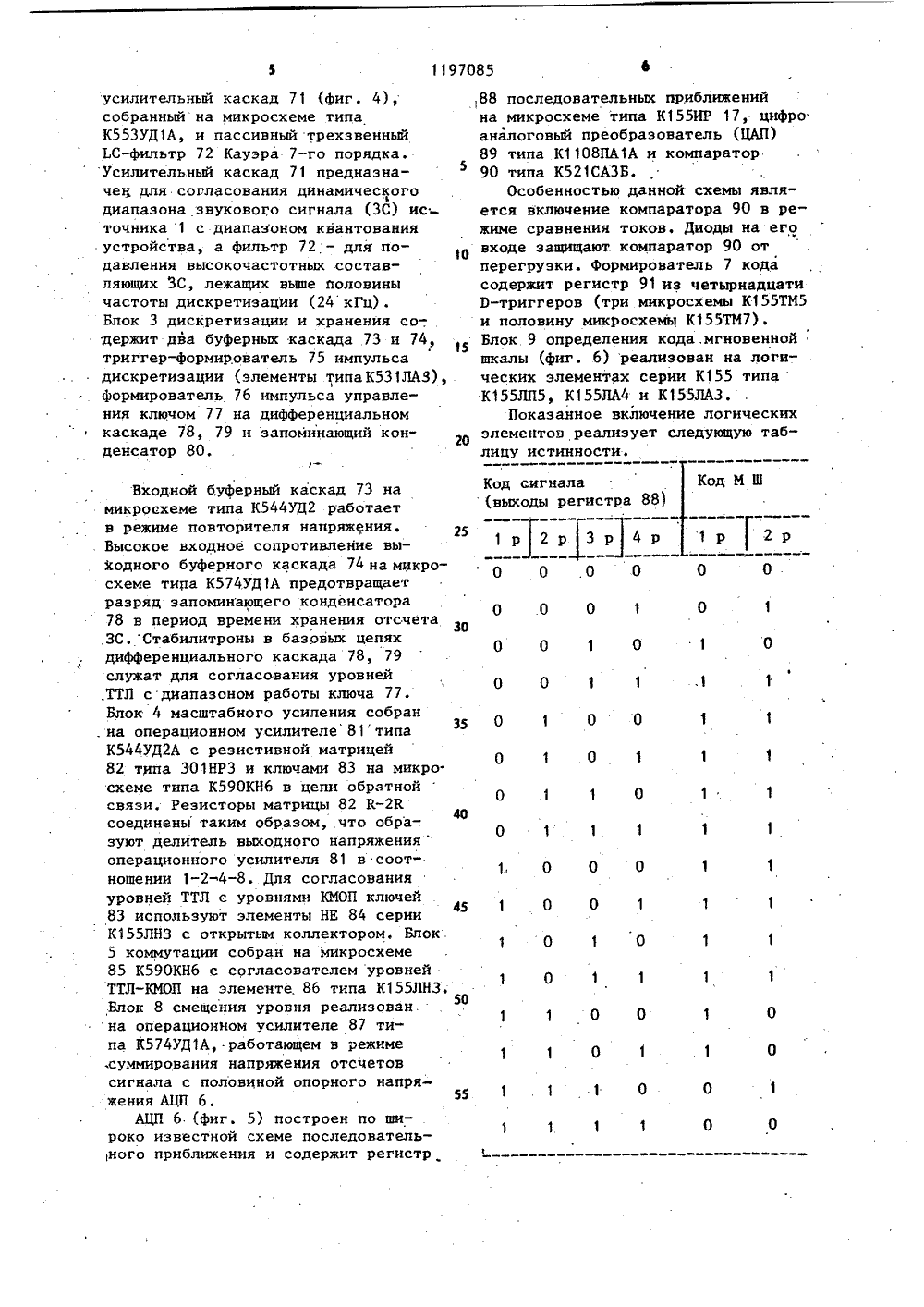

131 ИБЛИСЕКА НИЯ ЛЬСТ 4 т авиае-К о СССР,8,04,77.СССР10.06,81.СССР10.05.78. ОСУДАРСТВЕННЫЙ КОМИТЕТ СССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТ ОПИСАНИЕ ИЗ К АВТОРСКОМУ СВИ(71) Ленинградский институционного приборостроения(54) (57) 1, УСТРОЙСТВО ДЛЯ КОДИРОВАНИЯ ЗВУКОВЫХ СИГНАЛОВ С ИНЕРЦИОННЫМ КОМПАНДИРОВАНИЕМ, содержащееисточник сигнала, усилитель, блокдискретизации и хранения, блокмасштабного усиления, первый входи выход которого соединены с соответствующими входами блока коммутации, аналого-циФровой преобразователь, формирователь кода, первыевходы которого соединены с первымивыходами аналого-цифрового преобразователя, а выходы являются выходамиустройства, о т л и ч а ю щ е е с ятем, что, с целью увеличения. точности и уменьшения времени кодирования, в него введены блок смещенияуровня, блок определения кода мгновенной шкалы, блок формированиякода инерционной шкалы и блок управления, первый и второй выходыкоторого подключены соответственнок первому и второму управляющим входам блока дискретизации и хранениявход которого через усилитель соединен с источником сигнала, а выход подключен к первому входу блока масштабного усиления, управляющие входы которого объединены с соответствующими вторыми входами формирователя кода и подключены к первым выходам блока формирования кода инерционной шкалы, второй выход которого соединен с первым входом блока управления, третий выход которого подключен к третьему входу формирователя кода, а четвертый, пятый, шестой и седъмой выходы соединены соответственно с первым, вторым,.третьим.и четвертым входа ми блока формирования кода инерционной шкалы, пятый вход которого объединен с первым входом блока определения кода мгновенной шкалы и под. ключен к второму выходу аналого-цифрового преобразователя, шестые входы блока формирования кода инерционной шкалы соединены с выходамй блока определения кода мгновенной шкалы, вторые входы которогоподключены к соответствующим первым выходам аналого-цифрового преобразователя,третий и четвертый выходы которого соединены соответственно с вторым и третьим входами блока управления, восьмой выход которогр соединен с управляющим входом блокакоммутации, выход которого через блок смещения уровня подключен к первому входу аналого-цифрового преобра-. зователя, второй и третий входы ко" торого соединены соответственно с девятым и десятым выходами блока управления, четвертый вход которого подключен к шине внешней синхронизации.10 15 20 25 30 35 40 45 50 55 48 элементов И, Поэтому код мгновенной шкалы с шестых входов 33 блока 10 формирования кода ИЩ,черезпервый блок 48. элементов И и блок55 элемечтов ИЛИ поступает на первые входы регистра 56 кода ИШ, кудазаписывается с приходом синхроимпульба, на его второй вход с четвертого выхода 22 блока 11 управления. После записи кода в регистр 56 он поступает на управляющие входыблока 4 масштабного усиления (фиг. 1), в котором устанавливается один из возможных коэффициентов усиления напряжения отсчета. Далее напряжение отсчета через блок 5 коммутации поступает на вход блока 8 смещения уровня, с выхода которого подается на первый вход 32 АЦП 6. С приходом шестого тактового импуль" са с девятого выхода 35 блока 11 управления на второй вход 37 АЦП 6 (фиг. 4) производится вторая установка регистра 88 последовательных приближений и затем последовательное уравновешивание напряжения отсчета так, как описано выше. Разница только в том,что теперь во втором цикле преобразования определяются все 12 разрядов кода (используются тактовые импульсы с 7-го по 19-й). По окончании процесса поразрядного уравновешивания с четвертого выхода 40 АЦП 6 на третий вход 42 блока 11 управления выдается отрицательный перепад напряжения, по которому в формирователе 62 импульса конца преобразования вырабатываются два. коротких импульса длительностью 150 нс. Положительный импульс с третьего выхода 20 блока 11 управления поступает на третий вход 21 формирователя 7 кода (Фиг. 1 О ж), по которому производится запись 12-разрядной мантиссы слова с первых,выходов 12 АЦП 6 и 2-разрядного кода порядка с первых выходов 15 блока Ю определения кода шкалы в регистр 91 (фиг. 5). Отрицательный импульс с первого выхода формы рователя 62 импульса конца преобра зования поступает на первый вход генератора 63 тактовых импульсов (Фиг; 8) КЗ-триггер 116 и 117 возвращается в нулевое состояние, срывая работу тактового генератора 118. Устройство ждет прихода следую. щего запускающего импульса задающего генератора 65 импульсов.Таким образом, устройство работает при неизменном уровне входного сигнала или при его увеличении независимо от значения кода инерционной шкалы. Однако, при уменьшении уровня сигнала смена кода шкалы происходит только в течение первого отсчета противоположной полярности. Предположим, что уровень сигнала уменьшается и за.время между двумя последовательными сменами полярности отсчетов подтверждениякода инерционной шкалы ни разуне произойло. Эта значит, что цифровой компаратор 57 (Фиг. 2)весь определенный вьппе интервалвремени выдает следующую информацию: на первом и втором выходах - уровень логического нуля, а на третьем выходе - уровень логической единицы. Вследствие этого на первом и втором входах элемента ИЛИ 58 и на входе элемента НЕ 47 присутствуют уровни логического нуля. Блок51 памяти признака обнулен отрицательным импульсом, пришедшим на его второй, вход с пятого выхода 23блока 11 управления. Импульс обнуле -ния формируется в блоке 61 Формирования импульса обнуления во втором цикле преобразования каждогопервого отсчета противоположнойполярности (фиг. 8). Это происходитследующим образом. В первом цикле после установки пятого разряда регистра последовательных приближенийв АЦП 6 по отрицательному фронту формирователь 60 импульсов конца первого цикла вырабатывает положительный импульс, который поступает на второй вход блока 61 формирования импульса обнуления. Третий импульс с выхода формирователя 70 импульсов синхронизации в течение времени между пятым и шестцй так" товыми импульсами возвращает триггер 68 завершения первого цикла в нулевое состояние, обеспечивая с одной стороны возможность работы блока 69 формирования импульсов начальной установки (Фиг, 8), а с другой - выдает уровень логическойединицы на первый вход блока 61 Формирования Импульса обнуления памяти, третий вход которого подключен к второму выходу 16 блока10 формирования кода инерционной17шкалы (фиг.:7), а точнее к первому выходу блока 46 формирования импульса смены знака. Последний работает следующим образом. Первый инверсный разряд кода со второго вькода 31.АЦП 6 поступает на пятый вход 30 блока 10 формирования кода инерционной шкалы. Здесь он по синхроимпульсу, проходящему с седьмого вькода 25 блока 11 управ пения на четвертый вход 29 блоха 10 формирования кода. инерционной шкалы, записывается во второй Р-триггер микросхемы 100. (Фиг.7), выходы которого подключены к входам ждущих мультивибраторов микросхемы 103, Последние вырабатывают импульсы, которые затеМ замешиваются на первых двух элементах микросхемы 103. Положительные импульсы с выхода второго элемента этой микросхемы поступают на первый вход 17 блока 11 управления. Ясно, что если на всех трех входах элемента ЗИ-НЕ 141 (фиг. 8) в блоке 61 формирования импульса обнуления окажутся уровни логических единиц, то на его выходе возникнет отрицательный импульс, который и обнуляет блок 51 памяти признака (фиг. 10, к). На выходе блока 51 (фиг. 2) имеется уровень логической единицы, который поступает на первый вход элемента И 52. Элемент НЕ 47 инвертирует входной уровень .логического нуля, подавая на второй вход элемента И 52 уровень логической единицы. На выходе элемента И 52 также появпяется уровень логической единицы, который поступает на первый вход блока 53. уменьшения кода, С вькодов последнего значение кода, уменьшенное на единицу, поступает на первые входы третьего блока 54 элементов И. При появлении 97085 18информации на вькодах блока 46 формирования импульсов смены знака,открытый по первому входу второйблок 49 элементов И закрывается повторьи входам, а третий блок 54 элементов И открывается, так как наего третий вход с первого выходаблока 46 формирования импульсовсмены знака поступает уровень доги О ческой единицы. При этом код инерционной шкалы, уменьшенный на единицу, с выхода блока 53 уменьшения кода через третий блок 54 элементов И, через блок 55 элементов 15 ИЛИ поступает .на первые входы регистра 56 кода ИШ, куда и записывается с приходомсинхроимпульса с четвертого выхода 22 блока 11 управления на первый вход 26 блока 10 20 формирования кода ИШ. Далее работаустройства происходит так, какописано вышее. Может случиться так, что код мгно венной шкалы для первого же отсчетапротивоположной полярности будетбольше кода инерционной шкалы, записанного в регистре 56.кода ИШ.Тогда информация на вькодах цифрового компаратора 57 меняется на противоположную. Второй блок 49 элементов И и третий блок 54 элементов И, несмотря на разрешение, приходящее с блока 46 формированияимпульса смены .знака, запираются, 35но отпирается первый блок 48 элементов И, Поэтому код мгновенной шкалы, приходящий с выходов блока 9определения кода мгновенной шкалы нашестые входы 33 блока 10 формирования кода ИШ через первый блок 48элементов И и блок 55 элементовИЛИ, поступает на первые входы регистра 56 кода ИШ и записывается внего так, как описано выше.2, Устройство по п. 1, о т.л ич а ю щ е е с я тем, что блок формирования кода инерционной шкалы содержит блок начальной установки, блок формирования импульса смены знака,элемент НЕ, три блока элемен.тов И, блок самоблокировки памяти, .блок памяти признака, элемент И, блок уменьшения кода, блок элементов ИЛИ, регистр, цйфровой компаратор и элемент ИЛИ, выход которого подключен к первому входу блока памяти признака, выход которого соединен с первыми входами элементаИ и блока самоблокировки памяти, ,выход которого подключен к второму входу блока памяти признака, выход элемента И соединен с первым входом блока уменьшения кода, выходы которого соединены с первыми входами третьего блока элементов И, выхо . ды всех блоков элементов И подключены к соответствующим входам блока элементов ИЛИ, выходы. которого сое динены с первыми входами регистра, первые выходы которого соединены .с первыми выходами блока формирования кода инерционной шкалы и подклю. чены к соответствующим первым входам второго блока элементов И и цифрового компаратора, вторые вьмоды регистра подключены к вторым входам блока уменьшения кода, второй вход регистра соединен с выходом блока начальной установки, а третий вход - с первым входом блока формирования кода инерционной шкалы, входы которого с второго о пятый подключены соответственно к третьему входу блока памяти признака, второму входу блока самоблокировки памяти, первому:и второму входам блока формирования импульса смены знака, первый выход которого соединен с вторым входом третьего блока, элементов И и с вторым выходом блока формирования кода инерционной шкалы, шестые входы которого подключены к первым входам первого блока элементов И и вторым входам цифрового компаратора, первый выйодкоторого соединен с вторым входомпервого блока элементов И и первымвходом элемента ИЛИ, второй выходцифрового компаратора подключенк второму входу элемента ИЛИ ичерез элемент НЕ - к второму входу элемента И, третий выход цифрового компаратора соединен стретьим входом третьего блока элементов И и вторым входом второгоблока элементов И, третий входкоторого подключен к второму выходу блока формирования импульса смены знака. 3. Устройство по и. 1, о т л ич а ю щ е е с я тем, что блок управления содержит формирователь импульса управления блоком коммутации,формирователь импульса конца первого цикла, блок формирования импульса обнуления памяти, формирователь импульса конца преобразования, генератор тактовых импульсов, первый и второй формирователи импульсов,задающий генератор импульсов, переключатель, триггер, блок формирования импульсов начальной установки и формирователь импульсов синхронизации, первый выход формирователя импульса конца преобразования соединен с первым входом генератора тактовых импульсов, выход которого подключен к входу первого формирователя импульсов, выход задающегогенераторасоединен с первым входом переключателя, выход которого через второй формирователь подключен к второму входу генератора тактовых импульсов и первому входу формировате"ля импульса управления блоком коммутации и первому входу триггера,первый выход которого подключен к первому входу блока формирования импульсов начальной установки, первый выход которого соединен с входом формирователя импульсов синхронизации, первый выход которого подключен к второму входу триггера, второй выход которого соединен с первым входом блока формирования импульса обнуления, памяти, второй вход которого объединен с вторым входом блока формирования импульсов начальной установки и подключен к первому выходу формирователя импульса. конца первого цикла, второй выход которого соединен с вторым входом формировате ля импульса управления блоком коммутации, выход второго формирователя импульсов соединен с первым выходом блока управления, выходы которого с второго по десятый соединены соответственно с первым выходом первого формирователя импульсов, вторымр Е, Сирохман ор Подпис 576/58 Тираж 871 ВНИИПИ Государственного копо делам изобретений и о 3035, Москва, Ж, Раушска аказ .7 тета СССрытий 4 аб., д Филиал ППП "Патент", г. Ужгород, ул ктная Составитель О. РевинскРедактор Н, Данкулич Техред А.Ач1 вьмодом формирователя импульса конца" преобразования, вторым вьмодом фор,мирователя импульсов синхронизации, выходом блока формирования импульса обнуления памяти, третьим и четвертым вьмодами формирователя импульсов синхронизации, выходом формирователя импульса управления блоком коммутации, вторым выходом первого формирователя импульсов и вторым выходоМ блока формирования им 197085 пульсов начальной установки, первыйвторой, третий и четвертый входы блока управления подключены соответственно к третьему входу блокаформирования импульса обнуления па"мяти, входу формирователя импульса конца первого цикла, входу формирователя импульса конца преобразования, объединенному стретьим входомблока формирования импульсовначальной установки,и второмувходу переключателя.1 О 15 20 25 30 Э 5 Изобретение относится к вычислительной технике и технике связи и может быть использовано в системах дискретной обработки звуковых сигналов, например, в телерадиовещании. Цель изобретения - увеличение точности и уменьшение времени кодирования,На фиг. 1 изображена структурная схема устройства, на фиг. 2 - структурная схема блока формирования кода инерционной шкалы; на фиг, 3 -структурная схема блока управления; на фиг 4. - принципиальная электрическая схема аналоговой части устройства, яа фиг. 5 - принципиальная электрическая схема аналого-цифрового преобразователя (АЦП) и формирователя кода, на фиг. 6 - принципиальная электрическая схема блока определе ния кода мгновенной шкалы; на фиг.7- принципиальная электрическая схема блока формирователя кода инерционной шкалы, на фиг. 8 - принципиальная электрическая схема блока управления на фиг, 9 - характеристика квантования отсчетов звукового сигналаф на фиг. 10 - временные диаграммы импульсов, вырабатываемых в блоке управленияУстройство для кодирования звуковых сигналов с инерционнымкомпан.дированием (фиг. 1) содержит последовательно соединенные источник 1 . сигнала усилитель 2, блок 3 дискретизации и хранения и блок 4 масштабного усиления, вход и выход которого подключены к входам блока 5 коммутации, аналого-цифровой преоб 2разователь (АЦП) 6, формирователь 7 кода, блок 8 смещения уровня,. блок 9 определения кода мгновенной шкалы (ИШ), блок 10 формирования кода. инерционной шкалы (ИЩ) и блок 11 управления. Первые выходы 12 АЦП б подключены к первым входам 13 формирователя 7 кода, вторые входы 14 которого объединены с управляющими входами блока 4 масштабного усиления и подключены к первым выходам 15 блока 10 формирования кода. ИШ,второй выход 16 которого соединенс первым входом 17 блока 11 управления, первый и второй выходы 18 и 19 последнего подключены к соответствующим управляющим входам блока 3 дискретизации и хранения, третий вьмод 20 блока 11 управления соединен с третьим входом 21 формирователя 7 кода. Выходы 22 - 25с четвертого по седьмой блока 11подключены к входам 26 - 29 с пер"вого по четвертый блока 10, пятыйвход 30 которого объединен с первымвходом блока 9 определения кодаИШ и подключен к второму выходу 31АЦП 6, вторые входы блока 9 соединены .с соответствующими первьаеи выходами 12 АЦП 6, к первому входу 32которого через блок 8 смещения уровня подключен выход блока 5 коммутации, а выходы блока 9 подключенык шестым входам 33 блока 1 О. Восьмойвыход 34 блока 11 управления соединен с управлякюцим входом блока 5коммутации, а девятый 35 и десятый36 выходы подключены к второму 37и третьему 38 входам АЦП 6, третий39 и четвертый 40 выходы которогосоединены с вторым 41 и третьим 42входами блока 11 управления, четвертый вход 43 которого подключен к шине 44 внешней синхронизации.Блок 10 Формирования кода ИШ(Фиг. 2) содержит блок 45 начальнойустановки, блок 46 Формирования импульса. смены знака, элемент НЕ 47,первый 48 и второй 49 блоки элементов И и соединенные последовательнопо первым выходам и входам блок 50самоблокировки памяти, блок 51 памяти признака, элемент И 52, блок 53уменьшения кода, третий блок 54 элементов И, блок 55 элементов ИЛИ регистр 56 кода ИШ, цифровой ком-.паратор 57 и элемент ИЛИ 58, выходкоторого подключен к второму входублока 51 памяти признака, выходкоторого соединен с первым входомблока 50 самоблокировки памяти.Второй выход цифрового компаратора57 подключен к второму входу элемента ИЛИ 58 и через элемент НЕ 47 -к второму входу элемента И 52, третий выход компаратора 57 соединенс вторым входом третьего блока 54и первым входом второго блока 49элементов И, Вторые входы последнего подключены к соответствующимпервым выходам регистра 56, которые соединены с первыми выходами15 блока 10 формирования кода ИШ.Входы 26 - 30 с первого по пятыйблока 10 подключены соответственно,к второму входу регистра 56, третьему входу блока 51, второму входублока 50 и первому и второму входам блока 46, первый выход которогосоединен с третьим входом третье-.го блока 54 элементов И и вторымвыходом 16 блока 10, шестые входы33 которого подключены к вторымвходам компаратора 57 и первымвходам первого блока 48 элементовИ, второй вход последнего соединен с первым выходом компаратора 57.Выходы первого 48 и второго49 блоков элементов И подключенык вторым и третьим входам блока 55элементов ИЛИ, третий вход блока 49соединен с вторым выходом блока 46формирования импульса смены знака,а третий вход регистра 56 кода ИШподключен к выходу блока 25 начальной установки,Блок 11 управления (Фиг. 3) содержит формирователь 59 импульсауправления блоком коммутации, Фор 4мирователь 60 импульса конца первого, цикла, блок 61 формирования импульса обнуления памяти, соединенные последовательно по первым выходам и входам формирователь 62 импульса конца преобразования, генератор 63 тактовых импульсов и первый формирователь 64 импульсов и соединенные последовательно по первым выходам и входам задающий генератор 65 импульсов, переключатель 66, второй формирователь 67 импульсов, триггер 68 завершения первого цикла, блок 69 формирования импульсов начальной установки и. формирователь 70 .импульсов синхронизации, первый выход которого подключен к второму входу триггера 68, второй выход которого соединен с первым входом 1197085 5 1 О 15 20 блока 61. Второй вход Последнего в месте с вторым входом блока 69 .подключены к первому выходу формирователя 60, второй выход которогосоединен с первым входом формирователя 59. Второй вход последнего.объединен с вторым входом генератора 63 и подключен к выходу второ,го формирователя 67 импульсов, соединенному с первым выходом 18 блока 11 управления. 25 30 Выходы 19, 20., 22 - 25, 34 - 36со второго по десятый блока 11управления подключены соответственнок первому выходу первого формирователя 64 импульсов, второму выходу формирователя. 62, второму выходуформирователя 70, выходу блока 61,третьему и четвертому выходам формирователя 70, выходу формирователя59, второму выходу первого формирователя 64 импульсов и второму выходу блока 69. Входы 17, 41, 42 и 44с первого по четвертый блока 11управления соединены соответственнос третьим входом блока 61, входомФормирователя 60, входом формирователя 62, объединенным с третьимвходом блока 69 и вторым входомпереключателя 66.В качестве примера реализацииустройства для кодирования:звуковых сигналов с инерционным компан дированием приведена койкретнаяпринципиальная схема (фиг. 4 - 8).55 Источником 1 сигнала может. служить микрофонный усилитель, магнитофон, электропроигрывающее устройство и пр, Усилитель 2 содержит(выходы регистра 88) 0 0 .0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 0 1 1 0 1. 0 0 1 0 0 1 1 О 1 0 1 О 1 11 1 О О1 1 01 1 .1 01 1 0 0 0 0 0 усилительный каскад 71 (фиг. 4), собранный на микросхеме типа К 553 УД 1 А, и пассивный трехзвенный ЬС-фильтр 72 Кауэра 7-го порядка. Усилительный каскад 71 предназначен для согласования динамического1 диапазона звукового сигнала (ЗС) ис точника 1 с диапазоном квантования устройства, а фильтр 72 - для подавления высокочастотных составляющих ЗС, лежащих вьппе половины частоты дискретизации (24 кГц) . Блок 3 дискретизации и хранения со-, держит два буферных каскада 73 и 74,15 триггер-формирователь 75 импульса дискретизации (элементы типаК 531 ЛАЗ), формирователь 76 импульса управления ключом 77 на дифференциальном каскаде 78, 79 и запоминающий конденсатор 80.20 Входной буферный каскад 73 на микросхеме типа К 544 УД 2 работает в режиме повторителя напряжения. . Высокое входное сопротивление выходного буферного каскада 74 на микросхеме типа К 574 УД 1 А предотвращает разряд запоминающего конденсатора 78 в период времени хранения отсчета .ЗС.Стабилитроны в базовых цепях дифференциального каскада 78, 79 служат для согласования уровней .ТТЛ сдиапазоном работы ключа 77. Блок 4 масштабного усиления собран . на операционном усилителе 81 типа К 544 УД 2 А с резистивной матрицей 82 типа 301 НРЗ и ключами 83 на микро. схеме типа К 590 КНЬ в цепи обратной связи. Резисторы матрицы 82 КК соединены таким образомчто обра-. зуют делитель выходного напряжения" операционного усилителя 81 в соотношении 1-2-4-8. Для согласования уровней ТТЛ с уровнями КМОП ключей 83 используют элементы НЕ 84 серии45 К 155 ЛНЗ с открытым коллектором. Блок.5 коммутации собран на микросхеме 85 К 590 КН 6 с согласователем уровней ТТЛ-КМОП на элементе. 86 типа К 155 ЛНЗ. Блок 8 смещения уровня реализован на операционном усилителе 87 типа К 574 УД 1 А, работающем в режиме ,суммирования напряжения отсчетовсигнала с половиной опорного напряжения АЦП б.55АЦП 6 (фиг. 5) построен по широко известной схеме последовательного приближения и содержит регистр 88 последовательных приближений на микросхеме типа К 155 ИР 17, цифро аналоговый преобразователь (ЦАП) 89 типа К 1108 ПА 1 А и компаратор 90 типа К 521 САЗБ.Особенностью данной схемы является включение компаратора 90 в режиме сравнения токов. Диоды на его входе защищают компаратор 90 от перегрузки. формирователь 7 кода содержит регистр 91 из четырнадцати Р-триггеров (три микросхемы К 155 ТИ 5 и половину микросхемы К 155 ТИ 7). Блок. 9 определения кода. мгновенной шкалы (фиг. 6) реализован на логических элементах серии К 155 типаК 155 ЛП 5, К 155 ЛА 4 и К 155 ЛАЗ.Показанное включение логических элементов реализует следующую таблицу истинности. 1 р 2 р Зр 4 р 1 р 2 р 0 0,0 0 0 0Блок 10 формирования кода инер= ционной шкалы выполнен на микросхемах серии К 155. Принципиальная электрическая схема блока приведена на фиг. 7. Первый 48, второй 49 и тре тий 54 блоки элементов И и блок 55 элементов ИЛИ выполнены на микро. схемах 92 и 93 типа К 155 ЛРЗ, а также на третьем и четвертом элементах микросхемы 94 типа К 155 ЛАЗ. Регистр 56 кода инерционной шкалы выполнен на микросхеме 95 типа К 155 ТМ 7. Блок 45 начальной установки содержит конденсатор 96 и регистр 97, Цифровой компаратор 57 выполнен на микросхеме 98 типа К 155 ИМЗ и первом элементе микросхемы 99 типа К 155 ЛАЗ Элемент НЕ 47 реализован на втором элементе той же микросхемы 99Элемент ИЛИ 58 реализован на третьем элементе микросхемы 99. Блок 51 памяти признака, выполнен на первом Р-триггере микросхемы 100 типа К 155 ТМ 2. Блок 50 самоблокировки па" мяти реализован на втором элементе микросхемы 94 типа К 155 ЛИ 1. Элемент И 52 выполнен на первом элементе той же микросхемы 94. Блок 53 уменьшения кода реализован на сумматоре 101 типа К 155 ИМЗ и двух элементах микросхемы 102, Блок 46 формирования импульса смены знака содержит второй П-триггер микросхемы 100 типа К 155 ТМ 2, два ждущих мультивибратора, собранных на микросхеме 103 типа К 155 АГЗ с соответствующими время .задающими элементами 104 - 107 идва элемента 2 И-НЕ микросхемы 102, служащих для смешивания импульсов смены знака от положительных и отрицательных фронтов смены кода первого разряда; Блок 11 управления также в основном выполнен на микросхемах 155 серии (фиг. 8). Задающий генератор 65 импульсов выполнен по схеме мультивибратора на элементах 108 и 109 микросхемы типа К 155 ЛАЗ с время- задающими элементами 110-112, Второй формирователь 67 импульсов выполнен в виде ждущего мультивибратора на микросхеме 113 типа К 155 АГЗ с времязадающими элементами 114 и 115 ,используется инверсный выход мультивибратора. Генератор 63 тактовых импульсов содержит КЗ-триггер запуска на первом 116 и втором 117 элементах микросхемы типа К 155 ЛАЗ,непосредственно тактовый генератор,выполненный на третьем элементе118 той же микросхемы с линией 119задержки типа ММЛЗ-М,5/300 в цепи 5обратной связи и формирователь фронтов на первом элементе 120 микросхемы типа К 155 ЛИ 1. Первый формиро- .ватель 64 импульсов выполнен намикросхеме 121 с времязадающими 10 элементами 122, 123 аналогично формирователю 67 импульсов. Формирователь 59 импульса управленияблоком коммутации и триггер 68 завершения цикла представляют собойКБ-триггеры, выполненные на эле-.15ментах 124-127 микросхемы типаК 155 ЛАЗ. Блок 69 формированияимпульсов начальной установки содержит второй элемент 2 И 128 микросхемы типа К 155 ЛИ 1 и четвертыйэлемент 2 И-НЕ 129 микросхемы типаК 155 ЛАЗ. формирователь 70 импульсовсинхронизации содержит ждущий.мультивибратор на микросхеме 130типа К 155 АГЗ с времязадающими 25элементами 131 и 132, линию 133задержки типа ММЛЗ-М,0/300 сотводом через О, 1 мкс и два формирователя.на элементах 134 и 135типа К 155 ЛИ 1; Формирователь 60импульсов конца первого цикла выполнен на микросхеме 136 типаК 155 АГЗ с времязадающей цепочкой137 - 139. Формирователь 62 импульсов конца преобразования выполнен 35. на микросхеме 140 аналогично. Блок61 формирования импульса обнуленияпамяти выполнен на элементе ЗИ-НЕ141 типа К 155 ЛА 4.Устройство работает следующим 40 образом.Аналоговый звуковой сигнал поступает на вход усилителя 2 (фиг.1где усиливается таким образом,чтобы использовалась вся шкала 45 квантования, и ограничивается по,спектру с целью предотвращенияперекрытия боковых полос ЗС придискретизации, после чего поступаетна вход блока 3 дискретизации и.50 хранения. Далее работа устройствадля кодирования звуковых сигналовпроисходит следующим образом.При подаче питающего напряжения+5 В конденсатор 96 в блоке 45 на чальной установки (фиг. 7) не можетмгновенно зарядиться до напряжения,равного уровню логической единицыцепи 97, 96 выбрана такой, чтобына К-входе П-триггеров 95 регистра 56 кода ИШ оставался уровеньлогического нуля на время, достаточное для установки триггеровв нулевое состояние. Таким образом,в начале работы устройства науправляющем входе блока 4 масштабного .усиления всегда устанавливается код "00", соответствующийсамой точной шкале квантования(фиг.9), что предотвращает грубоеквантование ЗС в начальный моментработы. Задающий генератор 65 импульсов (фиг. 3,8) запускается ина его выходе появляются прямоугольные импульсы с периодом20,8 мкс (48 кГц). Если переключатель 66 находится в верхнем положении (фиг.8), то эти импульсы поступают на вход второго формирователя 67 импульсов, где по их положительному фронту вырабатываютсякороткие (длительностью 150 нс) отрицательные импульсы (фиг.10 а,б),Наличие второго формирователя 67импульсовобеспечивает возможностьвнешней синхронизации устройствасо входа 44 любым импульсным сигналом с частотой 48 кГц. Короткийотрицательный импульс поступаетодновременно на вход блока 3 диск"ретизации и хранения (выход 18 блока11) как импульс начала выборки (ИНВ),на второй вход генератора 63 такто.вых импульсов, на первый вход формирователя 59 импульса управленияблоком коммутации и на первый входтриггера 68 завершения первого цикла. С приходом ИНВ на первый управляющий вход блока 3 дискретизации и хранения (фиг. 4) КБ-триггер 75 устанавливается в единичное состоя- ние. На коллекторе транзистора 79 появляется потенциал + 15 В. Ключ 77 открывается и конденсатор 80 заряжается до напряжения ЗС и далее отслеживает его изменения. Одновременно (фиг. 3, 8) КЯ-триггер в формирователе 59 импульса управления блоком коммутации (фиг. 10 д) и триггер 68 завершения первого цикла устанавливаются в единичные состояния. При этом уровень логичес". кой единицы с восьмого выхода 34 блока 11 управления поступает на управляющий вход блока 5 коммута 25 30 состояние и на входе элемента 118возникает уровень логической единицы. Генератор 63 тактовых импульсовначинает вырабатывать прямоугольные импульсы в виде меандра, которые через элемент 120 поступаютна вход первого формирователя 64импульсов. В последнем по отрицательным фронтам меандра Формируются короткие. положительные и отрицательные импульсы длительностьюю 150 нс и периодом в 1 мкс(фиг.10 в) "Первый отрицательный импульс является импульсом конца выборки (ИКВ),который с второго выхода 19 блока 45 11 управления поступает на второйуправляющий вход блока 3 дискретизации и хранения (фиг. 4). При этомКЗ-триггер 75 возвращается в нулевое состояние, потенциал на кол лекторе транзистора 79 снижаетсядо минус 9 В, ключ 77 закрывается.Напряжение сигнала, оставшееся наконденсаторе 80, хранится в течениевсего времени преобразования от счета.Напряжение отсчета сигнала с выхода блока 3 дискретизации и хранения (Фиг. 1) поступает на сигналь 5 1 О 15 20 ции (фиг. 1,4), который подключает выход блока 3 дискретизации и хранения к входу блока 8 смещения уровня, а уровень логической единицы с выхода триггера 68 завершения первого цикла поступает на первый вход блока 69 формирования импульсов начальной установки (фиг. 8), элемент 129, на выходе которого устанавливается уровень логической единицы. Последний поступает на соответствующий вход элемента 128, на другом входе которого установлен потенциал логического нуля, приходящий с четвертого выхода 40 АЦП 6 (фиг. 5) . На втором выходе блока 69 Формирования импульсов начальнойустановки устанавливается уровень логического нуля (фиг10 г), который поступает с десятого выхода 36блока 11 уйравления на третий вход 38 АЦП 6 (фиг, 5), подготавливая таким образом регистр 88 последовательных приближений к работе. Отрицательный импульс с выхода второго 67 формирователя импульсов поступает на второй вход генератора 63 тактовых импульсов (Фиг. 8). При этом К 5-триггер на элементах 116 и 117 устанавливается в единичное11 11ный вход блока 4 масштабного усиления и на второй вход блока 5коммутации, с выхода которого отсчетпоступает на вход блока 8 смещенияуровня, где складывается с половинойопорного напряжения АЦП 6Сдвинутое по уровню напряжение отсчета ЗСс выхода блока 8 поступает напервый вход 32 АЦП 6. Первый тактовый импульс, поступающий на второйвход 37 АЦП 6 (фиг. 5) с девятоговыхода 35 блока 11 управления(фиг. 5) таким образом, что на выхо.де. первого разряда Регистра или навходе первого, разряда ЦАП 89 появляется уровень логической единицы,. а на остальных разрядных входах ЦАП 89 устанавливаются уровнилогического нуля. Через резисторК, находящийся внутри ЦАП 89и суммирующий весовые токи ЦАП и токвходного сигнала 17, приходящегос выхода блока 8 смещения уровняна первый вход 32 АЦП 6, начинаеттечь разностный ток 1 в 1 ,. где 1 ток отсчета сигнала, 11 - весовойРток первого разряда, который вызывает соответствующее падение напряжения, прикладывающееся к входу компаратора 90. Если Пс ъ Б (1 ) 1 ),то дО = (1 - 1 ). КО, на выходекомпаратора 90 устанавливаетсяуровень логической единицы. ЕслиЦ с Ц (1 с 1), т.е. Ь У с О,1 р с (рна выходе комйаратора 90 устанав -ливается уровень логического нуля.В любом случае информация с выходакомпаратора 90 поступает на Э-входрегистра 88 последовательных прибли -жений АЦП 6 (Фиг. 5). С приходомвторого тактового импульса с блока 11 управления на второй вход37 АЦП 6,(фиг, 1) эта информациязаписывается в регистр 88 и одновременно на.выходе второго разряда регистра 88, а следовательно,и на входевторого разряда ЦАП 89,появляется уровень логической единицыЕсли 17 с 01 р+ Пя р(1 с 11 р Мто на выходе компаратора 90 появляется уровень логической единицы, аесли Бс с 0 + 0 Р, то устанавли 4 рвается уровень логического нуля.В любом случае информация с выходакомпаратора 90 поступает на Р-входрегистра 88 и записывается в негос приходом третьего тактового импуль 97085 12са, который одновременно включает весовой ток третьего разрядаЦАП, Подобным. образом определяются тре 5 102030 35 40 455055 тий и четвертый разряды кодового слова в первом цикле преобразования,С приходом пятого тактового им-. пульса информация о значении четвертого разряда кода записывается в регистр 88 и одновременно отрицательный Фронт импульса установки пятого разряда ЦАП 89 поступает с третьего выхода 39 АЦП 6 на второй вход 41 блока 11 управления (фиг.8) По этому фронту в формирователе 60импульсов конца первого цикла вырабатываются два импульса длительностью порядка 150 нс. Отрицательный импульс поступает на первый вход Форми рователя 59 импульса управления блоком коммутации, КЗ"триггер последнего устанавливается в нулевое состояние, и уровень логического нуля с восьмого выхода 34 блока 11 управленияпоступает на управляющий вход блока5 коммутации (фиг. 1), который подключает вход блока 8 смещения уровня к выходу блока 4 масштабного усиления. Положительный импульс с другого выхода формирователя 60 импульса конца первого цикла (фиг.8) поступает на блок 61 формирования импульса обнуления .памяти и ца второй вход блока 69 формирования импульсов начальнойустановки. На выходе элемента 129 возникает уровень логического нуля, который устанавливает уровень логического нуля на выходе элемента 128, а. следовательно, и на третьем входе 38 АЦП 6 (вход установки). Одновременно отрицательный фронт с первого выхода ,(элемент 129) блока 69 формирова- ния импульсов начальной установки поступает на вход формирователя 70 импульсов синхронизации. Мультивибратор 130 формирует два импульсадлительностью150 нс. Положительный импульс с седьмого выхода 25 блока 11 управления (фиг. 1) поступает на четвертый вход блока 10 фор - мирования кода ИШ а отрицательный импульс поступает на вход линии )33 задержкиДалее начинается определение кода.инерционной шкалы. Второй, третий и четвертый разряды кода с первых выходов 12 АЦП 6 поступают на вторые входы блока 9 определения кода мгновенной шкалы, на первыйФ13 1 вход которого со второго выхода 31АЦЛ 6 подается инверсный первый раэряд. В соответствии с таблицей истинности, приведенной выше, блок9 определения кода мгновенной шкалывырабатывает двухразрядный код,который поступает на шестые входы33 блока 10 Формирования кода ИШ(фиг. 2), т.е. на вторые входы цифрового компаратора 57 и на первыевходы первого блока 48 элементов ИПричем в начальный момент временимогут сложиться две ситуации:1) код мгновенной шкалы равенкоду инерционной шкалы, записанному в регистр 56 кода инерционной2) код мгновенной шкалы большекода инерционной при условии, чтотекущий отсчет сигнала не являетсяпервьщ после изменения его полярности,ровой компаратор 57 на первом выходевыдает уровень логической единицы,а на втором и третьем выходах устанавливается уровень логическогонуля. При этом (фиг. 2) на первомвходе элемента ИЛИ 58 на второмвходе первого блока 48 элементов Иустанавливаются уровни логическойединицы, На втором входе элементаИЛИ 58 и на входе элемента НЕ 47 1Тогда в первом случае цифровой компаратор 57 выдает с первого выхо да (выход Р микросхемы 98, фиг.7) на элемент ЙЛИ 58 и на первый блок 48 элементов И уровень логического нуля, с третьего выхода (на фиг. 7 выход второго элемента микросхемы 99) на второй и третий блоки 49, 54 элементов И - уровень логической единицы, а со второго выхода первый элемент микросхемы 99 на элемент ИЛИ 58 и элемент НЕ 47 уровень логического нуля При этом первый блок 48 элементов И оказывается запертым, на выходе элемента ИЛИ 58 (выход третьего элемента микросхемы 99) появляется уровень логической единицы, на выходе второго .элемента НЕ 47 микросхемы 99 - уровень логического нуля.В это время с шестого выхода 24 блока 11 управления (фиг1) на третий вход 28 блока 10 формирования кода инерционной шкалы, т.е. на второй вход блока 50 самоблокиров" ки памяти, который открыт,. поступа" ет положительный синхроимпульс дли тельностью 150 нс (см. Фиг. 10 з). Блок 51 памяти признака записывает информацию с выхода элемента ИЛИ 58 и на его выходе появляется уровень логического нуля который запирает блок 50 самоблокировки памяти и элемент И 52. Таким образом,в блоке 51 памяти признака записана информация о том, что код мгно: 25 30 устанавливаются уровни логическогонуля. На первом входе второго блока49 элементов И и. на втором входетретьего блока 54 элементов И также 35устанавливаются уровни логическогонуля, запирая их. Уровень логической единицы с выхода элемента ИЛИ 58поступает на второй вход блока 51памяти признака, куда записывается с 40приходом синхроимпульса с шестоговыхода 24 блока 11 управления на третий вход 28 блока 10 Формирования кода ИШ. При этом на первый вход блока 50 саиоблокировки памяти подается уровень логического нуля предотУвращая возможность прохождения синхро"импульса на синхровход блока 51памяти, признака. Уровень логическогонуля с выхода блока 51 поступаетна первый вход элемента И 52, на 50выходе которого также устанавливаетсяуровень логического нуля, предотвращая возможность уменьшения кода инерционной шкалы до момента смены полярности отсчета. Таким образом, в блок51 памяти признака записана информация о тои, что код мгновенной шкалыбыл хотя бы раз больше кода инерционной шкалы, и открыт первый блок 197085 14венной шкалы был равен коду инерционной шкалы, а на третий входтретьего блока 54 элементов И спервого выхода блока 46 формирования импульса смены знака подаетсяуровень логического нуля, запирая егоПоэтому через 100 нс, с приходомвторого синхроимпульса с четвертоговыхода 22 блока 11 управленияна 10 первый вход 26 блока 10 формированиякода инерционной шкалы (фиг.10 и),код с выходов регистра 56, кодаинерционной шкалы через открытыйвторой блок 49 элементов И, блок 55элементов ИЛИ поступаетна первыевходы регистра 56 и записывается внего, Во втором случае, когда кодмгновенной шкалы больше кода инерционной шкалы, записанного первоначально в регистре 56 кода ИШ, циф

СмотретьЗаявка

3771600, 13.07.1984

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

АНИСИМОВ СЕРГЕЙ ВАСИЛЬЕВИЧ, ВАНДЕ-КИРКОВ ВЛАДИМИР ВАДИМОВИЧ, МАТВЕЕВ НИКОЛАЙ ЕВГЕНЬЕВИЧ

МПК / Метки

Метки: звуковых, инерционным, кодирования, компандированием, сигналов

Опубликовано: 07.12.1985

Код ссылки

<a href="https://patents.su/20-1197085-ustrojjstvo-dlya-kodirovaniya-zvukovykh-signalov-s-inercionnym-kompandirovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для кодирования звуковых сигналов с инерционным компандированием</a>

Предыдущий патент: Преобразователь код-напряжение

Следующий патент: Система связи с дельта-модуляцией

Случайный патент: Преобразователь угла поворота вала в код