Дельта-декодер с экспандированием

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 594583

Автор: Шпигель

Текст

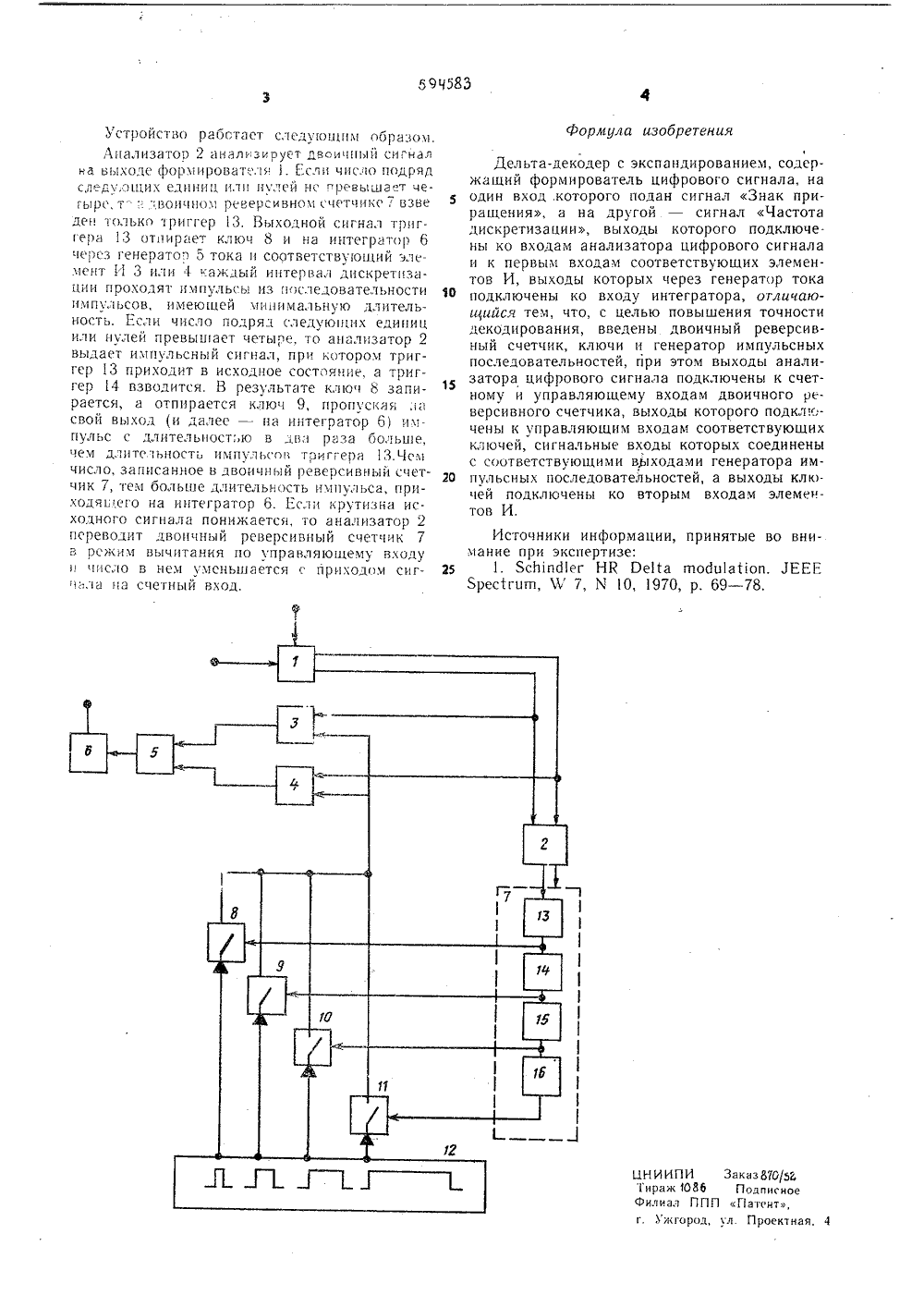

"к.: й 1 БА Союз Советских Социалистических Респ)блин(23) Приоритет сударотвенный комете авета Миннотров СССР по делам нэооретеннйи открытий 3) Опубликовано 25,02.78, Бюллет К 621,376) Дата опубликования описания Е 5.0178(72) Авт Р, Шпигел етен нтральный научно-исследовательский институт связ(71) Заявител АНДИРОВАНИЕМ входам соответстю ю.11 ОЧЕИ, СЦ ГЦ,1,1 ЬЦ.Ц. ны с соответствчОццм ЦМПУЛЬСНЫХ ПОС, ЕДОН;1 1 СЛЮЦСИ ПОДКЛК)ЦГМЫ К 1 тов И. входы ковь ходамт льносте ГГОРЫЧ СОЕДЦ торыхгене 11, а ход х ртор ыходы элемец.я схех 1 ельта-декодер с экспандцроваццем годер.жцт формцровате,;ь 1 цифрового сцгнл, вью ходы которого НОдключены ко входа)1 ац 1 гн 131 тора 2 цифрового сигнала ц к первым вход;1): соответствмющих элементов 11 3 ц -1, вьходыкоторых цсрез гсцсратор ) " Ок цодклоцец,ко входх интеграторы 6;воцццыц рсверсцвцый сцстцик 7, клочи 8 - 11 и хцсртор 1" цхНхсцых последовательностей, црц этом цьходылцзатора 2 ц 1)рОВОГО Гцгц)л цд.лкчс 11 , счетному ц управляюцсхх входам двоцццсц реверсивного счетццка 7, в 1: оды которог подключены к управляк)ццм входам соотвстстнук- шцх клочей 8 - 11, сигнальные входы которых соединены с соответствующими ньходми генератора 2 импульсных последов 1 тсл ц)сгсй.а выходы ключей 8 -подключены ко ц-х)р:ч входам заемеТов И 3 ц -. Нрц это) двоичный реверсивный счетчик 7 с, тоцт цз цепочки трг 25 геров 1316. 54) ДЕЛЬТА-ДЕКОДЕР С Изобретение относится к устройствам связи и может использоваться при построении кодеров и декодеров в калах связи, образованных ме годом дельта-модуляци.Извес ген догьта-декодер, содержащий формц роватсль цифрового сигнала, анализатор цифрового сц нала, элементы И, амплитудный модулятор, амплитудно-щиротный преобразовагель, генератор тока и интегратор 1.Однако известный дельта-декодер имеет недостаточную точность декодирования.Цель изобретения - повышение точности декодирования.Для этого в дельта-декодер с экспандированием, содержащий формирователь цифрового сигнала, на один вход которого подан сиг.нал Знак прирацения, а на другой - сигнал Частота дискретизации, выходы которого подключены ко входам анализатора цифрового сигнала и к первым входам соответствующих элементов И, выходы которых через генератор тока подключены ко входу интегратора, введены двоичный реверсивный счетчик, ключи и генератор импульсных последовательностей, при этом выходы анализатора цифрового сигнала подклоцены к счетному и управляющему входам двоичного реверсивного счетчика, выходы которого подключены к управляюццм ертеже дана структурная элскт)1 ца предлагасчого устройств.Устройство работает следующим образом.Анализатор 2 нлидирует двои ный сигнал иа выходе формирователя 1. Если число подряд следу,ощих единиц илн нулсй нс гргвь,ша=т чегырс, т .воичном реверсивном счетчике 7 взве ден только т риггер 3. Выходной сигнал триггеры 13 отпирает ключ 8 и на интегратор 6 через генератор 5 тока и соответствующий элемент И 3 или 4 каж сый интервал дискретизации проходят импульсы из нс 1 следовательности импульсов, имеющей минимальную длительность. Если число подряд следуюнсих единиц или нулей превышает четыре, то анализатор 2 выдает импульсный сигнал, при котором триггер 13 приходит в исходное состояние, а триггер 4 взводится. В результате клю с 8 запирается, а отпирается ключ 9, пропуская ны свой выход (и далее - на интегратор 6) импульс с длительностью в свраза больше, чем длительность импульсов триггеры 13.Чсм число, записанное в двоичный реверсивный счетчик 7, тем больше длительность импульса, приходяпсего на интегратор 6. Если крутизны исходного сигнала понижается, то анализатор 2 переводит двоичный реверсивный счетчик 7 в режим вычитания по управляющему входу и число в нем уменьшается с приходом сигцала на счетный вход. Формула изобретенияДельта-декодер с экспандированием, содержащий формирователь цифрового сигнала, на один вход .которого подан сигнал Знак приращения, а на другой - сигнал Частота дискретизации, выходы которого подключе.ны ко входам анализатора цифрового сигнала и к первым входам соответствующих элементов И, выходы которых через генератор тока подключены ко входу интегратора, отличающийся тем, что, с целью повышения точности декодирования, введены двоичный реверсивный счетчик, ключи и генератор импульсных последовательностей, при этом выходы анализатора цифрового сигнала подключены к счетному и управляюгцему входам двоичного реверсивного счетчика, выходы которого подключены к управляющим входам соответствующих ключей, сигнальные входы которых соединены с соответствующими выходами генератора им пульсных последовательностей, а выходы клкьчей подключены ко вторым входам элементов И,Источники информации, принятые во внимание при экспертизе:25 1. Ясйпдег НК с.уе са гпос 1 ца 11 оп. 1 ЕЕЕЬрес 1 гцтп, Ъ 7, Х 10, 1970, р. 69 - 78.ИИИПИ Заки 810(5 ираж 1086 Поапиено Филиал ППП Патеит,Ужгород, ул. Проект

СмотретьЗаявка

2379113, 02.07.1976

ЦЕНТРАЛЬНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ СВЯЗИ

ШПИГЕЛЬ АЛЬБЕРТ РАХМИЛЬЕВИЧ

МПК / Метки

МПК: H03K 13/22

Метки: дельта-декодер, экспандированием

Опубликовано: 25.02.1978

Код ссылки

<a href="https://patents.su/2-594583-delta-dekoder-s-ehkspandirovaniem.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-декодер с экспандированием</a>

Предыдущий патент: Функциональный аналого-цифровой преобразователь

Следующий патент: Тиристорный прерыватель постоянного тока

Случайный патент: Последовательный стабилизатор напряжения