Всесоюзная; п л т-” gt; amp; -5 •. -ir-r if: . патиlt; й1»-: . д; ., гс и.: , библ; -ю i; , . a •, vjii-c: is-xv. -i. v.;: ; ., -u

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 371579

Авторы: Виноградов, Горбачев, Жуков, Судьин

Текст

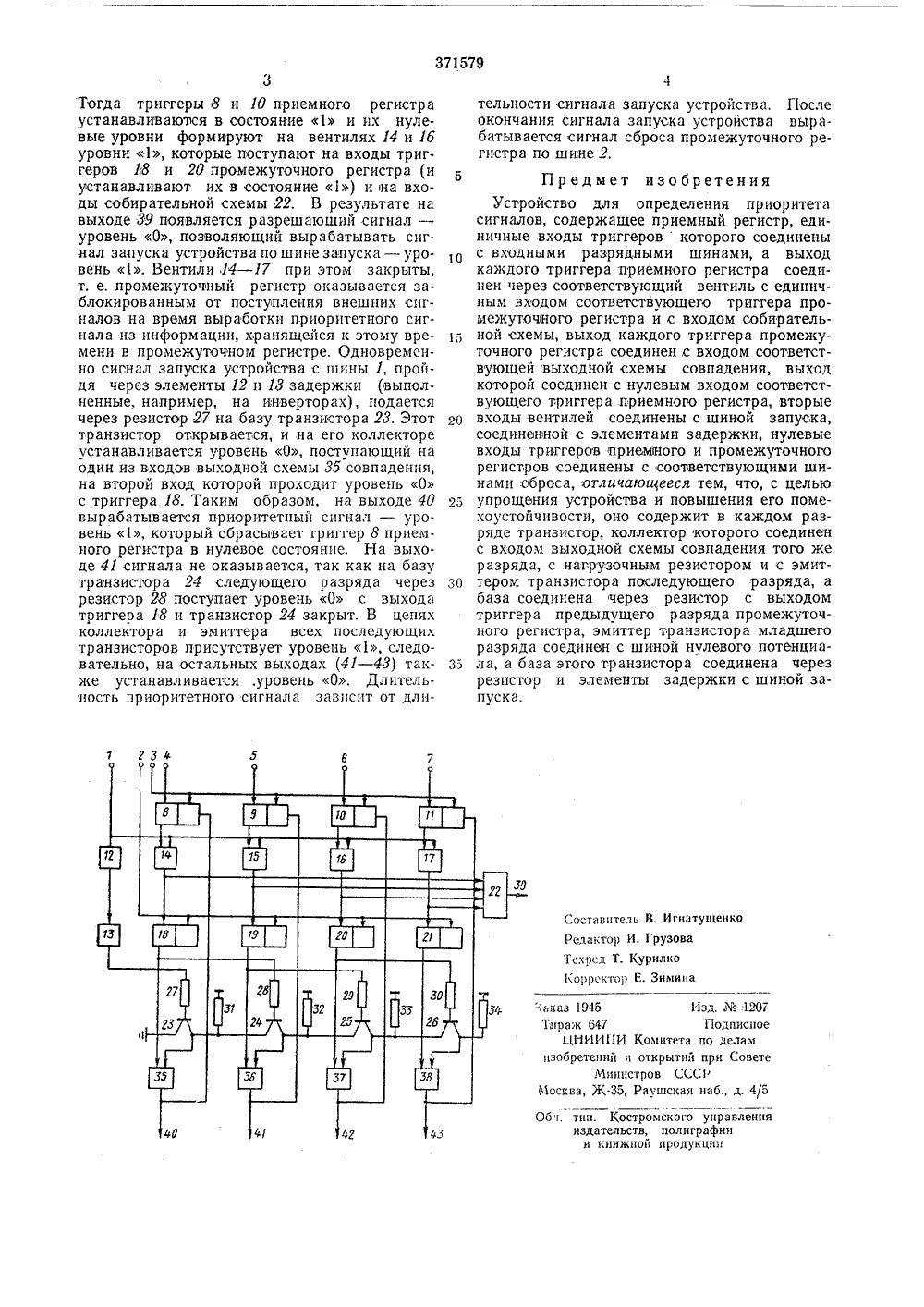

Сааз Советских Социалистических Республии32 529 ОПИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Зависимое от аит. сшдстельства-Заявлено 05.1.1971 ( 1609582/18-24)с присоединение. заявки-Приоритет -Опубликовапо 22 Л 1.1973. Бюллетень12Дата опубликования описашгя 7 Л.1973 М.Кл. С 06 918 Комитет оа делам изобретений и открытий ори Совете Министров СССРУДК 681,326.34 (038.8) Авторы изор Гси:я Ю. М, Виноградов, Ю. К, Судьин, Е. И. Жуков и О, С. Горбачев Заявитель ВСт ОБОЗНАЯ т;Б 1)Б.;: УС 1 РОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ПРИОРИ 1 ЕТА СИГНАЛОВ Изобретение относится к области автоматики и вычислительной техники и предназначено для приоритетного выбора одного сигнала из нескольких.Известно устройство для определения приоритета сигналов, содержащее приемныи и промежуточный регистры, схему сборки, схемы совпадения, инверторы. Однако в таком устройстве при определенных временных соотношениях между входными сигналами и сигналом запуска не исключена возможность выработки ложного сигнала одновременно с приоритетным (из-за конечного времени распространения сигнала поразрядной блокировки).Предложенное устройство отличается тем, что имеет в каждом разряде транзистор, коллектор которого соединен с входом выходной схемы совпадения того же разряда, с нагрузочным резистором и с эмиттером транзистора последующего разряда, а база через резистор - с,выходом триггера предыдущего разряда промежуточного регистра, Эмиттер транзистора младшего разряда соединен с шиной нулевого потенциала, а база этого транзистора через резистор и элементы задержки - с шиной запуска.Это позволяет упростить устройство и повысить его помехоустойчивость.На чертеже показана блок-схема устройства. Устройство содержит шины запуска 1, сброса промежуточного 2 и приемного 3 регистра, входные разрядные 4 - 7, приемный регистр на триггерах 8 - И, элементы,12 и 13 задержки, вентили 14 - 17, промежуточный регистр на триггерах 18 - 21, собирательную схему 22, транзисторы 23 - 26, резисторы 27 - 30, нагрузочные резисторы 31 - 34, выходные схемы 3 Б - 38 совпадения.1 О Устройство работает следующим образом.В исходном положении все триггеры приемного (8 - 11) и промежуточного (18 - 21) регистров находятся в нулввом состояшп, при котором правые плечи триггеров открыты, а ле вые закрыты. (Обратное состояние будем считать единичным). На шину 1 запуска устройства поступает уровень О. Вентили 14 - 17 нормально открыты, поэтому вся информация, записанная в триггерах 8 - 11 приемного реги стра, однозначно переписывается в тригеры18 - 21 промежуточного регистра. Так как в исходном положении приемный регистр сброшен в нулевое состояние, на выходе 39 (выход собирательной схемы 22) оказывается уро вень 1 (уровень 1 - напряжение, близкоек напряжению питания). На выходах 40 - 43 наблюдается уровень О, поскольку промежуточный регистр сброшен в нулевое состояние.Пусть на входные разрядные шины 4 и б Зе приходят одновременно сигналы уровня 1."аказ Тира зобнаб., д. 4/ Тогда триггеры 8 и 10 приемного регистра устанавливаются в состояние 1 и пх нулевые уровни формируют на вентилях 14 и 1 б уровни 1, которые поступают на входы триггеров 18 и 20 промежуточного регистра (и устанавливают их в состояние 1) и на входы собирательной схемы 22. В результате на выходе 39 появляется разрешающий сигнал - уровень О, позволяющий вырабатывать сигнал запуска устройства по шине запуска - уровень 1. Вентили 14 - 17 при этом закрыты, т. е. промежуточный регистр оказывается заблокированным от поступления внешних сигналов на время выработки приоритетного сигнала из информации, хранящейся к этому времени в промежуточном регистре. Одновременно сигнал запуска устройства с н 1 ины 1, пройдя через элементы 12 и И задержки (выполненные, например, на инверторах), подается через резистор 27 на базу транзистора 23. Этот транзистор открывается, и на его коллекторе устанавливается уровень О, поступающий на один из входов выходной схемы Зб совпадения, на второй вход которой проходит уровень О с триггера 18. Таким образом, на выходе 40 вырабатывается приоритетный сигнал - уровень 1, который сбрасывает триггер 8 приемного регистра в нулевое состояние. На выходе 41 сигнала не оказывается, так как на базу транзистора 24 следующего разряда через резистор 28 поступает уровень О с выхода триггера 18 и транзистор 24 закрыт. В цепях коллектора и эмиттера всех последующих транзисторов присутствует уровень 1, следовательно, на остальных выходах (41 - 43) также устанавливается, уровень 0. Длительность приоритетного сигнала зависит от длительности сигнала запуска устройства, После окончания сигнала запуска устройства вырабатывается сигнал сброса промежуточного регистра по ши:не 2,5 Предмет изобретенияУстройство для определения приоритетасигналов, содержащее приемный регистр, единичные входы триггеров которого соединены с входными разрядными шинами, а выход каждого триггера приемного регистра соединен через соответствующий вентиль с единичным входом соответствующего триггера промежуточного регистра и с входом собирательной схемы, выход каждого триггера промежуточного регистра соединен с входом соответствующеи выходной схемы совпадения, выход которой соединен с нулевым входом соответствующего триггера приемного регистра, вторые 20 входы вентилей соединены с шиной запуска,соединенной с элементами задержки, нулевые входы триггеров приемного и промежуточного регистров соединены с соответствующими шинами сброса, отличающееся тем, что, с целью 25 упрощения устройства и повышения его помехоустойчивости, оно содержит в каждом разряде транзистор, коллектор которого соединен с входом выходной схемы совпадения того же разряда, с нагрузочным резистором и с эмитзо тером транзистора последующего разряда, абаза соединена через резистор с выходом триггера предыдущего разряда промежуточного регистра, эмиттер транзистора младшего разряда соединен с шиной нулевого потенциа ла, а база этого транзистора соединена черезрезистор и элементы задержки с шиной запуска. л. тнп. Костромского унравлени издательств, полиграфии и книжной продукции

СмотретьЗаявка

1609582

Ю. М. Виноградов, Ю. К. Судьин, Е. И. Жуков, О. С. Горбачев

МПК / Метки

МПК: G06F 9/50

Метки: ir-r, is-xv, vjii-c, библ, всесоюзная, й1», патиlt

Опубликовано: 01.01.1973

Код ссылки

<a href="https://patents.su/2-371579-vsesoyuznaya-p-l-t-gt-amp-5-ir-r-if-patilt-jj1-d-gs-i-bibl-yu-i-a-vjii-c-is-xv-i-v-u.html" target="_blank" rel="follow" title="База патентов СССР">Всесоюзная; п л т-” gt; amp; -5 •. -ir-r if: . патиlt; й1»-: . д; ., гс и.: , библ; -ю i; , . a •, vjii-c: is-xv. -i. v.;: ; ., -u</a>

Предыдущий патент: Рекурсивно-однородная структура

Следующий патент: Логическое устройство

Случайный патент: Способ определения постоянной времени динамически настраиваемого гироскопа