Программируемый контроллер

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1453404

Авторы: Витковский, Склема

Текст

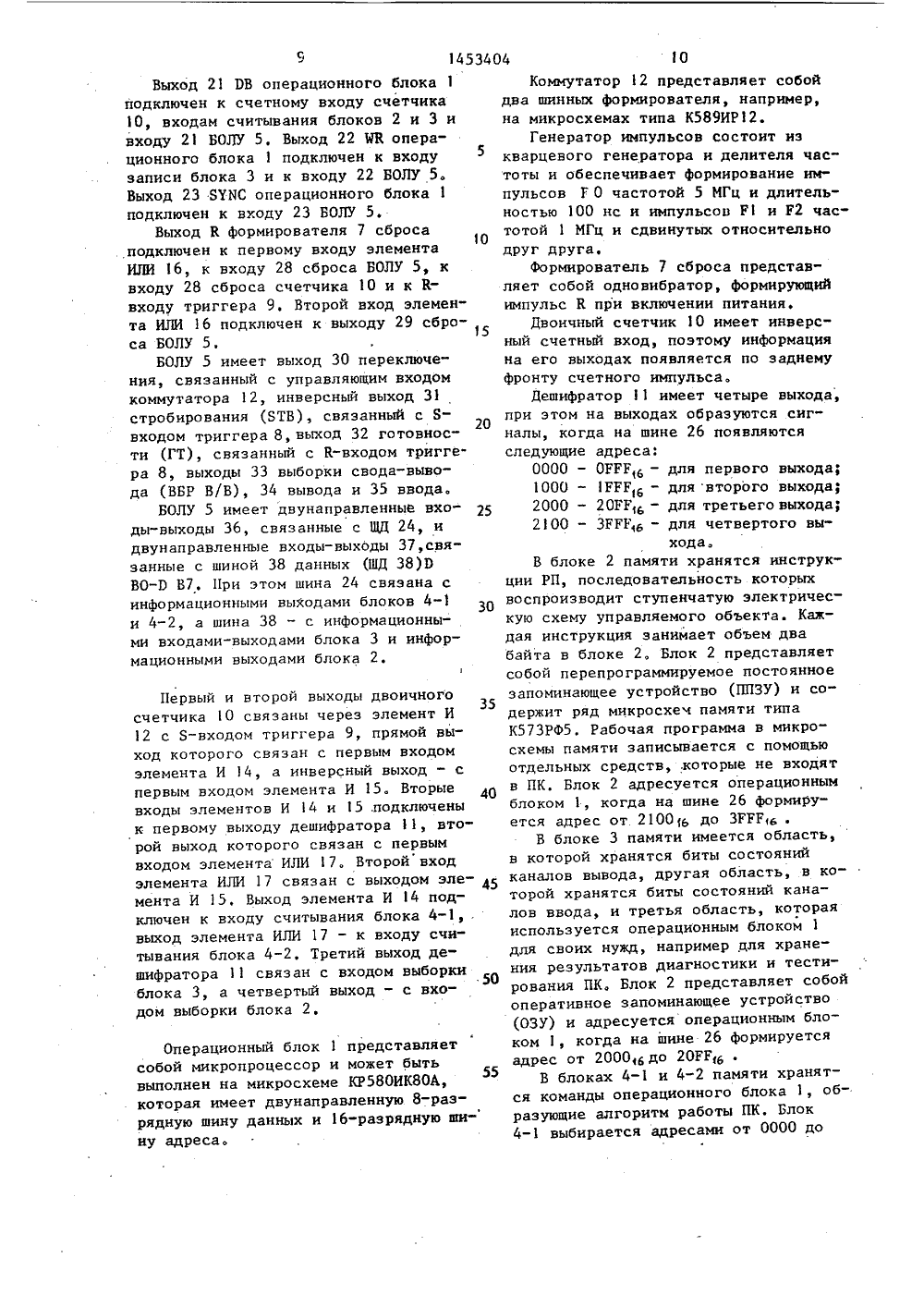

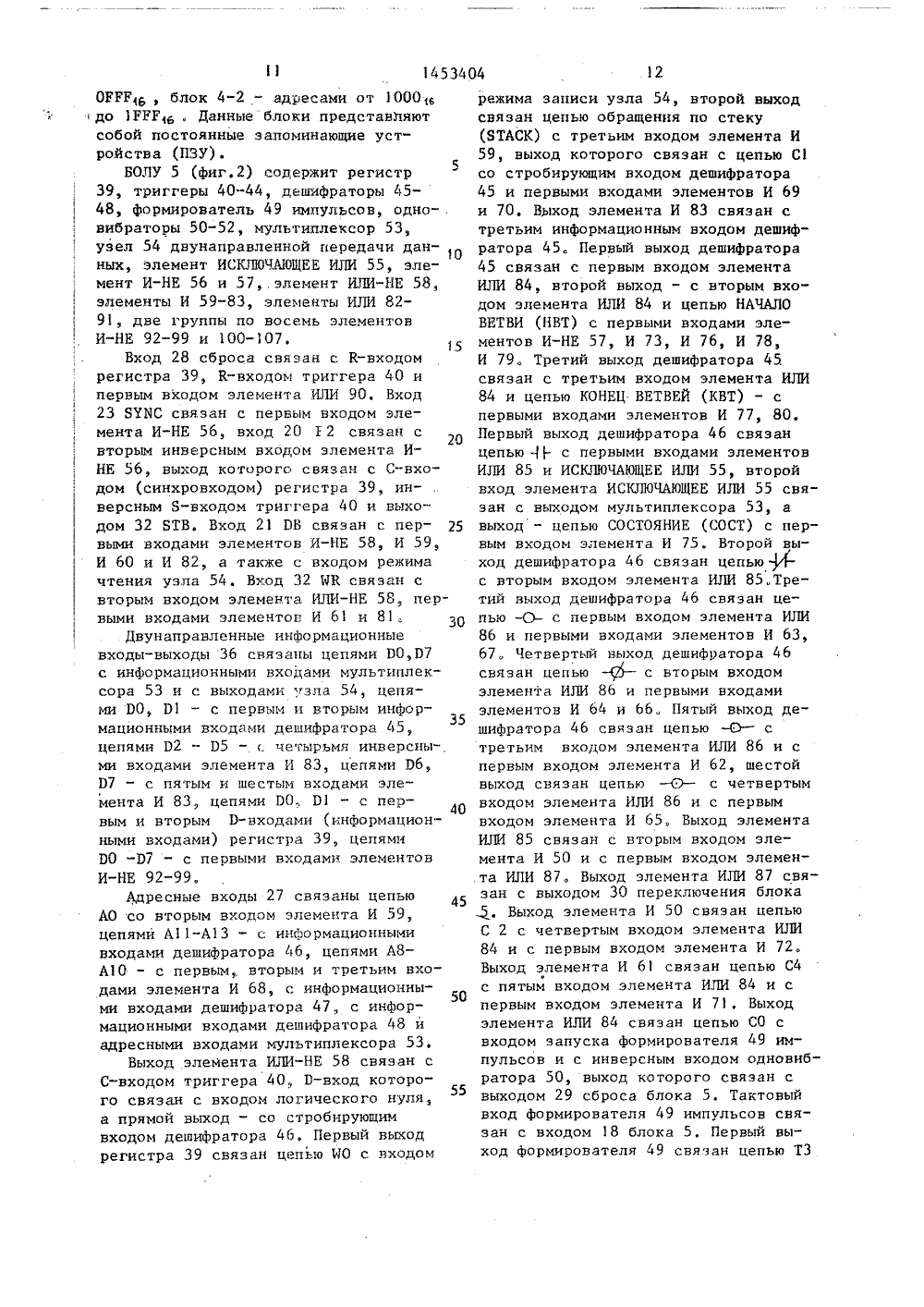

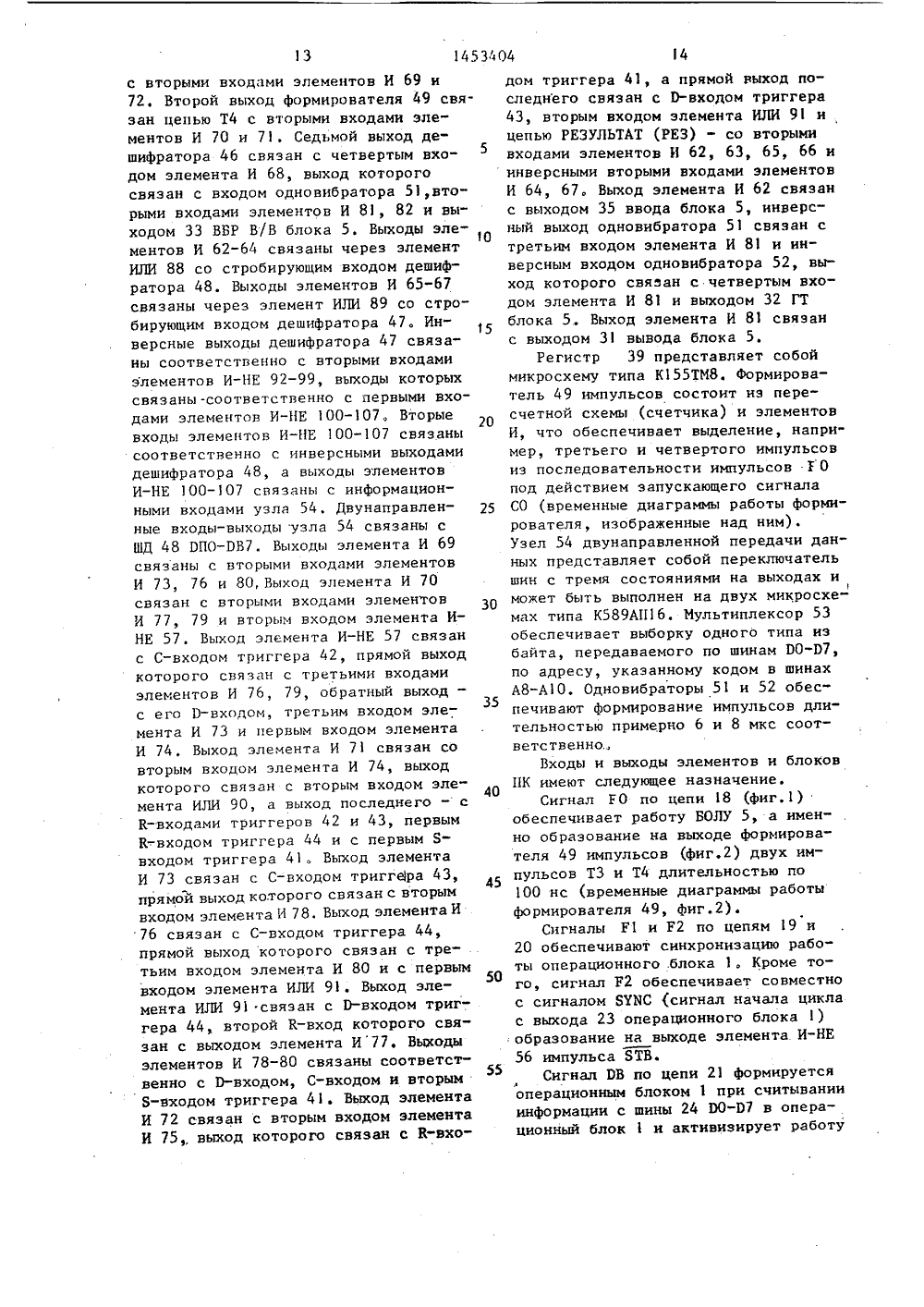

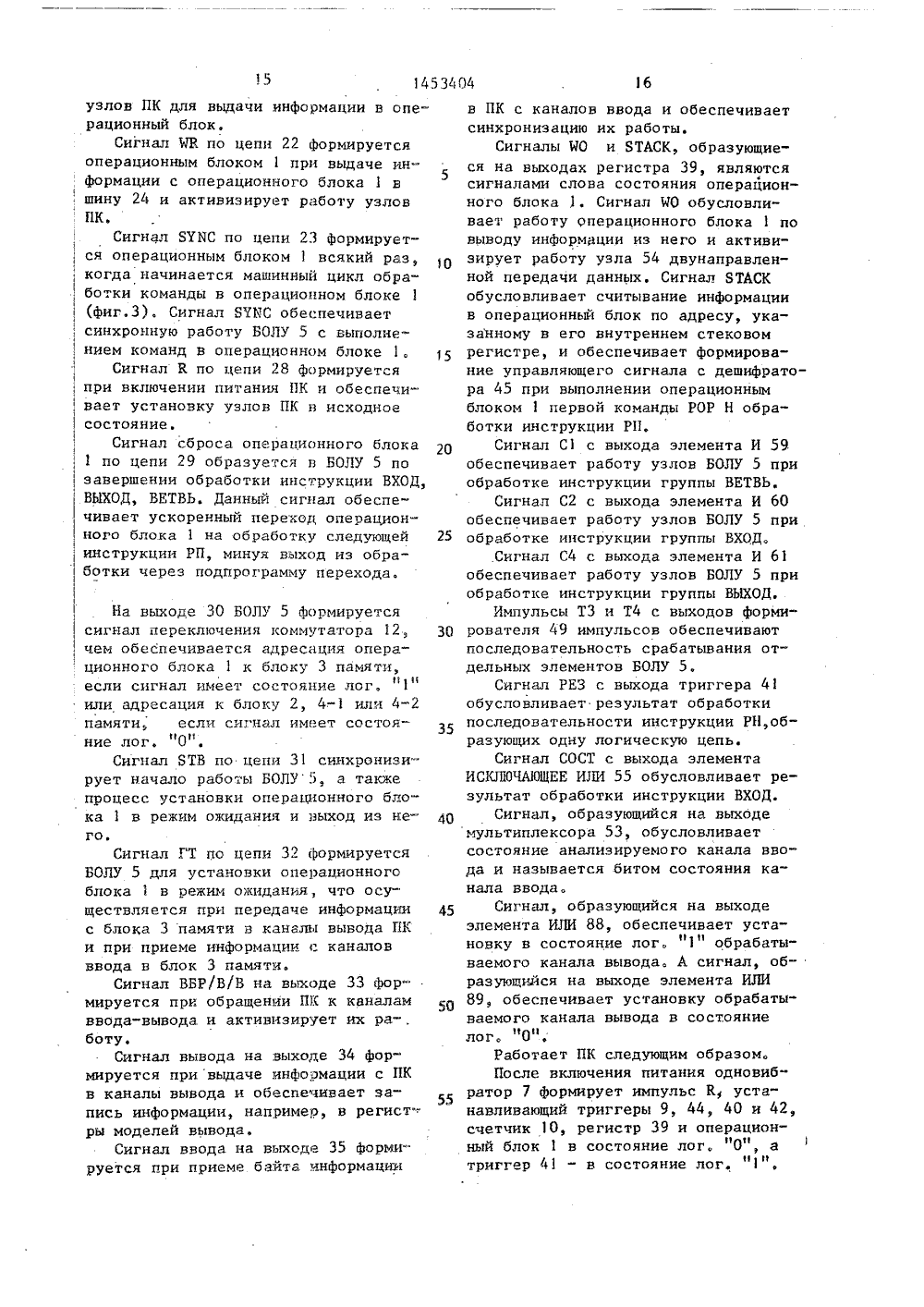

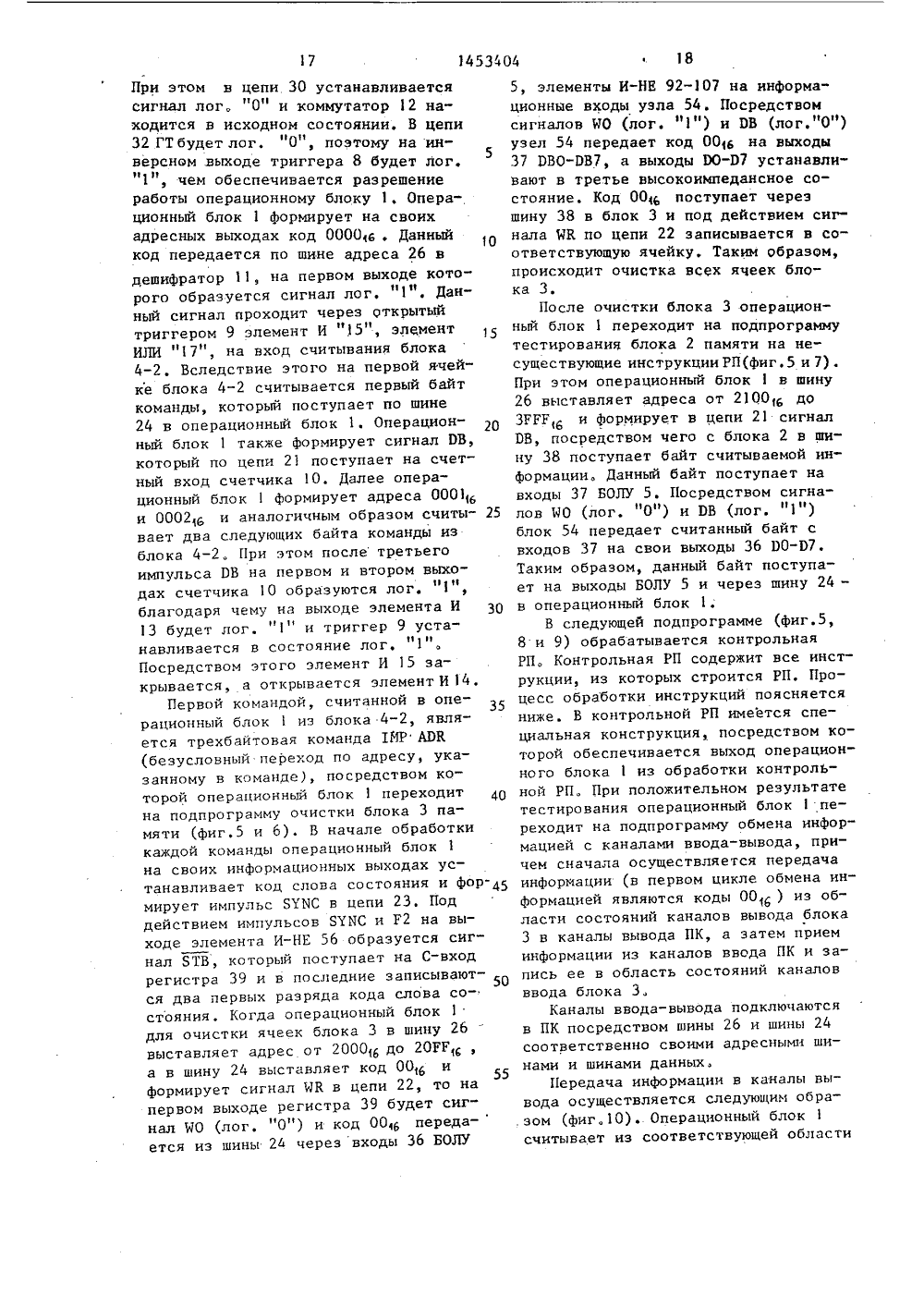

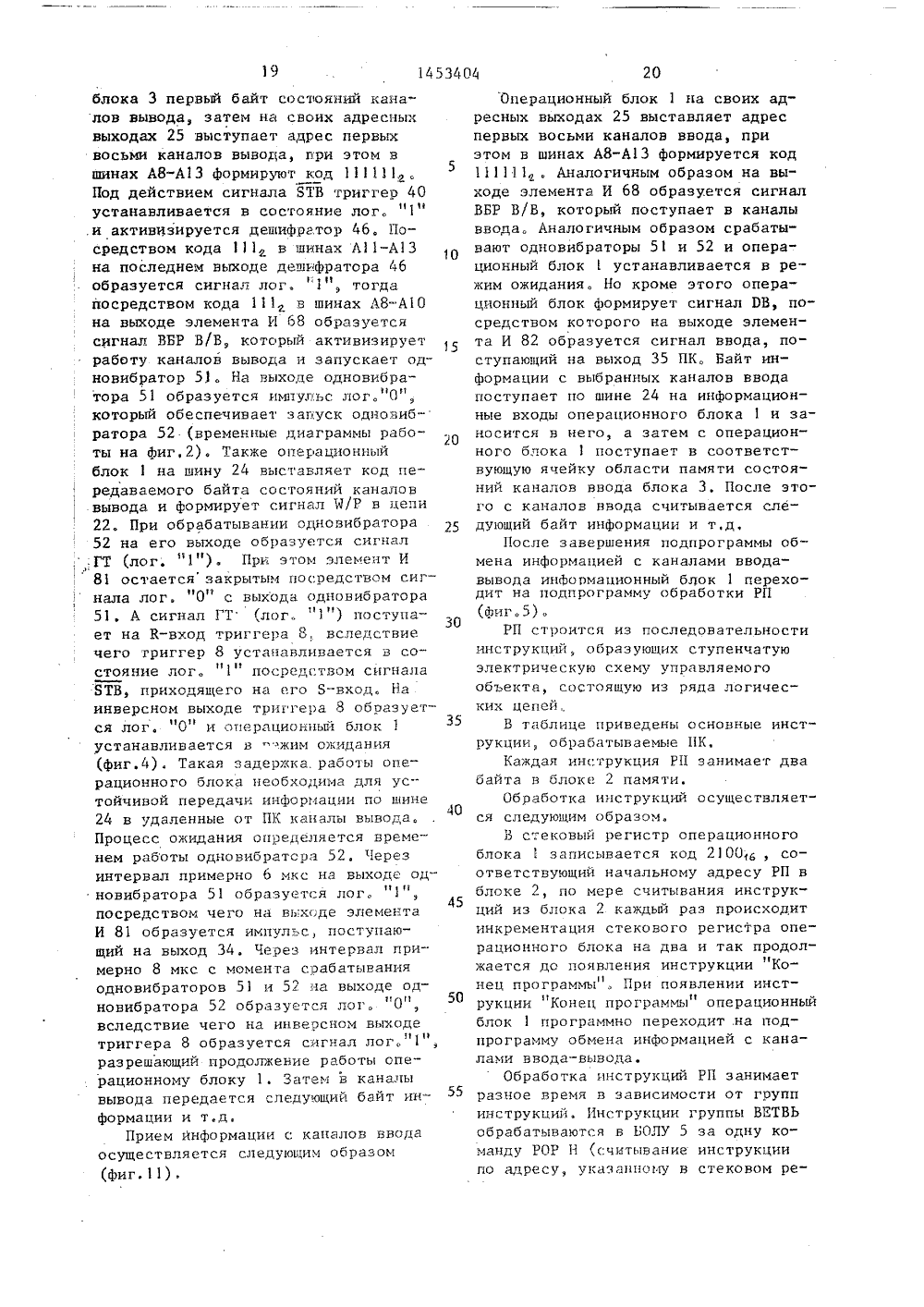

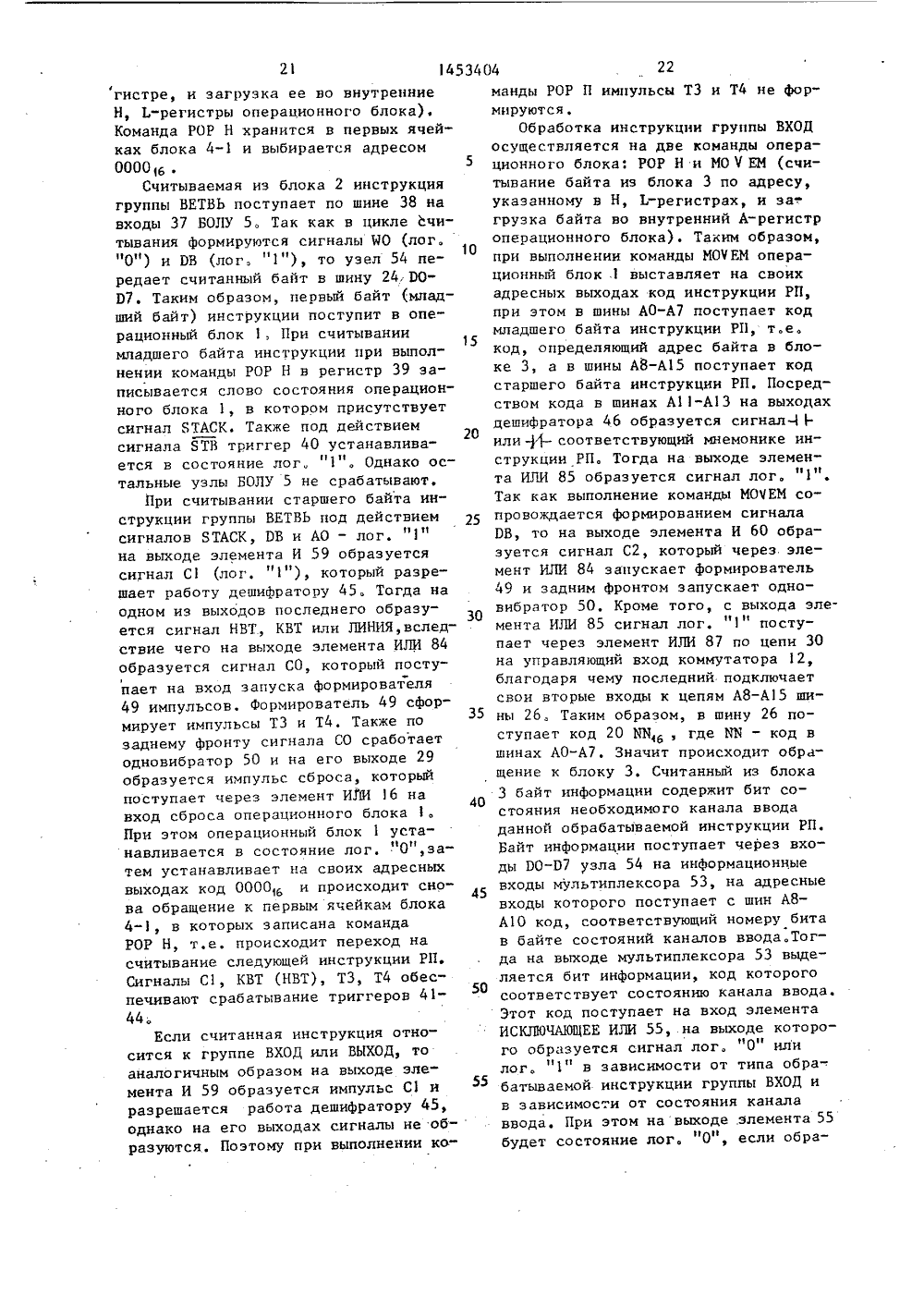

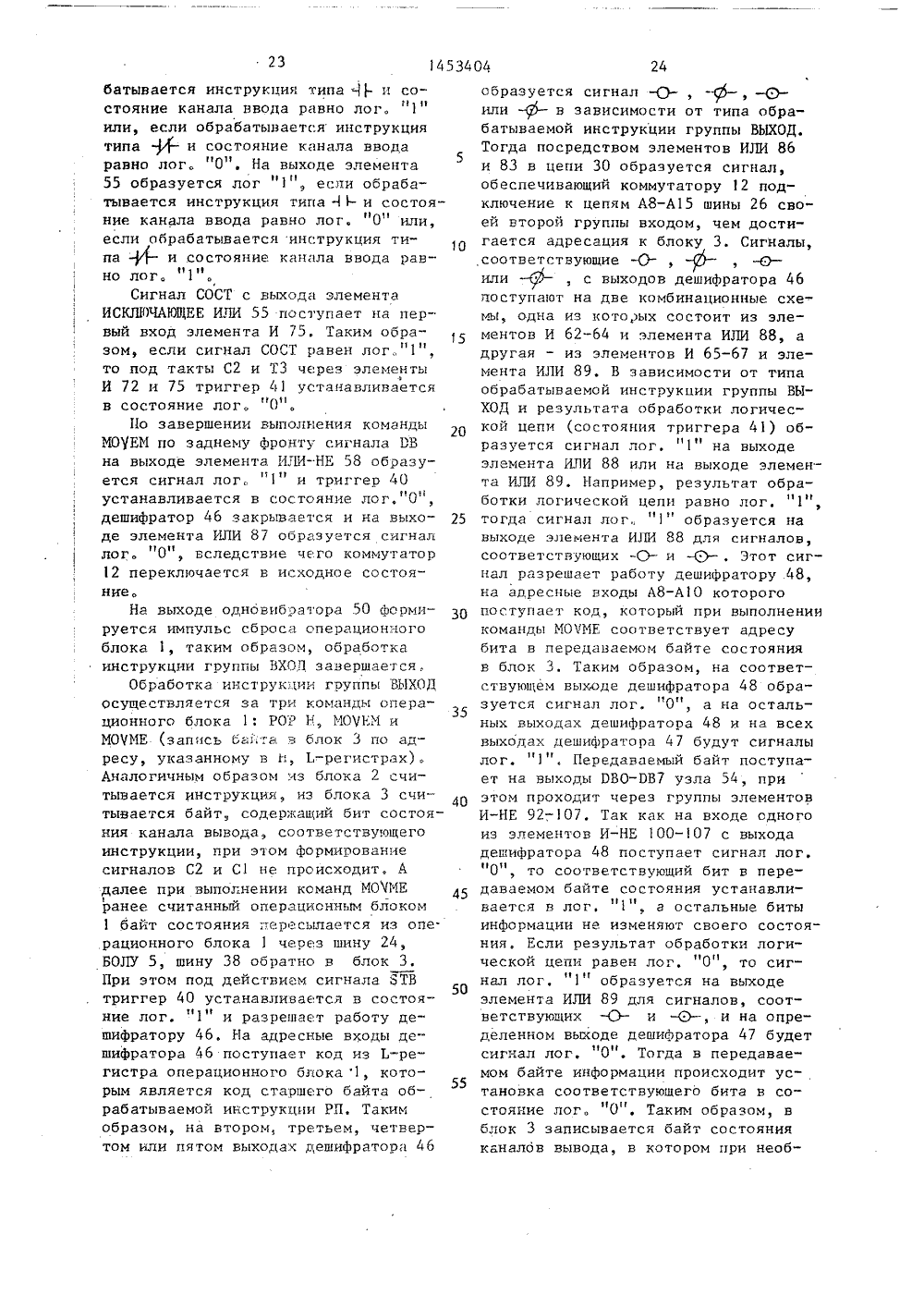

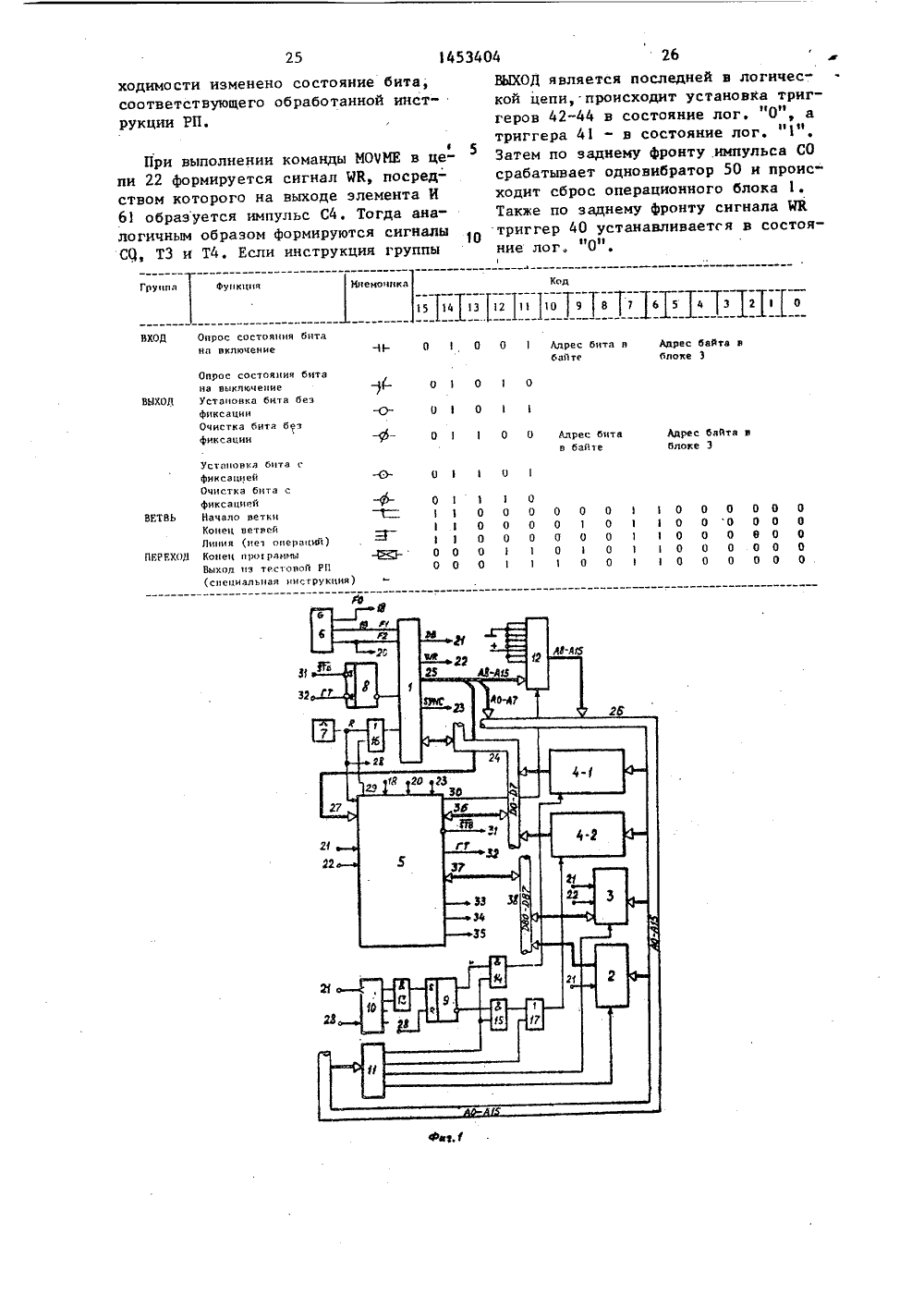

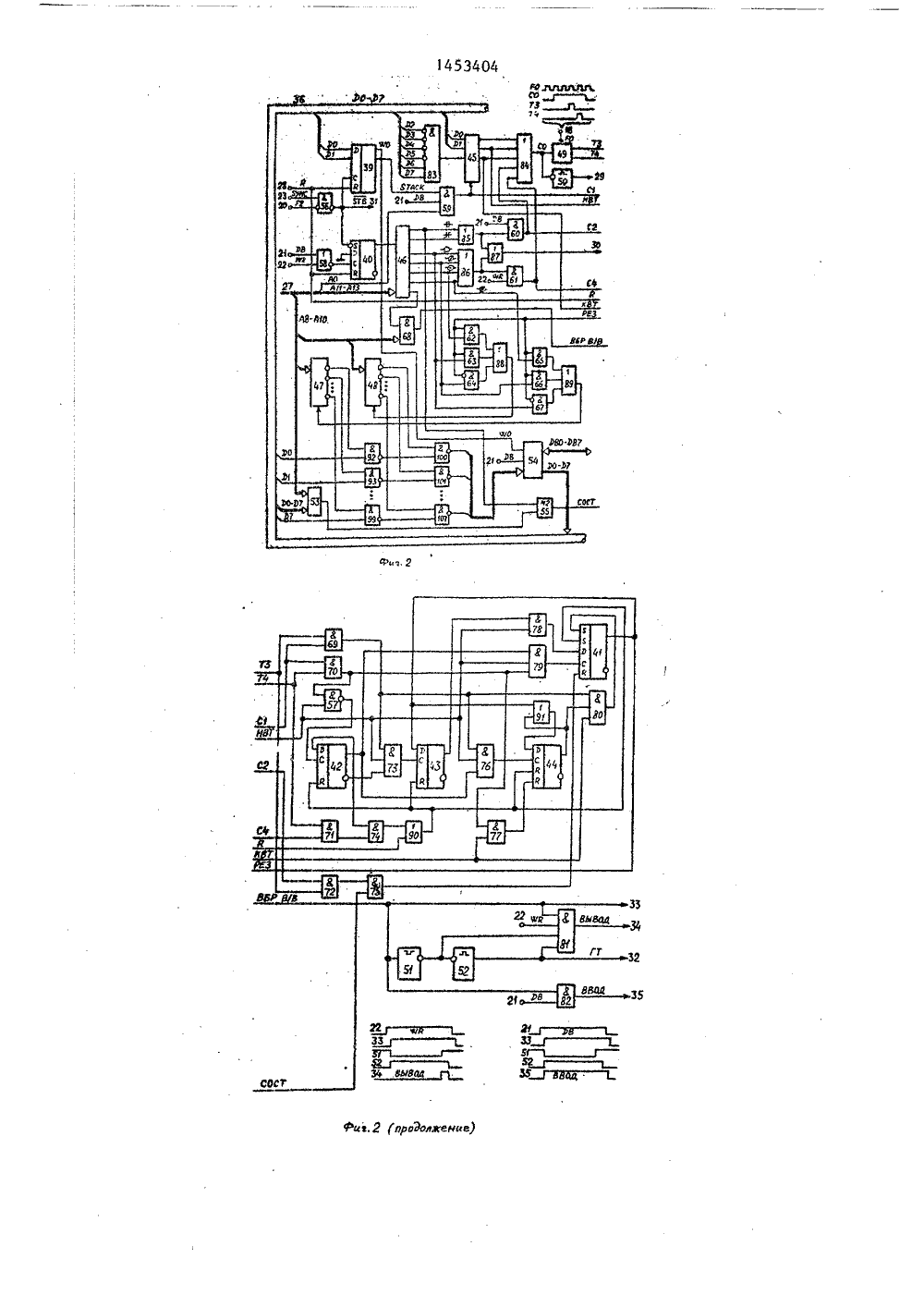

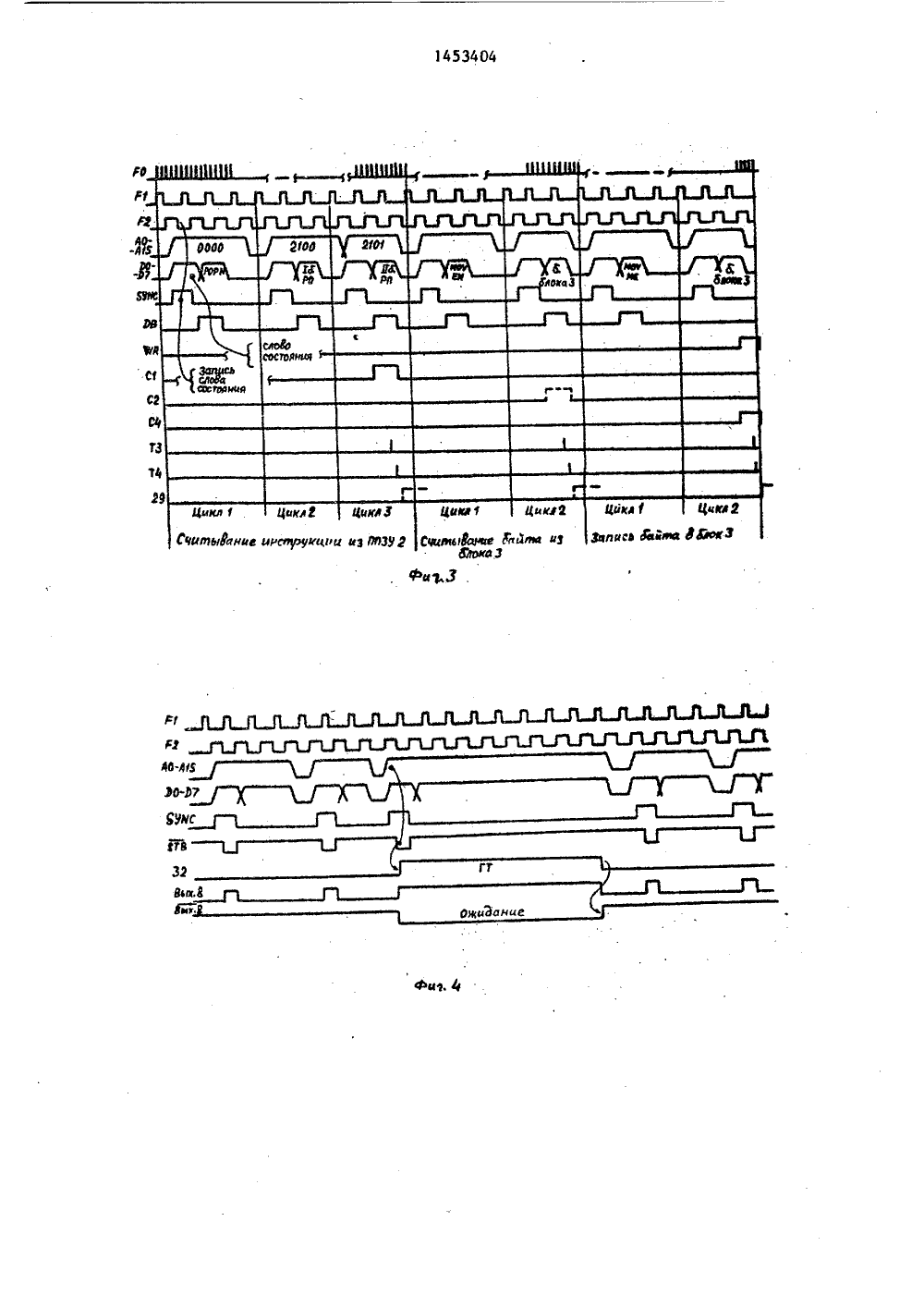

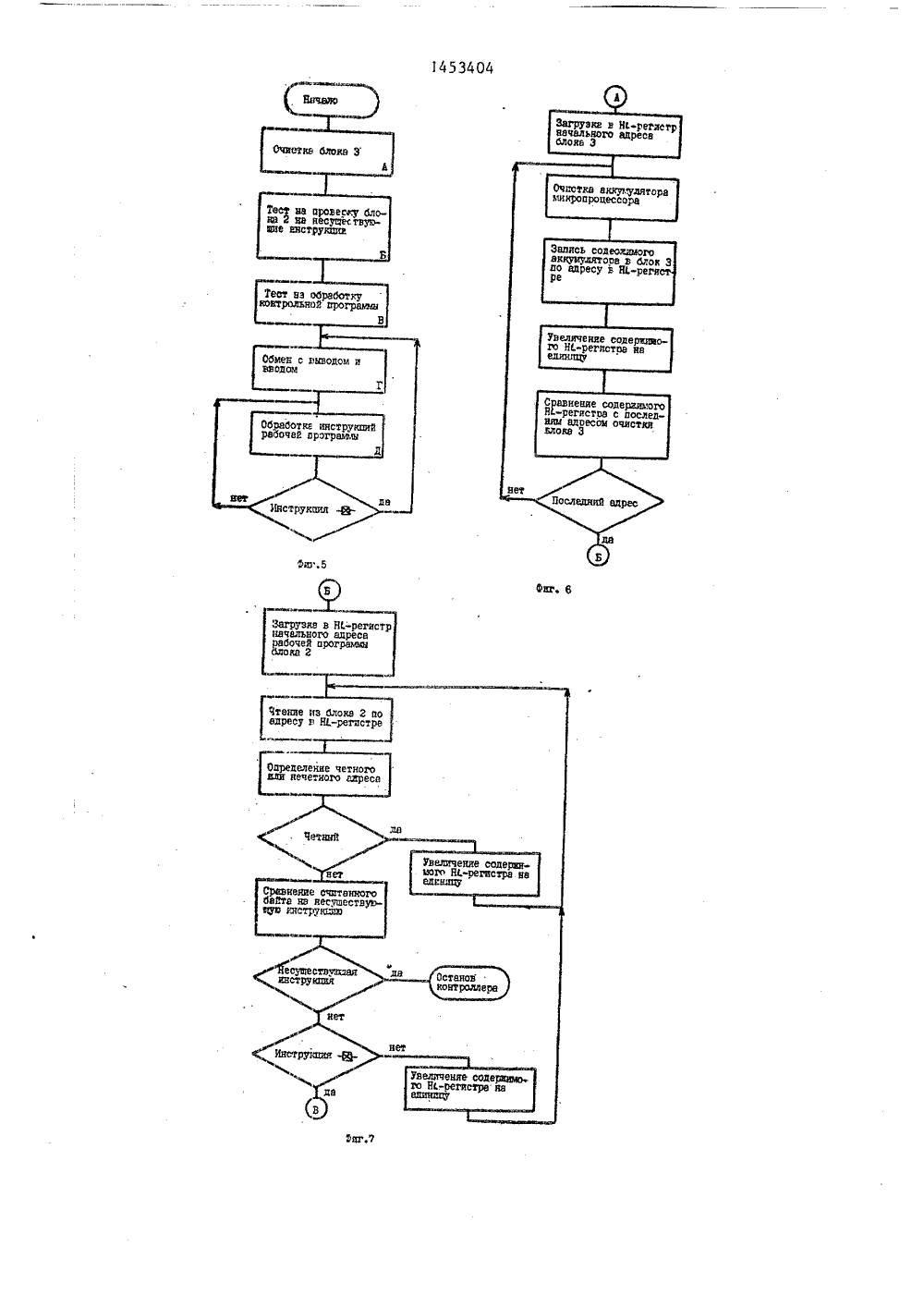

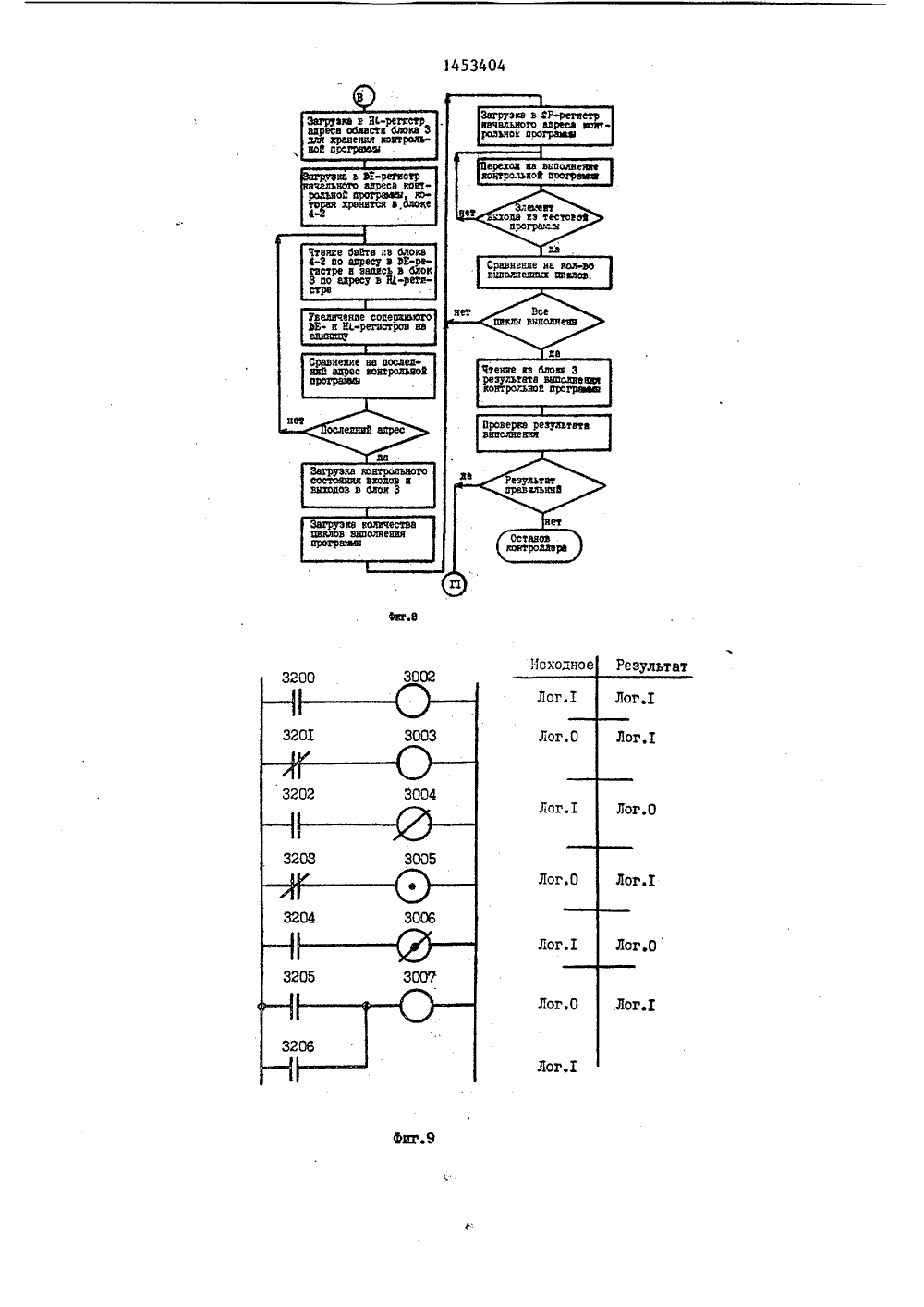

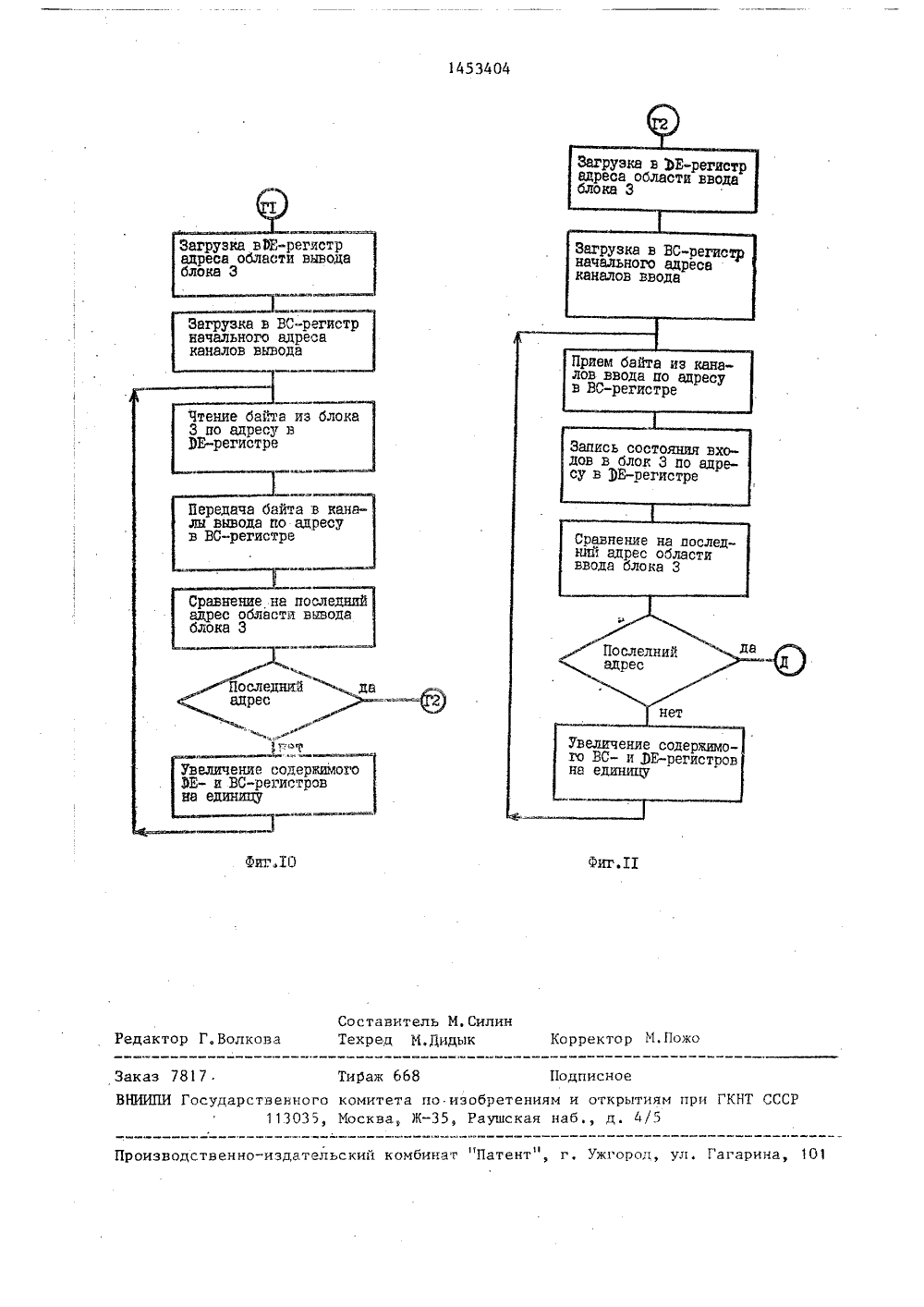

) 4 С 06 1. 9/00 15 ГОСУДАРСТВЕННЫЙ НОМИТЕПО ИЗОБРЕТЕНИЯМ И ОТКРЫТПРИ ГКНТ СССР ПИСАНИЕ ИЗОБРЕТЕНИЯ Н АВТОРСКОМУ СВИДЕТЕЛЬСТВУ або(56) Авторское свидетельство СССРВ 1001012, кл. С 05 В 19/18, 1980.Патент США М 4172289,кл. С 06 Р 9/00, опублик. 1982.(54)(57) 1. ПРОГРАММИРУЕМЫЙ КОНТРОЛЕР,содержащий операционный блок, блокпамяти рабочей программы, блок памяти состояний, первый блок памяти управляющих программ, блок обработкилогических условий, генератор импульсов, формирователь сброса, триггер,элемент ИЛИ и коммутатор, причем выход старших разрядов адреса операционного блока подключен к первому информационному входу коммутатора, второй информационный вход которого подключен к входу фиксированного кодастарших разрядов адреса устройства,выход коммутатора через шину адресаподключен к входам старших разрядовадреса блока памяти рабочей программы, блока памяти состояний и первогоблока памяти управляющих программ,входы младших разрядов адреса которых через шину адреса подключены квыходу младших разрядов адреса операционного блока, первый выход генератора импульсов подключен к первомувходу блока обработки логических условий, второй выход генератора импульсов подключен к первому тактовомувходу операционного блока, третийвыход генератора импульсов подключенк второму тактовому входу операцнонного блока и к второму входу блокаобр тки логических условий, выход формирователя сброса подключен к первому входу первого элемента ИЛИ и ктретьему входу блока обработки логических условий, первый выход которого подключен к второму входу первогоэлемента ИЛИ, выход которого подключен к входу сброса операционного блока, выходы признаков считывания, записи и начала цикла которого подключены соответственно к входам с четвертого по шестой блока обработки логических условий, выход признака считывания операционного блока подключенк входам считывания блока памяти рабочей программы и блока памяти состояний, выход признака записи операционного блока подключен к входу .записи блока памяти состояний, входвыход блока памяти состояний и выходблока памяти рабочей программы черезпервую шину данных подключены к первому входу-выходу блока обработкилогических условий, второй входвыход которого через вторую шинуданных подключен к информационномувходу-выходу операционного блока исоединен с выходом первого блока памяти управляющих программ, выходыблока обработки логических условий свторого по седьмой подключены соответственно к управляющему входу коммутатора входам установки в единицу и установки в ноль первого триггера, выходам признаков выборки логических условий устройства, выходмладших разрядов адреса операционного блока подключен к седьмому входублока обработки логических условий,выход первого триггера подключен квходу готовности операционного блока,о т л и ч а ю щ и й с я тем, что, 1453404 20блока 3 первый байт состояний каналов вывода, затем на своих адресных выходах 25 выступает адрес первых восьми каналов вывода, при этом н шинах А 8-А 13 Формируют код 1111111, Под действием сигнала ЯТВ триггер 40 устананливается в состояние лог. "1" и активизируется дешифратор 46, Посредством кода 111 в шинах А 11-А 13 на последнем ныходе дешифратора 46 образуется сигнал лог, 11, тогда посредством кода 111 н шинах А 8-А 10 на выходе элемента И 68 образуется сигнал ВБР В/В, который активизирует работу каналов вывода и запускает одновибратор 51. На выходе одновибратора 51 образуется импугьс лог."0", который обеспечинает запуск однонибратора 52 (временные диаграммы работы на фиг,2). Также операционный блок 1 на шину 24 выставляет код передаваемого байта состояний каналов вывода и формирует сигнал 11/Р н цепи 22. При обрабатывании однонибратора 52 на его выходе образуется сигнал ГТ (лог, "1"). При этом элемент И 81 остается закрытым посредством сигнала лог, "0" с выхода одновибратора 51, А сигнал ГТ (лог "1") поступает на К-вход триггера 8, вследствие чего григгер 8 устанавливается н состояние лог. "1" посредством сигнала ЯТВ, приходящего на его Б-вход. На инверсном выходе триггера 8 образуется лог. "0" и операционный блок 1 устанавливается н ".жим ожидания (фиг.4). Такая задержка. работы оп.ерационного блока необходима для устойчивой передачи информации по шине 24 в удаленные от ПК каналы вывода, Процесс ожидания определяется временем работы однонибратсра 52, Через интервал примерно 6 мкс на выходе од 11 1 1 новиб р ато ра 5 1 образуется ло г . посредством чего н а выходе элемента И 8 1 образуется импульс, поступающий н а выход 3 4 . Через интервал и римерно 8 мк с. с момента с раб атынания одновиб ра т о ро в 5 1 и 5 2 на выходе од 11 11 но виб ра то ра 5 2 образуется ло г . 0 вследствие чего на ин вер сном выходе11 11 триггера 8 образуется си гн ал ла г1 разрешающий продолжение работы оп ерационному блоку 1 . Затеи н каналы вывода передается сл едующий байт информации и т , д .Прием йнфо рмаци и с каналов ввода осуществляется следующим образом ( фиг . 1 1 ) . 10 15 20 25 ЗО 35 40 45 50 Операционный блок 1 на своих адресных выходах 25 выставляет адреспервых восьми каналов ввода, приэтом в шинах А 8-А 13 формируется код111111 . Аналогичным образом на выходе элемента И 68 образуется сигналВБР В/В, который поступает в каналыввода. Аналогичным образом срабатывают одновибраторы 51 и 52 и опера"ционный блок 1 устанавливается в режим ожидания. Но кроме этого операционный блок формирует сигнал РВ, посредством которого на выходе элемента И 82 образуется сигнал ввода, поступающий на выход 35 ПК, Байт информации с выбранных каналов вводапоступает по шине 24 на информационные входы операционного блока 1 и заносится н него, а затем с операционного блока 1 поступает в соответствующую ячейку области памяти состояний каналов ввода блока 3, После этого с каналов ввода считывается следующий байт информации и т.д,После завершения подпрограммы обмена информацией с каналами вводавывода информационный блок 1 переходит на подпрограмму обработки РП(фиг.5).РП строится из последовательностиинструкций, образующих ступенчатуюэлектрическую схему управляемогообьекта, состоящую из ряда логических цепей,.В таблице приведены основные инструкции, обрабатываемые ПК,Каждая инструкция РП занимает двабайта н блоке 2 памяти.Обработка инструкций осуществляется следующим образом.В стеконый регистр операционногоблока 1 записывается код 2100,6, соответствующий начальному адресу РП нблоке 2, по мере считывания инструкций из блока 2 каждый раз происходитинкрементация стеконого регистра операционного блока на дна и так продолжается до появления инструкции Конец программы . При появлении инструкции Конец программы операционныйблок 1 программно переходит .на подпрограмму обмена информацией с каналами ввода-вывода.Обработка инструкций РП занимаетразное время в зависимости от группинструкций, Инструкции группы ВЕТВЬобрабатываются н ВОЛУ 5 за одну команду РОР Н (считывание инструкциипо адресу, указанному н стековом регистре, и загрузка ее во внутренние Н, Ь-регистры операционного блока). Команда РОР Н хранится в первых ячейках блока 4-1 и выбирается адресом ОООО.Считываемая из блока 2 инструкция группы ВЕТВЬ поступает по шине 38 на входы 37 ВОЛУ 5. Так как в цикле считывания формируются сигналы ЧО (лог. иои) и ПВ (лог. и 1 и), то узел 54 передает считанный байт в шину 24; РОР 7. Таким образом, первый байт (младший байт) инструкции поступит в операционный блок 1. При считывании младшего байта инструкции при выполнении команды РОР Н в регистр 39 записывается слово состояния операционного блока 1, в котором присутствует сигнал ВТАСК. Также под действием сигнала ЯТВ триггер 40 устанавливается в состояние лог. и 1", Однако остальные узлы ВОЛУ 5 не срабатывают,При считывании старшего байта инструкции группы ВЕТВЬ под действием сигналов БТАСК, ВВ и АО - лог. и 1 и иа выходе элемента И 59 образуется сигнал С 1 (лог. и 1 и), который разрешает работу дешифратору 45, Тогда на одном из выходов последнего образуется сигнал НВТ., КВТ или ЛИНИЯ, вследствие чего на выходе элемента ИЛИ 84 образуется сигнал СО, который поступает на вход запуска формирователя 49 импульсов. Формирователь 49 сформирует импульсы ТЗ и Т 4. Также по заднему фронту сигнала СО сработает одновибратор 50 и на его выходе 29 образуется импульс сброса, который поступает через элемент ИГЯ 16 на вход сброса операционного блока 1. При этом операционный блок 1 устаи и навливается в состояние лог. 0 ,затем устанавливает на своих адресных выходах код 0000 ь и происходит снова обращение к первым ячейкам блока 4-1, в которых записана команда РОР Н, т.е. происходит переход на считывание следующей инструкции РП. Сигналы С 1, КВТ (НВТ), ТЗ, Т 4 обеспечивают срабатывание триггеров 41- 44.Если считанная инструкция относится к группе ВХОД или ВЫХОД, то аналогичным образом на выходе элемента И 59 образуется импульс С 1 и разрешается работа дешифратору 45, однако на его выходах сигналы не образуются, Поэтому при выполнении команды РОР П импульсы ТЗ и Т 4 не формируются,Обработка инструкции группы ВХОДосуществляется на две команды операционного блока: РОР Н и МО У ЕМ (считывание байта из блока 3 по адресу, указанному в Н, Ь-регистрах, и загрузка байта во внутренний А-регистроперационного блока). Таким образом,при выполнении команды МОУЕМ операционный блок,1 выставляет на своихадресных выходах код инструкции РП,при этом в шины АО-А 7 поступает кодмладшего байта инструкции РП, т.е.15код, определяющий адрес байта в блоке 3, а в шины А 8-А 15 поступает кодстаршего байта инструкции РП, Посредством кода в шинах А 11-А 13 на выходахдешифратора 46 образуется сигнал 4 1 или +- соответствующий мнемонике инструкции РП. Тогда на выходе элемента ИЛИ 85 образуется сигнал лог. "1".Так как выполнение команды МОУЕМ сопровождается формированием сигналаВВ, то на выходе элемента И 60 образуется сигнал С 2, который через. элемент ИЛИ 84 запускает формирователь49 и задним фронтом запускает однавибратор 50, Кроме того, с выхода элемента ИЛИ 85 сигнал лог, 1 постуи ипает через элемент ИЛИ 87 по цепи 30на управляющий вход коммутатора 12,благодаря чему последний подключаетсвои вторые входы к цепям А 8-А 15 ши ны 26, Таким образом, в шину 26 поступает код 20 Ш, , где М 11 - код вшинах АО-А 7. Значит происходит обращение к блоку 3. Считанный из блока3 байт информации содержит бит состояния необходимого канала вводаданной обрабатываемой инструкции РП,Байт информации поступает через входы ПОузла 54 на информационные 45входы мультиплексора 53, на адресныевходы которого поступает с шин А 8- А 10 код, соответствующий номеру битав байте состояний каналов ввода.Тогда на выходе мультиплексора 53 выделяется бит информации, код которогосоответствует состоянию канала ввода.Этот код поступает на вход элементаИСКЛЮЧАЮЩЕЕ ИЛИ 55,.на выходе которого образуется сигнал лог. 0 илилог, и 1 и в зависимости от типа обрабатываемой инструкции группы ВХОД ив зависимости от состояния каналаввода, При этом на выходе .элемента 55будет состояние лог. "0", если обра 23241453404батывается инструкция типа - и состояние канала ввода равно лог. "1"или, если обрабатывается инструкциятипа +1- и состояние канала вводаравно лог. 0. На выходе элемента55 образуется лог 1 , если обрабатывается инструкция типа 1- и состояние канала ввода равно лог. пО или,если обрабатывается инструкция типа +1- и состояние канала ввода равно лог. 1.Сигнал СОСТ с выхода элементаИСКЛ 1 ОЧА 0 ЩЕЕ ИЛИ 55 поступает на первый вход элемента И 75, Таким образом, если сигнал СОСТ равен лого"1",то под такты С 2 и Т 3 через элементыИ 72 и 75 триггер 41 устанавливаетсяв состояние лог, "О",Но завершении выполнения командыМ 07 ЕМ по заднему фронту сигнала ПВна выходе элемента ИГИ-НЕ 58 образуется сигнал лого "1" и триггер 40устанавливается в состояние лог.0",дешифратор 46 закрывается и на выходе элемента ИЛИ 87 образуется сигналлог. "0", вследствие чего коммутатор12 переключается в исходное состоя 1 О 20 ние.На выходе одновибратора 50 формируется импульс сброса операционного блока 1, таким образом, обработка инструкции группы ВХОД завершаетсяОбработка инструкции группы ВЫХОД осуществляется за три команды операционного блока 1: РОР Н, МОуЕМ иМО/МЕ (запись баГ;та в блок 3 по адресу, указанному в Н, Егрегистрах).Аналогичным образом из блока 2 считывается инструкция, из блока 3 считывается байт, содержащий бит состояния канала вывода, соответствующего инструкции, при этом формирование сигналов С 2 и С не происходит, А далее при выполнении команд МОЭМЕ 45 ранее считанный операционным блоком 1 байт состояния пер=сылается из опе. рационного блока 1 через шину 24, ВОЛУ 5, шину 38 обратно в блок 3.При этом под действием сигнала ЯТВ триггер 40 устанавливается в состояние лог. "1" и разрешает работу дешифратору 46. На адресные входы дешифратора 46 поступает код из .-регистра операционного блока 1, кото 55 рым является код старшего байта обрабатываемой инструкции РП. Таким образом, на втором, третьем, четвертом или пятом выходах дешифратор 46 образуется сигнал -О-, -ф-, -Оили -ф- в зависимости от типа обрабатываемой инструкции группы ВЫХОД.Тогда посредством элементов ИЛИ 86и 83 в цепи 30 образуется сигнал,обеспечивающий коммутатору 12 подключение к цепям АЗ-А 15 шины 26 своей второй группы входом, чем дости"гается адресация к блоку 3. Сигналы,соответствующие -Ст , -ф , ттили -ф- , с выходов дешифратора 46поступают на две комбинационные схемы, одна из которых состоит из элементов И 62-64 и элемента ИЛИ 88, адругая - из элементов И 65-67 и элемента ИЛИ 89. В зависимости от типаобрабатываемой инструкции группы ВЫХОД и результата обработки логической цепи (состояния триггера 41) образуется сигнал лог, "1" на выходеэлемента ИЛИ 88 или на выходе элемента ИЛИ 89. Например, результат обработки логической цепи равно лог. "1",тогда сигнал логообразуется навыходе элемента ИЛИ 88 для сигналов,соответствующих -О- и -Я- . Этот сигнал разрешает работу дещифратору 48,на адресные входы А 8-А 10 которогопоступает код, который при выполнениикоманды МОЭМЕ соответствует адресубита в передаваемом байте состоянияв блок 3, Таким образом, на соответствующем выходе дешифратора 48 образуется сигнал лог. 0, а на остальных выходах дешифратора 48 и на всехвыходах дешифратора 47 будут сигналылог. "1", Передаваемый байт поступает на выходы РВО-ВВ 7 узла 54, приэтом проходит через группы элементовИ-НЕ 92-, 07. Так как на входе одногоиз элементов И-НЕ 100-107 с выходадешифратора 48 поступает сигнал лог,"0", то соответствующий бит в передаваемом байте состояния устанавливается в лог. "1", а остальные битыинформации не изменяют своего состояния, Если результат обработки логической цепи равен лог. 0, то сигнал лог, "1" образуется на выходеэлемента ИЛИ 89 для сигналов, соответствующих -0- и -Я-, и на определенном выходе дешифратора 47 будетсигнал лог, 10". Тогда в передаваемом байте информации происходит установка соответствующего бита в состояние лог. "0", Таким образом, вблок 3 записывается байт состоянияканалов вывода, в котором при необ14 1 О 1 О О Адрес байта вблоке 3 Адрес бита вбайте о 1 о 1 а Опрос состояния битаиа выключениеУстановка бита безфиксацииОчистка бита безфиксации ВЦХОЛ а 1 оО 1 1 О О Адрес бита в балтеАдрес байта вблоке Э а 1 1 О ооооо о оо о о о о о о о о а 1 1 1 1 о о о о о о в о о о о о о о о о о о о о о о о о о о о о о а о о о О 1 О а о о а 1 оо а 31 ходимости изменено состояние бита,соответствующего обработанной инстРукции РП еПри выполнении команды МОЭМЕ в цепи 22 формируется сигнал ЯКз посредством которого на выходе элемента И 61 образуется импульс С 4. Тогда аналогичным образом формируются сигналы СЦз ТЗ и Т 4, Если инструкция группы ВХОД Опрос состояния бита иа включениеУстаовка бита сфиксациейОчистка бита сфиксацияВЕТВЬ Начало веткиКонец ветвейПипия (ет операций)ПЕРЕХОД Конец прораи 1 ыВыход из тестовой РП(сециальая ииструкция) 53404 26ВЫХОД является последней в логичес-.кой цепи, происходит установка триггеров 42-44 в состояние лог. "0", а триггера 41 - в состояние лог. "1".Затем по заднему фронту импульса СО срабатывает одновибратор 50 и происходит сброс операционного блока 1.Также по заднему фронту сигнала ЯК триггер 40 устанавливается в состояние лог. "Опк1453404Тест нэ обработку коитрщьной прогревы Загрузке в Н 1-регистр начального адреса рабочей прогревы 1 лока 2 гение из блока 2 по дресу в НС-регистре Опреиеление четного вщ нечетного адресе3453404 да да РезультатправкяьянЬ Остановконтроллера Зйгруэка В Нь Регистр адреса областн блока 3 дгя хранения контроль, ной псогреса яа ь Мрегистрното алвеса контрольной прогрева, яоторая хранятся в.блоКЕ аЧтение байта яв блока4-2 по авресу в РЕ-регистре в вапнсь в блок3 по адресу в Щ-регистре Увелнченяе содерквегоЭЕ- иНЬ-регистров ва еднБшу Сравнение на всследвий адрес контрольнойпрогра 3 аВ нетоследний адрес Загрузка контрольногосостояшя анодов нвнзодов в блок 3 Загрузке количестваяналов внполяеняяпретр йаа Загрузка в ЬР-регистрначального Вцеса нсвтрольяок поограва Передан не внполввве контрольной поогранщ пене ктет,клода ке тестовойпрогрэ.и Сревнеяяе яа коя-зо внпожеяал пнклов. Чтение яэ блока 3реяультата внполвещнконтрольной прогрева Нроверка результатавнполненянС-региалре "а л выв ер Фиг.10 иг.1 Т Составитель И,СилинРедактор Г,Волкова Техред И,Дидык ектор М.Пож Подписное 7817 а роизводственно-издательский комбинат "Патент", г, Ужгород, ул. Гагарина, 101 Государственного 113035, ТиРаж 668комитета по изобМосква, Ж, Ра ниям и открытиям при ГКНТ ССая наб., д, 4/5с целью повышения надежности, в него введены второй блок памяти управляющих программ, второй элемент ИЛИ, .счетчик, дешиФратор,:второй триггер и три элемента И, причем выход признака считывания операционного блока подключен .к счетному входу счетчика, вход установки в ноль, первый и вто/рой выходы которого подключены соответственно к выходу формирователя сброса, к первому и второму входам первого элемента И, выход которого подключен к входу установки в единицу второго триггера, вход установки . в ноль и выход которого подключены соответственно к выходу формирователя сброса и к первому входу второго элемента И, выход которого подключен к входу считывания первого блока памяти управляющих программ, инверсный выход второго триггера подключен к первому входу третьего элемента И, выход которого подключен к первому входу второго элемента ИЛИ, выход которого подключен к входу считывания второго блоха памяти управляющих программ, адресный вход которого подключен через шину адреса к выходу коммутатора и к выходу младших разрядов адреса операционного блока и соединен с входом дешифратора, выход второго блока памяти управляющих программ подключен, чсрез вторую шину данных к информационному входу операционного блока первый выходдешифратора подключе: к вторым входам третьего и четвертого элементов И, второй выход дешифратора подключен к второму входу второго элеМента ИЗИ, трЕтий и четвертый выходы дешифратора подключены соответственно к входам выборки блока памяти состояний и блока памяти рабочей программы.2, Программируемый контролер по пю 1 о т л и ч а ю щ и й с я тем что блок обработки логических условий содержит регистр, пять триггеров, четыре дешифратора, Формирователь им.пульсов, три одновибратора, мультиплексор, узел двунаправленной передачи данных, элемент ИСКЛЮЧАЮЩЕЕ ИМ 4, два элемента И-НЕ, элемент ИЛИ-НЕ, двадцать пять элементов И восемь элементов ИЛИ, цве группы элементов И-НЕ, причем первый вход-выход блока через шину подключен к информациоь- ному входу-выходу узла двунаправленной передачи данных, инфориационный 5 О 15 20 25 ЗО 35 4 О 45 5 О 55 выход которого, информационные входымультиплексора, первые входы элементов И-НЕ первой группы, информационный вход регистра, информационныйвход первого дешифратора, входы .первого элемента И через шину соединеныс вторым входом-выходом блока, выходпервого триггера подключен к стробирующему входу второго дешифратора,К-е выходы третьего и четвертого дешифраторов подключены соответственнок второму входу К-го элемента И-НЕпервой группы и к первому входу К-гоэлемента И-НЕ второй группы (К=1М, где М - разрядность шины данных),второй вход и выход которого подключены соответственно к выходу К-гоэлемента И-НЕ первой группы и к информационному входу К-го разряда узла двунаправленной передачи данных,вход режима записи которого подключен к первому выходу регистра, второй выход которого подключен к первому входу второго элемента И, выходыпервого и второго элементов И подключены соответственно к информационному и стробирующему входам первого дешифратора, первый вход блока подключен к тактовому входу формирователяимпульсов, второй вход блока подключен к инверсному входу первого элемента И-НЕ, третий вход блока подключен к входам установки в ноль регистра и первого триггера и к первому входу первого элемента ИЛИ, четвертый вход блока подключен к первому входу элемента ИЛИ-НЕ, входу режима чтения узла двунаправленной передачи данных, второму входу второгоэлемента И, первому входу третьегоэлемента И, пятый вход блока подключен к второму входу элемента ИЛИ-НЕ,первому входу четвертого элемента И,первому входу пятого элемента И,шестой вход блока подключен к второмувходу первого элемента И-НЕ, выходвторого дешифратора подключен к первому входу шестого элемента И, седьмой вход блока подключен к информационному входу второго дешифратора,к остальным входам шестого элементаИ, информационным входам третьего ичетвертого дешифраторов, к второмуинформационному входу мультиплексора": к третьему входу второго элементаИ, четвертый вход блока подключен кпервому входу седьмого элемента И,первый выход блока подключен к выхо5 145 ду первого одновибратора, второй выход блока подключен к выходу второго элемента ИЛИ, третий выход блока подключен к выходу первого элемента И-НЕ и соединен с синхровходом регистра и входом установки в единицу первого триггера, выход второго одновибратора через третий одновибратор подключен к четвертому выходу блока и второму входу четвертого элемента И, третий вход которого подключен к выходу второго одновибратора, выход шестого элемента И подключен к входу второго одновибратора, к пятому выходу блока, четвертому входу четвертого и второго входу седьмого элементов И, выходы которых подключены соответственно к шестому и седьмому выходам блока, выход. второго триггера подключен к первым входам элементов И с восьмого по тринадцатый, информационному входу третьего триггера и первому входу третьего элемента ИЛИ, выход которого подключен к информационному входу четвертого триггера, выходы элементов И с восьмого по десятый подключены соответственно к входам четвертого элемента ИЛИ, выход которого подключен к стробирующему входу четвертого дешифратора, выходы элементов И с одиннадцатого по тринадцатый подключень 1 к входам пятого элемента ИЛИ, выход которого подключен к стробирующему входу третьего дешифратора, выход шестого элемента ИЛИ подключен к входу первого одновибратора и к входу запуска формирователя импульсов, первый выход которого подключен к первым входам четырнадцатого и пятнадцатого элементов И, второй выход формирователя импульсов подключен к первым входам шестнадцатого и семнадцатого элементов И, выходы которых подключены соответственно к первым входам второго элемента И-НЕ и восемнадцатого элемента И, выход которого под" ключен к второму входу первого элемента ИЛИ, выход которого подключен к входам установки в ноль третьего, четвертого и пятого триггеров и первому входу установки в единицу второго триггера, второй вход установки в единицу, вход установки в ноль, информационный вход и синхровход которого подключены соответственно к выходам элементов И с девятнадцатого по двадцать второй, выходы элементов 3404 6и с двадцать третьего по двадцать пя 1тый подключены соответственно к второму входу установки в ноль и синхровходу третьего триггера, к сннхровходу четвертого триггера, выход седьмого элемента ИЛИ подключен к второмувходу третьего элемента И и к первомувходу второго элемента ИЛИ, выходвосьмого элемента ИЛИ подключен квторому входу второго элемента ИЛИ ик второму входу пятого элемента И,выход которого подключен к первомувходу шестого элемента ИЛИ и к второму входу семнадцатого элемента И выФход третьего элемента И подключен квторому входу шестого элемента ИЛИ ик второму входу пятнадцатого элемента И, выход которого подключен к пер вому входу двадцатого элемента И,второй вход которого подключен к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, первыйи второй входы которого подключенысоответственно к выходу мультиплексо ра и к первому выходу второго дешифратора, выходы с первого по шестойкоторого подключены соответственно кпервому и второму входам седьмого ик входам с первого по четвертый восьЗ 0 мого элементов ИЛИ, третий выход второго дешифратора подключен к.вторымвходам девятого и тринадцатого элементов И, четвертый выход второгодешифратора подключен к вторым входамдесятого и двенадцатого элементов И,пятый и шестой выходы второго дешифратора подключены соответственно квторым входам восьмого и одиннадцатого элементов И, выход первого элемента ИЛИ-НЕ подключен к синхровходупервого триггера, информационныйвход которого подключен к входу логического нуля контроллера, выход второго элемента И подключен к вторым 45входам четырнадцатого и шестнадцатого элементов И, выходы с первого потретий первого дешифратора подключены соответственно к входам с третьего по пятый шестого элемента ИЛИ, 50второй выход первого дешифратора подключен к второму входу второго элемента И-НЕ и к первым входам двадцатьпервого, двадцать второго, двадцатьчетвертого и двадцать пятого элементов И, вторые входы которых подключены соответственно к выходу третьеготриггера, выходу шестнадцатого элемента И, прямому и инверсному выходам пятого триггера, третий выход1453404 5 10 первого дешифратора подключен к первым входам двадцать третьего и девятнадцатого элементов И, выход четырнадцатого элемента И подключен ктретьим входам двадцать четвертого идвадцать пятого элементов И и. к второму входу девятнадцатого элемента.И, третий вход которого подключен квыходу четвертого триггера и соединен с вторым входом третьего элемента ИЛИ, второй вход дваццать третьего элемента И подключен к выходу Изобретение относится к вычислительной технике и предназначено дляпостроения программируемых контролеров (ПК),Целью изобретения является попышение надежности работы ПК.На фиг,1 представлена функциональная схема ПК; на фиг.2 - схема блокаобработки логических условий (БОЛУ);на фиг.3 - временная диаграмма работы ПК при обработке инструкций ВХОД,ВЫХОД, ВЕТВЬ; на фиг,4 - временнаядиаграмма процесса установки операционного блока в режим ожидания; нафиг.5 - структурная схема алгоритмаработы ПК; на иг,6 - структурнаясхема алгоритма очистки блока памятисостояний; на фиг.7 - структурнаясхема алгоритма пр., ерки блока памяти рабочей программы (РП) на несуществующие инструкции на фиг.8 -структурная схема алгоритма теста обработки контрольной программы; нафиг.9. - ступенчатая электрическаясхема контрольной РП для теста обработки; на фиг,10 - структурная схемаалгоритма обмена информацией с каналами вывода; на фиг.1 - то же, с каналами ввода,Программируемый контролер содержит операционный блок 1, блок 2 памяти рабочей программы (ППЗУ), блок3 памяти состояний (ОЗУ), первый ивторой блоки 4-1 и 4-2 памяти управляющих программ (ПЗУ), блок 5 обработки логических условий (ВОЛУ 5),генератор 6 импульсов, формирователь7 сброса, триггеры 8 и . В:-Б-типа,9двоичный счетчик 10,деширатор 11,коммутатор 12, элементы И 13-15, элементы ИЛИ 16-17,шестнадцатого элемента И, выход второго элемента И-НЕ подключен к синхровходу пятого триггера, прямой выход которого подключен к третьемувходу двадцать второго элемента И, инверсный выход пятого триггера подключен к информационному входу пятого триггера и к второму входу восемнадцатого элемента И, выход которогоподключен к второму входу первогоэлемента ИЛИ. Генератор 6 импульсов имеет выходы 18 К, 19 Р 1 и 20 Р 2,при этомвыход 18 подключен к входу синхронизации 18 ВОЛУ 5,.выход 19 - к первому тактовому входу операционного блока 1, выход 20 - ко второму тактовому входу операционного блока 1 и ковходу 20 синхронизации ВОЛУ 5. Операционный блок 1 имеет выход 21 признака считывания РВ, выход 22 признаказаписи (Ув.), выход 23 начала цикла(ЯКОБС), двунаправленные выводы, подключенные к 8-разрядной шине 24 данных (ЩД 24) РО-Р 7, адресные выходы25 АО-А 15, вход готовности, связанный с инверсным выходом триггера 8,и вход сброса, связанный с выходомэлемента ИЛИ 6, Адресные выходы АОА 7 операционного блока 1 и выходы А 8 А 15 коммутатора 12 подключены к шине26 адреса (ША 26) АО-А 15, котораясвязана с адресными входами блока 2памяти рабочей программы, с адресными входами блока 3 памяти состояний,с адресными входами первого и второго блоков 4-1 и 4-2 памяти управляющих программ, а также с адреснымивходами А 8-А 15 дешифратора 11. Крометого, адресные выходы АО, А 8-А 13 операционного блока 1 подключены к входам 27,ВОЛУ 5,а адресные выходы А 8 А 13 подключены к первой группе входом коммутатора 12, вторая группавходов которого связана с входом фиксированного кода старших разрядов адреса, т.е. с цепями источника питания ПК, при этом шестой вход этойгруппы подключен к "+ питания, а остальные - к входу логического нуляВыход 21 РВ операционного блока 1подключен к счетному входу счетчика10, входам считывания блоков 2 и 3 ивходу 21 БОЛУ 5, Выход 22 МК операционного блока 1 подключен к входузаписи блока 3 и к входу 22 БОЛУ 5.Выход 23 БУНС операционного блока 1подключен к входу 23 ВОЛУ 5,Выход К формирователя 7 сбросаподключен к первому входу элементаИЛИ 16, к входу 28 сброса ВОЛУ 5, квходу 28 сброса счетчика 10 и к Квходу триггера 9. Второй вход элемен"та ИЛИ 16 подключен к выходу 29 сбро"са БОЛУ 5.ВОЛУ 5 имеет выход 30 переключения, связанный с управляющим входомкоммутатора 12, инверсный выход 31стробирования (БТВ), связанный с 8 входом триггера 8, выход 32 готовнос"ти (ГТ), связанный с К-входом триггера 8, выходы 33 выборки свода-вывода (ВБР В/В), 34 вывода и 35 ввода,ВОЛУ 5 имеет двунаправленные входы-выходы 36, связанные с ЩД 24, идвунаправленные входы-выходы 37,связанные с шиной 38 данных (ШД 38)ВВОВ 7. При этом шина 24 связана синформационными выходами блоков 4-1и 4-2, а шина 38 - с информационнымн входами-выходами блока 3 и информационными выходами блока 2,Первый и второй выходы двоичного счетчика 1 О связаны через элемент И 12 с Б-входом триггера 9, прямой выход которого связан с первым входом элемента И 14, а инверсный выход - с первым входом элемента И 15. Вторые 40 входы элементов И 14 и 15 .подключены к первому выходу дешифратора 11, второй выход которого связан с первым входом элемента ИЛИ 7. Второй вход элемента ИЛИ 17 связан с выходом эле мента И 5, Выход элемента И 14 подключен к входу считывания блока 4-1, . выход элемента ИЛИ 7 - к входу считывания блока 4-2, Третий выход дешифратора 11 связан с входом выборки блока 3, а четвертый выход - с входом выборки блока 2. Операционный блокпредставляет собой микропроцессор и может быть выполнен на микросхеме КР 580 ИК 80 А, которая имеет двунаправленную 8-разрядную шину данных и 16-разрядную шину адреса. 1453404 ОКоммутатор 12 представляет собойдва шинных формирователя, например,на микросхемах типа К 589 ИР 12.Генератор импульсов состоит нзкварцевого генератора и делителя час"тоты и обеспечивает формирование им"пульсов Г 0 частотой 5 МГц и длительностью 100 нс и импульсов Р и Р 2 частотой 1 МГц и сдвинутых относительнодруг друга.Формирователь 7 сброса представ"ляет собой одновнбратор, формирующийимпульс К при включении питания.Двоичный счетчик 10 имеет инверс"ный счетный вход, поэтому информацияна его выходах появляется по заднемуфронту счетного импульса,Дешифратор 11 имеет четыре выхода,при этом на выходах образуются сиг"налы, когда на шине 26 появляютсяследующие адреса:0000 - ОРРР, - для первого выхода;1000 - 1 РРР, - для второго выхода;2000 " 20 ГГ, - для третьего выхода;21 00 - ЗРГГ,а - для четвертого выхода,В блоке 2 памяти хранятся инструкции РП, последовательность которыхвоспроизводит ступенчатую электрическую схему управляемого объекта. Каждая инструкция занимает объем двабайта в блоке 2, Блок 2 представляетсобой перепрограммируемое постоянноезапоминающее устройство (ППЗУ) и содержит ряд микросхем памяти типаК 573 РФ 5. Рабочая программа в микросхемы памяти записывается с помощьюотдельных средств, .которые не входятв ПК, Блок 2 адресуется операционнымблоком 1, когда на шине 26 формируется адрес от 2100 ь до ЗРРР .В блоке 3 памяти имеется область,в которой хранятся биты состоянийканалов вывода, другая область, в которой хранятся биты состояний каналов ввода, и третья область, котораяиспользуется операционным блоком 1для своих нужд, например цля хранения результатов диагностики и тестирования ПК. Блок 2 представляет собойоперативное запоминающее устройство(ОЗУ) и адресуется операционным блоком 1, когда на шине 26 формируетсяадрес от 2000,до 20 ГР .В блоках 4-1 и 4-2 памяти хранятся команды операционного блока 1, образующие алгоритм работы ПК, Блок4-1 выбирается адресами от 0000 доОРРРл, блок 4-2 - адресами от 10006до 1 РРР 4 е . Данные блоки представляютсобой постоянные запоминающие устройства (ПЗУ).ВОЛУ 5 (фиг.2) содержит регистр 39, триггеры 40-44, дешифраторы 45- 48, формирователь 49 импульсов, одновибратооы 50"52, мультиплексор 53, узел 54 двунаправленной передачи дан О ных, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 55, элемент И-НЕ 56 и 57,.элемент ИЛИ-НЕ 58, элементы И 59-83, элементы ИЛИ 82- 91, две группы по восемь элементов И-НЕ 92-99 и 100-107.15Вход 28 сброса связан с К-входом регистра 39, В.-входом триггера 40 и первым входом элемента ИЛИ 90, Вход 23 ЯУСС связан с первым входом элемента И-НЕ 56 вход 20 1 2 связан с вторым инверсным входом элемента ИНЕ 56, выход которого связан с С-входом (синхровходом) регистра 39, инверсным Я-входом триггера 40 и выходом 32 БТВ, Вход 21 0 В связан с пер выми входами элементов И-НЕ 58, И 59, И 60 и И 82, а также с входом режима чтения узла 54. Вход 32 ИК связан с вторым входом элемента ИЛИ-НЕ 58, первыми входами элементов И 61 и 81Двунаправленные информационные входы-выходы 36 связаны цепями 00,07 с информационными входами мультиплексора 53 и с выходами узла 54, цепями 00, 01 - с первым и вторым информационными входами дешифратора 45,35 цепями 02 - 05 - с четырьмя инверсными входами элемента И 83, цепями 06, 07 - с пятым и шестым входами элемента И 83 цепями 00 01 - с первым и вторым 0-входами (информационными входами) регистра 39., цепями 00 -07 - с первыми входами элементов И-НЕ 92-99.Адресные входы 27 связаны цепью АО со вторым входом элемента И 59, цепями А 11-А 13 - с информационными входами дешифратора 46, цепями А 8- А 10 - с первым, вторым и третьим входами элемента И 68, с информационными входами дешифратора 47 с информационными входами дешифратора 48 и адресными входами мультиплексора 53.Выход элемента ИЛИ-НЕ 58 связан с С-входом триггера 40, 0-вход которо 55 го связан с входом логического нуля а прямой выход - со стробирующим входом дешифратора 46, Первый выход регистра 39 связан цепью иО с входом режима записи узла 54, второй выход связан цепью обращения по стеку (ВТАСК) с третьим входом элемента И 59, выход которого связан с цепью С 1 со стробирующим входом дешифратора 45 и первыми входами элементов И 69 и 70. Выход элемента И 83 связан с третьим информационным входом дешифратора 45. Первый выход дешифратора 45 связан с первым входом элемента ИЛИ 84, второй выход - с вторым входом элемента ИЛИ 84 и цепью НАЧАЛО ВЕТВИ (НВТ) с первыми входами элементов И-НЕ 57, И 73, И 76, И 78, И 79. Третий выход дешифратора 45 связан с третьим входом элемента ИЛИ 84 и цепью КОНЕЦ ВЕТВЕЙ (КВТ) - с первыми входами элементов И 77, 80, Первый выход дешифратора 46 связан цепью -11- с первыми входами элементов ИЛИ 85 и ИСКЛЮЧАЮЩЕЕ ИЛИ 55, второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 55 связан с выходом мультиплексора 53, а выход - цепью СОСТОЯНИЕ (СОСТ) с первым входом элемента И 75. Второй выход дешифратора 46 связан цепью 4- с вторым входом элемента ИЛИ 85.Третий выход дешифратора 46 связан цепью -О- с первым входом элемента ИЛИ 86 и первыми входами элементов И 63, 67. Четвертый выход дешифратора 46 связан цепью -ф - с вторым входом элемента ИЛИ 86 и первыми входами элементов И 64 и 66 Пятый выход дешифратора 46 связан цепью -О в с третьим входом элемента ИЛИ 86 и с первым входом элемента И 62, шестой выход связан цепью в О с четвертым входом элемента ИЛИ 86 и с первым входом элемента И 65, Выход элемента ИЛИ 85 связан с вторым входом элемента И 50 и с первым входом элемента ИЛИ 87. Выход элемента ИЛИ 87 связан с выходом 30 переключения блокаВыход элемента И 50 связан цепью С 2 с четвертым входом элемента ИЛИ 84 и с первым входом элемента И 72. Выход элемента И 61 связан цепью С 4 с пятым входом элемента ИЛИ 84 и с первым входом элемента И 71, Выход элемента ИЛИ 84 связан цепью СО с входом запуска Формирователя 49 импульсов и с инверсным входом одновибратора 50, выход которого связан с выходом 29 сброса блока 5. Тактовый вход формирователя 49 импульсов связан с входом 18 блока 5, Первый выход формирователя 49 связан цепью ТЗс вторыми входами элементов И 69 и 72. Второй выход формирователя 49 связан цепью Т 4 с вторыми входами элементов И 70 и 71. Седьмой выход дешифратора 46 связан с четвертым входом элемента И 68, выход которого связан с входом одновибратора 51,вторыми входами элементов И 81, 82 и выходом 33 ВБР В/В блока 5, Выходы эле ментов И 62-64 связаны через элемент ИЛИ 88 со стробирующим входом дешифратора 48. Выходы элементов И 65"67 связаны через элемент ИЛИ 89 со стробирующим входом дешифратора 47. Инверсные выходы дешифратора 47 связаны соответственно с вторыми входами элементов И-НЕ 92-99, выходы которых связаны -соответственно с первыми входами элементов И-НЕ 100-107, Вторые входы элементов И-НЕ 100-107 связаны соответственно с инверсными выходами дешифратора 48, а выходы элементов И-НЕ 100-107 связаны с информационными входами узла 54. Двунаправлен ные входы-выходы .узла 54 связаны с ШД 48 ЭПО-ЭВ 7. Выходы элемента И 69 связаны с вторыми входами элементов И 73, 76 и 80, Выход элемента И 70 связан с вторыми входами элементов И 77, 79 и вторым входом элемента ИНЕ 57. Выход элемента И-НЕ 57 связан с С-входом триггера 42, прямой выход которого связан с третьими входами элементов И 76, 79, обратный выход -35 с его О-входом, третьим входом элемента И 73 и первым входом элемента И 74, Выход элемента И 71 связан со вторым входом элемента И 74, выход которого связан с вторым входом эле мента ИЛИ 90, а выход последнего - с К-входами триггеров 42 и 43, первым К-входом триггера 44 и с первым 8- входом триггера 41. Выход элемента И 73 связан с С-входом тригге 1 ра 43, 45 прямой выход которого связан с вторым входом элемента И 78. Выход элемента И . 76 связан с С-входом триггера 44, прямой выход которого связан с тре- . тьим входом элемента И 80 и с первым входом элемента ИЛИ 91. Выход элемента ИЛИ 91 связан с В-входом триггера 44, второй Е-вход которого связан с выходом элемента И 77. Выходы элементов И 78-80 связаны соответст 55 венно с В-входом, С-входом и вторым 8-входом триггера 41. Выход элемента И 72 связан с вторым входом элемента И 75 выход которого связан с Е-входом триггера 41, а прямой выход по"следнего связан с 0-входом триггера43, вторым входом элемента ИЛИ 91 ицепью РЕЗУЛЬТАТ (РЕЗ) - со вторымивходами элементов И 62, 63, 65, 66 иинверсными вторыми входами элементовИ 64, 67. Выход элемента И 62 связанс выходом 35 ввода блока 5, инверсный выход одновибратора 51 связан стретьим входом элемента И 81 и инверсным входом одновибратора 52, выход которого связан с четвертым входом элемента И 81 и выходом 32 ГТблока 5. Выход элемента И 81 связанс выходом 31 вывода блока 5.Регистр 39 представляет собоймикросхему типа К 155 ТМ 8. Формирователь 49 импульсов состоит иэ пере"счетной схемы (счетчика) и элементовИ, что обеспечивает выделение, напри"мер, третьего и четвертого импульсовиз последовательности импульсов Е 0под действием запускающего сигналаСО (временные диаграммы работы формирователя, изображенные над ним).Узел 54 двунаправленной передачи данных представляет собой переключательшин с тремя состояниями на выходах иможет быть выполнен на двух микросхемах типа К 589 А 1116, Мультиплексор 53обеспечивает выборку одного типа избайта, передаваемого по шинам ЭО-Р 7,по адресу, укаэанному кодом в шинахА 8-А 10, Одновибраторы 51 и 52 обеспечивают формирование импульсов длительностью примерно 6 и 8 мкс соответственно,.Входы и выходы элементов и блоков11 К имеют следующее назначение.Сигнал РО по цепи 18 (фиг.1)обеспечивает работу ВОЛУ 5, а именно образование на выходе формирователя 49 импульсов (фиг,2) двух импульсов ТЗ и Т 4 длительностью по100 нс (временные диаграммы работыформирователя 49, фиг,2).Сигналы Р 1 и Р 2 по цепям 19 и20 обеспечивают синхронизацию работы операционного .блока 1, Кроме того, сигнал Р 2 обеспечивает совместнос сигналом ЯУСС (сигнал начала циклас выхода 23 операционного блока 1)образование на выходе элемента И-НЕ 56 импульса ЗТВ.Сигнал РВ по цепи 21 формируетсяоперационным блоком 1 при считыванииинформации с шины 24 00-07 в операционный блок 1 и активизирует работуузлов ПК для выдачи информации в операционный блок.Сигнал ЪЖ по цепи 22 Формируется операционным блоком 1 при выдаче информации с операционного блока 1 вшину 24 и активизирует работу узловПК,Сигнал 8 гБС по цепи 23 Формируется операционным блоком 1 всякий раз,когда начинается машинный цикл обработки команды в операционном блоке(фиг.З), Сигнал БгЖС обеспечиваетсинхронную работу БОЛУ 5 с выполнением команд в операционном блоке 1,Сигнал Б. по цепи 28 Формируетсяпри включении питания ПК и обеспечивает установку узлов ПК в исходноесостояние,Сигнал сброса операционного блока1 по цепи 29 образуется в БОЛУ 5 позавершении обработки инструкции ВХОД,ВЫХОД, ВЕТВЬ. Данный сигнал обеспечивает ускоренный переход операционного блока 1 на обработку следующейинструкции РП, минуя выход из обработки через подпрограмму перехода. На выходе 30 БОЛУ 5 формируетсясигнал переключения коммутатора 12,чем обеспечивается адресация операционного блока 1 к блоку 3 памяти,если сигнал имеет состояние лог. "1"или адресация к блоку 2, 4-1 или 4-2памяти если сигнал имеет состояние лог, "О",Сигнал БТВ по цепи 31 синхронизи-.рует начало работы БОЛУ 5, а такжепроцесс установки операционного блока 1 в режим ожидания и выход из не-гоСигнал ГТ по цепи 32 ФормируетсяВОЛУ 5 для установки операционногоблока 1 в режим ожидания, что осуществляется при передаче информациис блока 3 памяти в каналы вывода ПКи при приеме информации с каналовввода в блок 3 памяти.Сигнал ВБР/В/В на выходе 33 фор-мируется при обращении ПК к каналамввода-вывода. и активизирует их ра-.боту,Сигнал вывода на выходе 34 формируется при выдаче информации с ПКв каналы вывода и обеспечивает запись информации, например, в регистры моделей вывода.Сигнал ввода на выходе 35 Форми-.руется при приеме байта информации в ПК с каналов ввода и обеспечиваетсинхронизацию их работы.Сигналы ИО и ВТАСК, образующиеся на выходах регистра 39, являютсясигналами слова состояния операционного блока 1. Сигнал УО обусловливает работу операционного блока 1 повыводу информации из него и активизирует работу узла 54 двунаправленной передачи данных. Сигнал ЗТАСКобусловливает считывание информациив операционный блок по адресу, указанному в его внутреннем стековомрегистре, и обеспечивает формирование управляющего сигнала с дешифратора 45 при выполнении операционнымблоком 1 первой команды РОР Н обработки инструкции РП,20 Сигнал С 1 с выхода элемента И 59обеспечивает работу узлов ВОЛУ 5 приобработке инструкции группы ВЕТВЬ.Сигнал С 2 с выхода элемента И 60обеспечивает работу узлов ВОЛУ 5 при25 обработке инструкции группы ВХОД..Сигнал С 4 с выхода элемента И 61обеспечивает работу узлов БОЛУ 5 приобработке инструкции группы ВЫХОД.Импульсы ТЗ и Т 4 с выходов форми 30 рователя 49 импульсов обеспечиваютпоследовательность срабатывания от"дельных элементов ВОЛУ 5.Сигнал РЕЗ с выхода триггера 41обусловливает результат обработкипоследовательности инструкции РН,образующих одну логическую цепь.Сигнал СОСТ с выхода элементаИСКЛЮЧАЮЩЕЕ ИЛИ 55 обусловливает результат обработки инструкции ВХОД.Сигнал, образующийся на выходемультиплексора 53, обусловливаетсостояние анализируемого канала ввода и называется битом состояния канала ввода.Сигнал, образующийся на выходеэлемента ИЛИ 88, обеспечивает установку в состояние лог. "1" обрабатываемого канала вывода. А сигнал, образующийся на выходе элемента ИЛИ89, обеспечивает установку обрабатываемого канала вывода в состояниелог. "0".Работает ПК следующим образом.После включения питания одновиб"ратор 7 формирует импульс К, уста"навливающий триггеры 9, 44, 40 и 42,счетчик 10, регистр 39 и операционный блок 1 в состояние лог. 0 , аи и 3триггер 41 - в состояние лог. ,5, элементы И-НЕ 92-107 на информа"ционные входы узла 54, Посредствомсигналв ИО (лог. "1") и 0 В (лог. 0")узел 54 передает код 00 Б на выходы37 0 В 0-0 В 7, а выходы 00-07 устанавливают в третье высокоимпедансное состояние. Код 00 поступает черезшину 38 в блок 3 и под действием сигнала МВ. по цепи 22 записывается в соответствующую ячейку. Таким образом,происходит очистка всех ячеек блока 3.После очистки блока 3 операционный блок 1 переходит на подпрограммутестирования блока 2 памяти на несуществующие инструкции РП(фиг.5 и 7).При этом операционный блок 1 в шину26 выставляет адреса от 2100 доЗРРР и Формирует в цепи 21 сигнал0 В, посредством чего с блока 2 в шину 38 поступает байт считываемой информации. Данный байт поступает навходы 37 ВОЛУ 5, Посредством сигналов ЫО (лог. "0") и 0 В (лог, "1")блок 54 передает считанный байт свходов 37 на свои выходы 36 00-07.Таким образом, данный байт поступает на выходы БОЛУ 5 и через шину 24 -в операционный блок 1,В следующей подпрограмме (фиг,5,8 и 9) обрабатывается контрольнаяРП. Контрольная РП содержит все инструкции, из которых строится РП, Процесс обработки инструкций поясняетсяниже, В контрольной РП имеется специальная конструкция, посредством которой обеспечивается выход операционного блока 1 из обработки контрольной РП. При положительном результатетестирования операционный блок 1 переходит на подпрограмму обмена информацией с каналами ввода-вывода, причем сначала осуществляется передачаинформации (в первом цикле обмена инФормацией являются коды 00 ) из области состояний каналов вывода блока3 в каналы вывода ПК, а затем приеминформации из каналов ввода ПК и зались ее в область состояний каналовввода блока 3.Каналы ввода-вывода подключаютсяв ПК посредством шины 26 и шины 24соответственно своими адресными шинами и шинами данных,Передача информации в каналы вывода осуществляется следующим обра.зом (Фиг.10). Операционный блок 1считывает из соответствующей области 11 ри этом в цепи 30 устанавливается сигнал лог, "0" и коммутатор 12 на" ходится в исходном состоянии. В цепи 32 ГТ будет лог. "0" поэтому на ин ф5 версном выходе триггера 8 будет лог. , чем обеспечивается разрешение работы операционному блоку 1. Операционный блок 1 формирует на своих адресных выходах код 0000 а, Данный код передается по шине адреса 26 в дешифратор 11, на первом выходе котоИ И рого образуется сигнал лог. 1, Данный сигнал проходит через рткрытьм триггером 9 элемент И "15", элемент ИЛИ "17", на вход считывания блока 4-2, Вследствие этого на первой ячейке блока 4-2 считывается первый байт команды, который поступает по шине 24 в операционный блок 1. Операционный блоктакже формирует сигнал 0 В, который по цепи 21 поступает на счетный вход счетчика 10, Далее операционный блок 1 Формирует адреса 0001 и 0002 и аналогичным образом считы вает два следующих байта команды из блока 4-2, При этом после третьего импульса 0 В на первом и втором выхо 11 й дах счетчика 10 образуются лог, 1 благодаря чему на выходе элемента И 30 13 будет лог"1" и триггер 9 уста 111 н авлив ае т ся в состояние ло г . 1 Посредством этого элемент И5 з ак рывае т ся , а открывается элемент И 1 4 .Первой командой , считанной в опер ационный блок 1 иэ блока 4 - 2, является тр ехб ай то в а я команда 1 ЙРА 0 К ( б е з у сло в ный переход и о адресу , указ анно му в команде) , посредством которой опе р ацио нный блок 1 переходит 4 О на подпрограмму очистки блока 3 памяти (фи г . 5 и 6 ) . В начале обработки каждой команды операционный блок 1 на своих информационных выходах устан авлив а е т коц слова состояния и фор миру е т импульс БУ БС в цепи 2 3 . Под действием импульсов ЯУ БС и Р 2 на выходе элемента И- НЕ 5 6 образуется сигн ал Б ТВ , который поступает на С- вход регистра 3 9 и в последние записываются два первых разряда кода слова состояния , Когда операционный блок 1 для очистки ячеек блока 3 в шину 2 6 выставляет адрес от 2000 до 20 РР, а в шину 24 выставляет код 00, и формирует сигнал ЧК в цепи 22, то на первом выходе регистра 39 будет сигнал ЧО (лог, "0") и код 00, переда-ется из шины 24 через входы 36 БОЛУ

СмотретьЗаявка

3810000, 10.11.1984

ПРЕДПРИЯТИЕ ПЯ А-1477

СКЛЕМА МИХАИЛ ВАСИЛЬЕВИЧ, ВИТКОВСКИЙ ИГОРЬ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G06F 15/00, G06F 9/00

Метки: контроллер, программируемый

Опубликовано: 23.01.1989

Код ссылки

<a href="https://patents.su/18-1453404-programmiruemyjj-kontroller.html" target="_blank" rel="follow" title="База патентов СССР">Программируемый контроллер</a>

Предыдущий патент: Генератор случайного марковского процесса

Следующий патент: Устройство управления обращениями

Случайный патент: Устройство для транспортирования материалов с помощью транспортирующей среды под давлением