Генератор символов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1550572

Авторы: Аноприенко, Башков, Коба

Текст

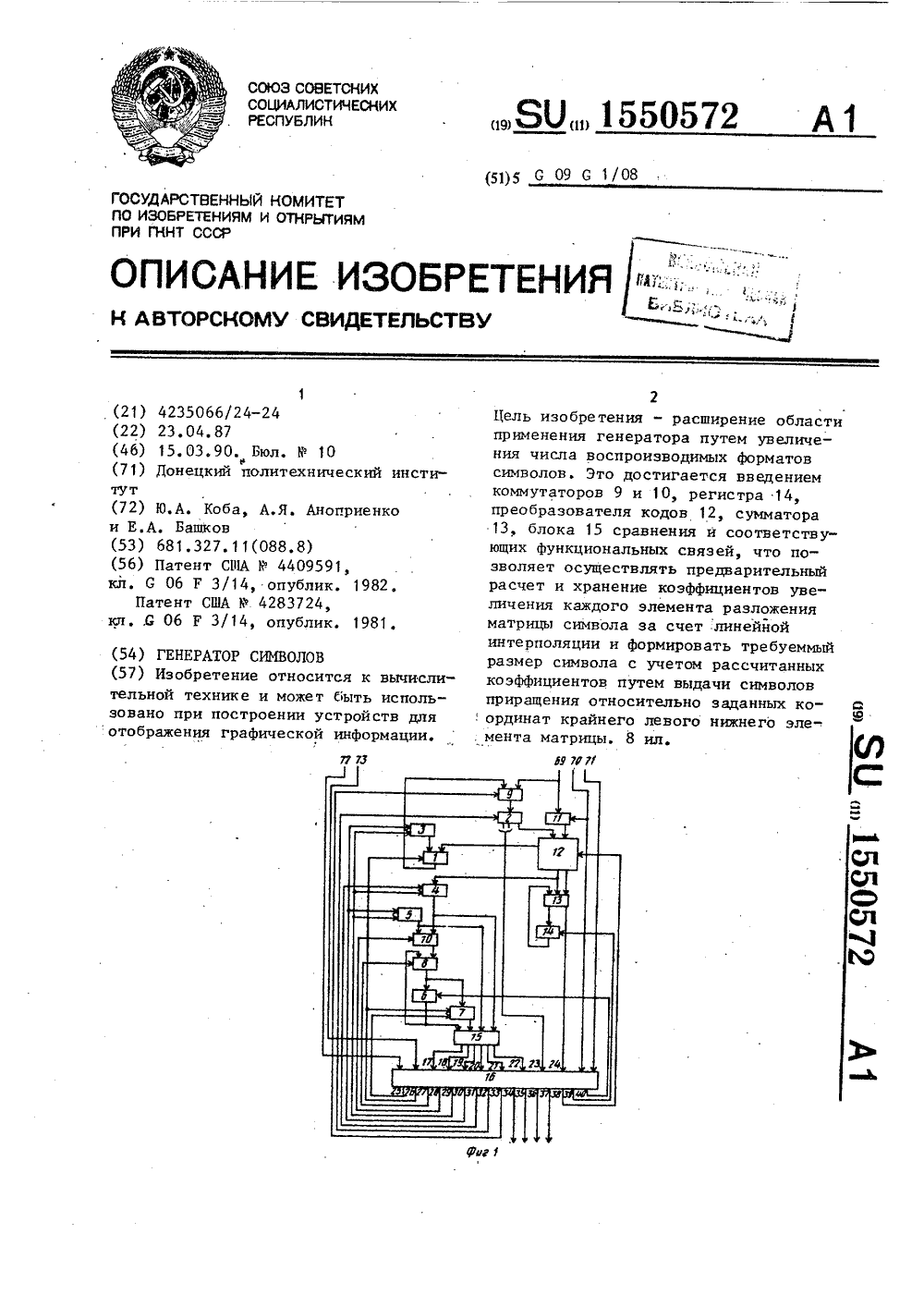

(54) ГЕНЕРА (57) Изобре тельнои те ет бь е испол ии устской ин при построения графич зован отобр иств формации,кз ОСУДАРСТ 8 ЕННЫЙ НОМИТЕТО ИЗОБРЕТЕНИЯМ И ОТНРЬГГИЯМРИ ГННТ СССР АНИЕ ИЗОБР(56) Патент США4кл. С 06 Р 3/14, опПатент США428клС 06 Р 3/14, оп СИМВОЛОВе относится к вычисли 1550572 А Цель изобретения - расширение области применения генератора путем увеличения числа воспроизводимых форматов символов, Это достигается введением коммутаторов 9 и 1 О, регистра 14, преобразователя кодов 12, сумматора 13, блока 15 сравнения и соответствующих функциональных связей, что позволяет осуществлять предварительный расчет и хранение коэффициентов увеличения каждого элемента разложения матрицы символа за счет линеййой интерполяции и формировать требуеммый размер символа с учетом рассчитанных коэффициентов путем выдачи символов приращения относительно заданных координат крайнего левого нижнего эле. мента матрицы. 8 ил.О Ю 7/та счетчика 4 (30-й разряд ПЗУ МК 41). В этом же такте осуществляется анализ признака равенства содержимого счетчика 4 константе (М) "Ст 2=(М)"У формируемого блоком 15. Если "Ст 2= =(М)"=О, то осуществляется переход на МК по адресу 11100 (на блок Я 4 ). При "Ст 2=(И)"=1 производится переход на МК по адресу 01011, т.е, на ввод следующего кода символа (блок О 9) ). При .необходимости изменения Формата генерируемого символа или окончания работы генератора выход из цикла осуществляется по сигналу "Сброс". Во всех МК, где блок 8 и сдвиговый регистр 2 не задействованы,. они находятся в режиме хранения, что достигается подачей сигналов на их управляющие входы с 34-го, 35-го и Яб-.го, 27-го разрядов ПЗУ МК 41.Предлагаемый генератор символов произвольного формата позволяет увеличить области применения таких устройств за счет увеличения числа воспроизводимых Форматов по сравнению с существующими устройствами для генерации символов. торого соединен с первым информационным входом преобразователя кодов,второй информационный вход которогосоединен с выходом первого регистра,5второи выход сдвигового регистра подиключен к первому информационному входу блока управления, второй информационный вход которого соединен с первым выходом сумматора, второй выходкоторого подключен к информационному входу второго регистра, выход которого соединен с первым информационным входом сумматора, второй и третийинформационные входы которого соединены с первым и вторым выходами преобразователя кодов, второй выход которого подключен к информационному входучетвертого счетчика, а третий выход -к первому адресному входу блока постоянной памяти, второй адресный входкоторого соединен с выходом первогосчетчика, а выход - с вторым информационным входом первого коммутатора,выходы второго и третьего счетчиковподключены к первому и второму информационным входам второго коммутатора,соединенным соответственно с первыми вторым входами блока сравнения,третий и четвертый входы которогоподключены соответственно к выходамчетвертого и пятого счетчиков, выходчетвертого счетчика подключен к информационному входу блока оперативной35памяти, адресный вход которого соединен с выходом второго коммутатора,а выход - с информационными входамичетвертого и пятого счетчиков, с первого по шестой выходы блока сравненияподключены соответственно к управляющим входам с третьего по восьмойблока управления, выход второго регистра соединен с третьим информационнымнходом сумматора, первый выход блокауправления подключен к первому управляющему входу пятого счетчика, второй выход в , к нторому управляющемувходу пятого счетчика и унравляющемувходу блока постоянной памяти, третий50выход - к управляющему входу блокаоперативной памяти, четвертый выход -к управляющему входу второго коммутатора, пятый выход - к первым управляющим входам .третьего, второго и 5первого счетчиков, шестой выход -к вторым управляющим входам третьегои первого счетчиков, седьмой выход -формула изобретения Генератор символов, содержащий блок постоянной памяти, сдвиговый регистр, с первого по пятый счетчики, блок оперативной памяти и блок управления, о т л и ч а ю щ и й с я тем, что, с целью расширения области применения генератора за счет увеличения числа воспроизводимых форматов символов, генератор содержит первый и второй коммутаторы, первый и второй регистры, преобразователь кодов, сумматор и блок сравнения, первый информационный вход первого коммутатора и информационный вход первого регистра являются информационным входом генератора, входом сигнала управления записью координаты Х которого являются управляющий вход первого регистра и первый управляющий вход блока управления, второй управляющий вход которого является входом сигнала управления записью координаты У генератора, входом сигнала сброса и входом синхросигнала которого являются вход сброса и синхровход блока управления, выход первого коммутатора подключен к информационному входу сдвигового регистра, первый выход кок второму управляющему входу второго счетчика, восьмой и денятый выходы -к управляющим входам сдвигового регистра и первого коммутатора соответственно, с десятого по тринадцатыйвыходы являются с первого по четвертый выходами генератора, четырнадцатый, пятнадцатый и шестнадцатый выходы блока управления соединены соответственно с управляющими входами преобразователя кодов, второго регистра и четвертого счетчика,%Ъ"фР"фФ ч вф,Ф . ЧОО ОО Оооь. ь ь, О фсь,ь,о ООООО ОО ьОО оО ООО ОО ООО ОО ООС 5 оо - оъ ОЮ ОО ооо ОО ОООО О ООООО ОО ООО ОО ООО ьо ОО оо ъф" ф Оь,аоо ОО ООО ооой о яооо ОО се О О ОООО ООВОО О ОьООООкООООООьОООО ЪОЮО О ОООО О ОООО ьо ьОО ч ь, ь с О ьь О О ь ъс ь ь Очсс ч ь О ь О о ь ъъльолъьл ,%,ь,ъ,ъльюис.ъььььефсс ООООО ОООО ОООО" О ООООООО ОО О ОООО ОО ОООО ОООО ООООООООООООООкОООООО ОЮООЯООь Оьа ООО О ОООО ОООО ООО ьООО ьОООООООО . ООООЮ О ОООООь ОООООьОООООООО О ОООО ОООлООл ООООЬООО ОЬООО ОООООООаъ Обл ОЮОООООО Оь Ооа ООООО ОООООО ОООО ьОООьоь ООО ЪОООООЮОь ООООЪОООООО ОьООО О ОООО ООООООО 0 ьооо О О ьОь ОО О О ОООЮ ООООО.О ОьОООООО ОоьООО ОООООООООООО Ооаьою ООООь О ОО ь О ООООООООО ОООО ООООО О Фе Отса ООООООООООО ООООООООО О Оььь О ОООО ОО О ОООО О О О ОООО О О О ОООООООООООООООООООООО ОО ООООООООООь ООООкОООООООООО О О О О О О О О ОО О Ю ОО О О В О О О О О О О ОООьоо ОООО О О ООООО О ОО ОООО О О ооъоовоо о О ооооа ооа оооо о О ООООООООООьОЪООО ьЮОО ОООьООООО, О О О О О ь. О О О О. О О О О О ОО О О ь а О ь О О О ООО ОО ь О О О О О О О О О О О О О ОО О О О ь О О О ООООООООкО ОООООО ОООО ь О О ьОО О О О О О % О О О ОО % О О ь " " О О ьЮ О О к О Ъ к О ФьО ОООО ООЪь ЮО 1 ь О Оь ьО ОоьООО,к,ьсЬОЪъ ООО О О О О ь ОО О О О. к к к , к О ЪФ.О ъ, О Оь ь,. ОООЮ ООО ъ, ььь ьОООО ,ь,О, ь, О О О ЮО О Ю О О % О О О Ъ Ъ Я ьь ь. ь ь, О О к" ь,ООО%ОООО . ООЮаоОООЮ ООЪООООО ооъьооо ооооо ювао ь ооо ьооьооО О О О Ъ Ъ Ь О Ъ Ъ О % О Ю ьЪ Ю ь О О О О О О ь, ,ОО ь О О О Ос О О ъ, О О О ь. с ь (: ь О е О ь, ООЬОООО О%ооь ОООООкООООьОООО ьлоаОО"ЮОООО ООО"ьООООООО ькФ О О О О О О О Ъ О О О О О О Олль . ь ьл ь ьл ь ь,1550572 оставитель И. Загинайкехред А,Кравчук тор С. Черни Редактор Е. Коп К Тир ретениям ушская н изводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагари Заказ 276 НИИПИ Гос енного коми13035, Мос 388ета по иа, Ж,дписноеткрытиям при ГКНТ д. 4/5Изобретение относится к вычисли"тельной технике и может быть использовано при построении устройства дляОтображения графической информации.Цель изобретения - расширение об 5ласти применения генератэра. за счетувеличения числа воспроизводимых Форматов символов,На фиг. 1 представлена структурая схема генератора; на фиг, 2 -труктурная схема блока управления;а Фиг. 3 - структурная схема преобазователя кодов; на фиг. 4 - струкурная схема блока сравнения- на 15г. 5 - таблица прожига ПЗУ микроманд блока управления; на фиг 6-8 -икропрограмма работы устройства.Генератор символов содержит блок1 постоянной памяти (разложения матиц символов), сдвиговый регистр 2,ервый 3, второй 4, третий 5, четвертый 6 и пятый 7 счетчики, блок 8 огеративной памяти (параметры генерируемого символа). первый 9 и второй 10 25коммутаторы, первый регистр 11, преобразователь 12 кодов, сумматор 13, вторзй регистр 14, блок 15 сравнения,блок 16 управления.Позициями 17-24 обозначены соотЙтствующие входы, а 25-40 - соответствующие выходы блока 16 управления,Блок 16 управления содержит ПЗУ 41рокоманд, регистр 42 адреса, комтаторы 43 и 44, элементы И 45-48,эпементы ИЛИ 49-51, триггер 52.35Позициями 53-58 обозначены соотвэтствующие входы и выходы в блоке 16.Преобразователь 12 коцов содержитформирователь 59 константы М, Формиро ватель 60 константы И, коммутаторб 1, Формирователь 62 обратного кода,Позициями 63 и 64 обозначены входыкэммутатора 61,Блок 15 сравнения содержит узел65 сравнения с нулем, узел 66 сравненйя с константой М, узел 67 сравненияс константой (М + И + 1) и узел 68сравнения с константой (М).Блок 1 постоянной памяти предназиачен для хранения битового разло 50жЕнил матриц всех генерируемых симвОлов с возможностью считывания при.подаче соответствующего адреса и управляющего сигнала.Сдвиговый регистр 2 служит дляприема и хранения размера символав единицах растра по вертикали, атакже приема, хранения и сдвига вправо-влево считанной информации из блока 1, Все действия выполняются по сигналу, формируемому элементом Ю 1 И 50.Первый счетчик 3 представляет собой счетчик по модулю М и предназначен для, Формирования младших разрядов адре,са блока 1 разложения мат" риц символов,Второй 4 и третий 5 счетчики служат для Формирования адреса считывания-записи блока 8 оператйвной памя- тИ аЧетвертый 6 и пятый 7 счетчики являются вычитающими и предназначены для приема из блока 8 оперативной памяти масштабного коэффициента по координате У и Х соответственно иаего последовательного уменьшения на единицу.Блок 8 оперативной памяти служит для приема и хранения масштабных коэффициентов,каждого элемента матрицы разложения по координатам Х и У. Емкость его составляет (М + И) ячеек памяти.Позициями 69-73 обозначены соответственно информационный вход, входасигналов управления записью координат Х и У, вход сигнала сброса и вход синхросигнала генератора.Коммутатор 9 предназначен для коммутации на сдвиговый регистр 2. информации, поступающей либо с входа 69, либо с выхода блока 1 под действием управляющего сигнала с выхода 33. блока 16. Коммутатор 10 служит для коммутации адреса считывания-записи блока 8 оперативной памяти, поступающего либо с выхода счетчика 4, либо с выхода счетчика 5 под действием управляющего сигнала с выхода 28 блока 16 управления.Регистр 11 осуществляет прием и хранение размера символа в единицах растра по горизонтали, а также прием и хранение кода генерируемого символа, который служит в качестве старших разрядов адреса блока 1 разложения матриц символов.Преобразователь 12 кодов предназначен для формирования коснтант М и И, коммутации коммутатором 61 под действием управляющих сигналов с блока 16 управления информации с четырех направлений на одно со сдвигово-.1550572 20 го регистра 2, регистра 11, формирователей 59 и 60 констант М и И, а также получения обратного кода числа и возникающего переноса с помощью формирователя 62 обратного кода под действием управляющего сигнала с вхо-. да 63.Сумматор 13 служит для суммирования информации, поступающей с преоб разователя 12 и регистра 14 с учетом переносаРегистр 14 осуществляет запись и хранение результата суммирования, поступающего с сумматора 13.Блок 15 сравнения предназначен для Формирования признаков выполнения операций, которые анализируются в блоке 16 управления, причем узел 65 сравнения с нулем вырабатывает признаки "Ст 4=0" и "Ст 5=0", узел 66 сравнения с константой М - признак "СтЗ=М", узел 67 сравнения с константой (М + И. + 1) формирует признаки "Ст 3=(М + И+ 1)" и "Ст 2 - (М + И+ 1)", 25 а узел 68 сравнения с константой (М) - признак "Ст 2=(М). В блоке 15 вырабатывается сигнал в результате суммирования поступающей информации на сумматоре 13 и является знаком 30 этой суммы ЗнБлок 16 управления необходим для управления работой генератора путем выдачи управляющих сигналов с учетом анализа сформированных признаков.Таблица прожига ПЗУ МК 41 представлена на фиг. 5.Устройство работает следующим образом.В основу процесса определения ко эффициентов увеличения каждого элемента разложения матрицы символа по координате Х положена линейная интер= поляция диагонали прямоугольника со сторонами по горизонтали и вертикали 45 соответственно йХ и М, где ЬХ - размер поля генерируемого символа; М - размер стандартной матрицы этого символа, хранимый в блоке 1, по горизонтали в единицах растра Опреде ление коэффициентов увеличения каждого элемента разложения матрицы символа по координате 7 производится аналогично, но для диагонали прямоугольника со стороны соответственно В и Ь 7, где И - размер стандартной матрицы, хранимой в блоке 1; ЬУ - размер поля генерируемого символа по вертикали в единицах растра. Под полем генерируемого символа понимается прямоугольная область экрана с размерами сторон д Х, йУ, в которую необходимо "вписать" символ. Очередной шаг интерполяции выбирается при анализе знака оценочной функции Р: если на 1-м шаге Р.;О, то делается шаг по Х и Р; = Р; - д У; если Р; ( О, то шаг по У и Р; = Р 1+В исходное состояние генератор устанавливается по входу 72 сигналом "Сброс", При этом обнуляется триггер 52 и регистр 42 адреса микрокоманд (МК), что приводит к установлению логического "0" на управляющем входе регистра 42 М и считыванию с нулевой ячейки ПЗУ МК 41 первого слова МК (фиг. 5), Поскольку нулевой разряд МК равен нулю, ЗпХ=О, ЗпУ=О, то на информационном входе триггера 52 элементом ИЛИ 51 формируется логический "0", который будет записываться по переднему фронту сигнала СИ в каждом последующем такте, что приведет к удержанию логического "0" на управляющем входе регистра 42 адреса до прихода сигналов ЗпХ, ЗпУ по входам 70 и 71. С инверсного выхода триггера 52 логическая "1" подается на вход элемента И 45, разрешая передачу сигнала ЗпХ на вход элемента . ИЛИ 51, Таким образом, генератор перейдет в состояние ожидания прихода внешних сигналов ЗпХ, ЗпУ. Коммутатор 43 подключает на свой выход один из восьми информационных сигналов "0", 24, 19, 20, 17, 21, 18, 22 в зависимости от управляющего поля (УП) МК (разряды - 1-3 ПЗУ МК 41, фиг. 5). Поскольку в нулевой ячейкеПЗУ МК 41-УП-ООО, то коммутатор 43 выдает на свой выход логический "0". Коммутатор 44 под действием этого сигнала подключит на свои выходы адресное поле (входы) 57, т.е. адрес следующей МК=00001, который будет удерживаться на входе регистра 42 адреса до прихода переднего фронта сигнала с выхода 54 элемента И 46.Установка размера поля генерируемого символа осуществляется следу-"ющим образом (фиг, 6, блок 2), По приходу сигнала ЗпХ, который как и ЗпУ может быть асинхронным по отношению с СИ, на информационном входе триггера 52 через элементы И 45 и ИПИ 51 устанавливается логическая11, которая записывается в триггер 52 по ближайшему переднему фронту сигнала СИ (Фиг, 7), что ведет к формированию на информационном входе триггера 52 логического "0", так как инверсный выход этого триггера 52 запрещает действие сигнапа ЗпХ, а улевои разряд считанной по адресу 0000 МК равен О Одновременно логи"-. 11 и10 еская 1 с выхода 53 триггера 52 разешает прохождение сигнала СИ через лемент И 46; По переднему фронту формированного импульса в регистр 42 адреса записывается адрес 0000115 йо которому осуществляется выборка следующей МК из ПЗУ МК 41, Поскольку УП=ООО, то коммутатор 43 передает Йа управляющий вход коммутатора 44 Йогичес 1 сий "О", который под действим этого сигнала Формирует на входе20 регистра 42 адреса адрес 00010, По переднему фронту сигнала ЗпХ осуществляется запись значения Д Х, установленного ранее на входе 69, регистр 9 этом же такте осуществляется обнуление регистра 14 по сигналу с 18-го азряда ПЗУ МК 41 (блок 4, фиг. 6). о переднему Фронту очередного сигнаа СИ в триггер 52 запишется логичес кий "0", который запретит подачу СИ а управляющий вход регистра 42 адреса - генератор перехоцит в состояние ожидания, По приходу сигнала Зп 7 (.блок 5) на выходе элемента ИЛИ 51 формируется логическая 1 , которая 31, и35 Записывается в триггер 52 по переднему фронту сигнала СИ, что разрешает Его подачу на управляющий вход регистфа 42 адреса, куда записывается адрес 00010. По этому адресу из ПЗУ МК 4140 Вчитывается очередная МКу которой нулевой разряд равен "1"Этот сигйал через элемент ИЛИ 5 1 передается на информационный вход триггера 52,45 Одновременно коммутатор 9 под действием управляющего сигнала с 25-го разряда ПЗУ МК 41 (логический "О") в соответствии с Фиг. 5 коммутирует на йнформационный вход сдвигового регистра 2 информацию с входа 69. На управ 50 ляющий вход этого регистра поступают сигналы с 26-го и 27-го разряда ПЗУ МК 41, которые настраивают сдвиговый регистр 2 на режим записи. По сигналувыхода элемента ИЛИ 50, равному 1 (так как Злу=1), Й У, скоммутированное на вход сдвигового регистра 2 коммутатором 9, записывается в сдвиговый регистр 2 (блок б, фиг. 6), Одновременно по сигналам с 14-го и 32-го разряда ПЗУ МК 41 обнуляются четвертый 6 и третий 5 счетчики, а по сигналам с 20-го и 21-го разрядов преобразователь 12 осуществляет коммутацию с выхода регистра 11 на вход сумматора ",3, где и происходит суммирование. Указанная коммутация производится следующим образом. Сигналы с 20-го и 21-го разрядов ПЗУ МК 41, объединенные в третью группу выходов 38 блока 16 управления, поступают на управляющие входы 63 и 64 (фиг. 3) коммутатора 61, который осуществляет коммутацию выхода регистра 11 на вход формирователя 62 обратного кода. Поскольку сигнал с 20-го разряДа ПЗУ МК 41 (управляющий вход 63) равен "0", то формирование обратного кода и переноса не производится и Формирователь 62 пе" редает скоммутированный код на вход сумматора 13 без изменения. Результат суммирования по сигналу с 19-го разряда ПЗУ МК 41 записывается в регистр 14. В следующем такте по переднему фронту сигнала СИ в триггер 52 записывается "1"., что разрешает подачу СИ на управляющий вход регистра 42 адреса, куда записывается 00011. По этому адресу из ПЗУ МК 41 считывается МК, поле управляющих сигналов которой содержит управляющие сигналы для преобразователя 12, сдви гового регистра 2 и счетчика 6. Преобразователь 12 коммутирует на вход сумматора 13 обратный код константы М с сформированным переносом, который.используется для получения на сумматоре 13 дополнительного кода константы М в процессе суммирования с содержимым регистра 14.Коммутация и формирование обратного кода с переносом производится следующим образом. Сигналы с 20-го и 2 1-го разрядов ПЗУ МК 41 поступают на управляющие входы 63 и 64,Фиг. 3) коммутатора 61, который осуществляет коммутацию выхода формирователя 59 константы М на вход Формирователя 62 обратного кода, Поскольку сигнал с 20-го разряда ПЗУ МК 41 (управляющий вход 63) равен ф 1 ффто происходит формирование обратногокода константы М и переноса, которые поступают на соответствующие входысумматора 13, В результате суммирова"ния обратного кода константы М, переноса и содержимого регистра 14 суммы получается разность регистр 14суммы - формирователь кода М (РС-ФКМ),которая по сигналу с 19-го разрядаПЗУ МК 41 запишется в регистр 14, Посигналу с 15-го разряда ПЗУ МК 41 к содержимому счетчика 6 прибавляется 1 (блок 7, фиг. 6). В этом же такте знак суммы (Зн 7) с выхода сумматора 13 поступает в блок 16 управления на вход коммутатора 42, который передает его на управляющий вход коммутатора 44, (так как УП=001). Если Зн Х =0 (результат суммирования положительный), то коммутатор 44 скоммутирует на вход регистра 42 адресаадресное поле, соответствующее группе выходов 57 ПЗУ МК 41 и равное00011, т.е. происходит зацикливание блока 7 (фиг. В) до достижения условия ЗН 1 =1 (результат суммирования отрицательный). Если Зн= 1, то коммутатор 44 передает на вход регистра 25 42 адреса адрес 00100, что соответствует переходу на блок 9. В следу. ющем такте после считывания из ПЗУ МК 41 по адресу 00100 очередной МК осуществляется запись содержимого счетчика 6 в блок 8 оперативной памяти по адресу, хранящемуся в счетчике 5, а также прибавление содержи. мого регистра 14 с содержимым регистра 11 и запись результата суммирования в регистр 14. Выполнение блока 935 означает окончание вычисления очередного (в данном случае первого) коэффициента увеличения для элемента стандартной матрицы символа по координа те Х. Это достигается формированием сигнала записи БОП 8 коммутацией коммутатора 10, коммутацией преобразователя 12 и формированием сигнала записи регистра 14 на 19-м разряде ПЗУ МК 41.45 В следующем такте (блок 10) очередная МК считается по адресу 00101, где происходит обнуление счетчика 6 по сигналу с 14-го разряда ПЗУ МК 41 и прибавление +1 к счетчику 5 по сигналу с 31-го разряда ПЗУ МК 41.50 В этом же такте содержимое счетчика 5 поступает в блок 15, где вырабатывается признак "СтЗ=М", который поступает на вход коммутатора 43. УП = 010, этот признак передается на управляющий вход коммутатора 44. Если признак "СтЗ=М" равен нулю , (т.е. содержимое СтЗФМ), то коммутатор 44 передает на вход регистра 42адреса адрес 00011, что соответствует зацикливанию до окончания счетавсех коэффициентов увеличения элементов разложения матрицы символа покоординате Х (блок 11). Если признак"СтЗ=М"=1, то передается адрес 00110,что соответствует началу счета коэффициентов увеличения по координате У.После считывания из ПЗУ МК 41 очередной МК по адресу 00110 происходитобнуление регистра 14 (блок 12) посигналу с 18-го разряда ПЗУ МК 41,В следующем такте (блок 13) из ПЗУМК 41 считывается МК по адресу 00111,поле управляющих сигналов которой содержит управляющие сигналы для выполнения операции вычитания содержимогосдвигового регистра 2 из содержимогорегистра 14 и запись значения результата в регистр 14. Это достигаетсявыдачей управляющих сигналов на преобразователь 12 с целью коммутацииобратного кода содержимого сдвигового регистра 2 на вход сумматора 13и формирования переноса для получениядополнительного кода этого числа насумматоре 13, а также выдачей сигнала записи сдвигового регистра 2 с19-го разряда ПЗУ МК 41. В следующемтакте МК, считанная по адресу 01000,выдает управляющие сигналы для выполнения блока 14, а именно. управляющие сигналы для передачи константы М на вход сумматора 13, сигналзаписи результата суммирования содержимого регистра 14 и константы И врегистр 14 - 19-й разряд РЗУ МК 41,сигнал увеличения содержимого счетчика 6 на 1 - 15-й разряд ПЗУ МК 41,В этом же также осуществляется анализ знака результата суммированияЗн Е (блок 15), Если знак Зн 7 =1(знак результата суммирования отрицательный), то следующим адресом считывания МК .будет адрес 01000, т.е.осуществляется зацикливание выполнения блока 14 до выполнения условияЗн 2 =0 (знак результата суммированияположительный). Если Зн 2 =О, то осуществляется переход по адресу 01001,т.е. на выполнение блока 16. Условиеравенства нулю знака результата суммирования означает, что счет очередного (в данном случае первого) коэффициента увеличения элемента разложения матрицы по координате У закончен.Величина коэффициента при этом находится в четвертом счетчике 6, Следовательно, результатом выполнения блока 16 должно стать занесение содержимого счетчика 6 в блок по адресу,хранящемуся в счетчике 5 генератора,Зто достигается выдачей управляющегосигнала с 33-го разряда ПЗУ МК 41(логический "О") на второй коммута тор 10, который коммутирует на ад-.10, ресный вход блока 8 выход счетчика 5.На управляющий вход блока 8 с 34-го,и 35-го разрядов ПЗУ МК 41 выдаетсясигнал записи. Одновременно на преоб разователь 12 поступают управляющие15сигналы, которые коммутируют навход сумматора 13 обратный код содержимого сдвигового регистра 2 и Фор=мируют перенос для получения допол нительного кода этого числа на сумма 20торе 3, суммирования его с содержимым регистра 14. В результате суимн"рования на выходе сумматора 13 образуется разность содержимых регистра14 и сдвигового регистра 2, которая 25по сигналу с 19-го разряда ПЗУ МК 41записывается в регистр 14. В следующем такте по адресу 01010 из ПЗУМК 41 считывается МК, поле управляющих сигналов которой содержит управ- ЗОляющие сигналы обнуления счетчика 614-й разряд ПЗУ МК 41 увеличение содержимого счетчика 5 ка 1 - 31-й раз-,ряд ПЗУ МК 41 (блок 17). В этом жетакте признак сравнения содержимогосчетчика 5 и константы (М + И + 1)"Ст 32 =(М + Я + 1)", вырабатываемыйблоком 15, передается через коммутатор 43 (так как УП = 01 1) на управляющий вход коммутатора 44, управляяпередачей на вход регистра 42 адресалибо адреса 01000, если признак "Ст 3 =-.(М + М + 1 )" = О (т.е, содерлплмоесчетчика 5 не равно константе (М ++ Б + 1), что соответствует переходуна ачет следующего коэффициента увеличения элемента разложения матрицыпо координате 7 на блок 14) либо адреса 01011, если признак "Ст 3 = (М ++ Ы + .1)" = 1 что свидетельствует5 Ооб окончании счета коэффициентов увеличения элементов разложения матрицыпо координате У и завершения счетакоэффициентов в целом, В следующемтакте по адресу 01011 из ПЗУ МК 41считывается МК, нулевой разряд кото 55рой равен нулю. Этот разряд Формирует на информационном входе триггера52 логический "0"., Поскольку УП = 000,то на выход коммутатора 43 коммутируется логический "О", который подается на управляющий вход коммутатора 44, который, в свою очередь, подает на вход регистра 42 адреса содержимое поля адреса 57, Таким образом, на входе регистра 42 адреса формируется адрес перехода на следующую МК О 1100. По приходу переднего фронта счгнала СИ в триггер 52 записывается логический "0", который, поступая на вход схемы И 46, блокирует прохождение синхроимпульсов СИ на управляющий вход регистра 42 адреса, таким образом переводя генератор в состоякие ожидания. На этом расчет коэффициентов увеличения по Х и У заканчивается.При выходе из состояния ожидания генератор приккмает код генерируемого символа и последовательно формирует сигналы вывода точечкого изображения этого символа, хранимого в блоке 1, с учетом рассчитанных коэффициентов увеличения каждого элемента разложения матрицы по двум координатам Х и У, которые хранятся в блоке 8. Формирование сигналов последовательного вывода элементов матрицы производится в виде приращений координат на одну единицу растра по каждой из осей (по оси Х только в положительном направлении) нли по одной из них. Поэтому предлагается, что абсолютные координаты начального элемента матрицы символа (крайний левый нижний элемент) известны заранее., Нри наличии на входе 69 кода генерируемого символа по сигналу ЗпХ генератор (блок 19) выводится из состояния ожидания и осуществляется запись поступившего кода в регистр 11 по сигналу ЗпХ. Одновременно сигнал ЗпХ через элементы И 45 и ИЛИ 51 передается на информационный вход триггера 52, (так как инверсный выход триггера в данный момент равен "1") и записывается по переднему фронту сигнала СИ, устанавливая в единичное состояние выход 53, что способствует прохождению сигналов СИ на управляющий вход регистра 42 адреса. С инверсного выхода триггера 52 логический "О" поступает ка вход элемента И 45, тем самым блокируя прохождение сигнала ЗпХ на информационный вход триггера 52. Сформированный передний Фронт сигнала с выхода 54 элемента И 46 записывается в регистр 42 адреса адре с 01100, по которому осуще ствляется чтение очередной МК. У считанной МК и у последующих МК до конца генерации символа нулевой разряд равен "1", что способствует установке в каждом такте триггера 52 в единичное состояние, что, в свою очередь, является условием прохождения стробирующих сигналов СИ на управляющий ,вход регистра 42 адреса. В текущем10 такте по сигналам с 20-го и 21-го разрядов ПЗУ МК 41 осуществляется формирование константы М на входе второго счетчика 4, куда она и заносится по сигналу с 32-го разряда ПЗУ15 МК 41. По этому же сигналу осуществляется обнуление первого 3 и третьего 5 счетчиков (блок 20). Таким образом, после выполнения данных операций в счетчике 5 будет находиться20 ;начальный адрен. расположения в блоке 8 коэффициентов увеличения элементов матрицы символа по координате Х, а во втором счетчике 4 - начальный ад рес расположения в блоке 8 коэффициента увеличения элементов матрицы символа по координате 7. В следующем такте по адресу 01101 из ПЗУ МК 41 считывается МК, поле управляющих сиг налов которой содержит управляющие сигналы записи сдвигового регистра 2. содержимым блока 1 разложения матриц символов по адресу, старшие разряды которого образованы кодом символа, хранимого в регистре 11, а младшие - . содержимым счетчика 3, записи счетчика 7 содержимым блока 8 по адресу, хранящемуся в счетчике 5, а также сигнал внешнего выхода "-1 уц (22-й разряд ПЗУ МК 41). Необходимость40 предварительного шага "-1 у" вызвана требованием генерации символа с заданных координат начального элемента, а блоки 24 и 25 предполагают Форми рование сигналов приращения "+1 у" и признака генерации одновременно, что может привести к смещению сформированного символа на строку растра вверх. Для выполнения записи сигналы с 20-го и 21-го разрядов ПЗУ МК 41 подаются50 на управляющие входы преобразователя 12, который коммутирует выход регистра 11 на адресный вход блока 1. Одновременно логический "0" с 33-го разряда ПЗУ.МК 41, попадая на управляющий55 вход коммутатора 10, управляет комму" тацией на адресный вход блока 8 выхода счетчика 5, Разряды 34 и 35 формируют сигнал чтения содержимого блока 8. По сигналу с 36-го разряда ПЗУ МК 41содержимое считанной ячейки блока 8записывается в счетчик 7, Этот жесигнал разрешает выборку из блока 1 первого столбца стандартной матрицы разложения символа. Одновременно логическая "1" с 25-го разряда ПЗУ МК 41 поступает на управляющий вход коммутатора 9 и коммутирует на информационные входы сдвигового регистра 2 выход блока 1 разложения матриц символов, а на управляющие входы сдвигового регистра 2 поступают с 26-го и 2-го разрядов ПЗУ МК 41, которые настраивают сдвиговый регистр 2 на режим записи. Сигнал с 28-го разряда ПЗУ МК 41 через элемент ИЛИ 50 разрешает запись содержимого считанной ячейки блока 1 разложения матриц символов в сдвиговый регистр 2 (блок 21). В следующем такте (блок 22) по адресу 01110 из ПЗУ ИК 41 считывается МК, поле управляющих сигналов которой содержит управляющие сигналы для записи счетчика 6 содержимым ячейки блока 8, адрес которой находится в счетчике 4. Для этого логическая "1" с 33-го разряда ПЗУ ИК.41 поступает на управляющий вход коммутатора 10 и коммутирует на адресные входы блока 8 выходы счетчика 4, а на управляющие входы блока 8 поступают сигналы с 34-го и 35-го разрядов ПЗУ МК 41, которые формируют сигнал чтения блока 8. Одновременно по сигналу с 16-го разряда ПЗУ МК 41 осуществляется запись содержимого считанной ячейки блока 8 в счетчик 6, В следующем такте происходит совмещение выполнения блоков С 23 НЯ Для этого по адресу 01111 из ПЗУ МК 41 считывается МК, которая формирует сигналы вывода анализируемого элемента стандартной матрицы. В данном такте анализируется нулевой разряд сдвигового регистра 2 Й (СР, т.е, первый нижний элемент формируемого столбца матрицы символа. Считанная МК в поле управляющих сигналов имеет сигналы с 17-го и 23-го разрядов ПЗУ МК 41 (соответственно уменьшение содержимого счетчика 6 на 1 и +1 у), которые подаются на входы элемента И 47, на третий вход которого подается нулевой разряд сдвигового регистра 2. Таким образом, если Яо(СР) = 1, то на выходе элемента И 47 формируется логическая "1", которая через элемент ИЛИ 49 передается на выход устроиства, что является признаком генерации, т, е, признаком вывода или не вывода текущей координаты на экранг При СР(СР) = О такой признак не Формируется, следоВательно, осуещствляется только приащение координаты беэ ее визуализаи. В этом же такте по сигналу с 17-го разряда ПЗУ МК 41 происходит10 уменьшение содержимого счетчика б на ,1 и проверка признака равенства нулю содержимого этого счетчика Ст 4 = ОУ Формируемого блоком 15, так как поле15 М=100. Если признак Ст 4 = О равен ,"0", то коммутатор 44 передает на ход регистра 42 адреса адрес 01111, ,е. произойдет зацикливание блоков (23), С 2 (Д) до того, пока текущий соэффициент увеличения элемента матрицы по координате У не станет равным аулю, Если признак "Ст 4 = О" равен1 , то следующая МК будет считыватьея по адресу 10000 (блок 27 ) кото Рая в поле управляющих сигналов имеет сигнал с 29-го разряда ПЗУ МК 41,оторый увеличивает содержимое счетчика 4 на 1 (т.е. приращения адреса выборки очередного коэффициента увели-, чения элементов матрицы символа по координате У), и сигналы управления сдвиговым регистром 2, которые, поступая с 26-го и 27-го разрядов ПЗУ К 41, устанавливают режим сдвига право на один разряд, который осуцествляется по сигналу с выхода элемента ИЛИ 50, (так как 28-й разряд ЙЗУ МК 41 равен единице). В этом же "такте анализируется признак сравне" иия содержимого счетчика 4 с константой (М + И + 1) "Ст 2 = (М + и + 1)", сформированный блоком 15, так как поле УП = 101. Если "Ст 2 = (М + Я +1 РР + 1) = О, т.е. содержимое счетчика 4 ие равно константе (М + И + 1), то45 коммутатор 44 под воздействием этого сигнала на вход регистра 42 адреса передаст адрес перехода 01110, т.е. произойдет зацикливание формирования признака генерации, который зависит от значения нулевого разряда сдвигового регистра 2, до конца текущего столбца (блок (Я ). Если "Ст 2 = ,Р= (М + Я + 1)" = 1, то осуществляетсяр пе еход и считывание МК из ПЗУ МК 41 по адресу 10001 (блок 29). Считанная МК в ноле управляющих сигналов имеет рва сигнала уменьшения второго 4 и пятого 7 счетчиков на 1 (разряды соответственно 30 и 37 ПЗУ МК 41), а в поле УП код 110, который, поступая на управляющий вход коммутатора 43, управляет передачей признака равенства нулю счетчика 7 "Ст 5 = 0", Формируемого блоком 15, на управляющий вход коммутатора 44, который в случае, если "Ст 5 = 0" = О, коммутирует на вход регистра 42 адреса адрес 10010. Равенство нулю признака "Ст 5 = 0" означает, что содержимое счетчика 7, в котором хранится коэффициент увеличения элементов матрицы символа по координате Х, не равно нулю, следовательно, необходимо продолжать последовательное формирование сигналов вывода текущего столбца до выполнения указайжго равенства. С этой целью по адресу 10010 из ПЗУ МК 41 считывается МК, в поле управляющих сигналов которой находятся сигналы с 23-го и 24-го разрядов ПЗУ МК 41, которые выдают на выход устройства приращение по координатам Х и У, т,е. сигналы "+1 х" и "-.1 у" (блок С 31;Р ). Сигнал "+1 х" необходим для перехода на следующий столбец формируемого символа. Сигнал РР РР+1 у необходим для приращения координа тн по 1" в следствие однов р еменного формирования сигналов приращения - 1 у и признака генерации в последующем (блоки ЯЗ 4 , (35) , что может привести к смещению изображения Формируемого столбца по отношению к уже сформирова нв:ому. Поскольку поле УП прочитанной МК равно 000, то в следующем такте в регистр 42 адреса запишется адре с 1 00 1 1, по которому из ПЗУ МК 4 1 счит, ает ся МК, после управлякРщих сигнало в которой содержит сигналы записи счетчика 6 содержимым блока 8 по адресу, находящемуся в счетчике 4. При этом логическая "1" с 28-го разряда ПЗУ МК 41 управляет коммутацией коммутатора 10 и подключает выход счетчика 4 на адресный вход блока 8. Одновременно сигналы с 34-го и 35-го разрядов ПЗУ МК 41 формирует сигнал чтения для блока 8, а по сигналу с 16-го разряда ПЗУ МК 41 содержимое считанной ячейки записывается в счетчик 16. Поле УП выполняемой МК равно 000, поэтому адрес следующей МК определяется полем 57. В следующем такте происхццит совмещение выполнения блоков ЦЗ/ Ф Я 6 Р подобно описанному (блоки 23) - 2 ф ). По адресу 10100 изПЗУ МК 41 считывается МК, которая фор- (М) содержимого счетчика 4 (блокмирует сигналы вывола анализируемого Я 38 ) "Ст 2=(М)", вырабатываемыйэлемента стандартной матрицы. Отличие блоком 15, который происходит следузаключается в анализе последнего ющим образом. Поле УПпоступает(М)-го разряда сдвигового регистра на управляющий вход коммутатора 43,(1( Р, .е,последнего верхнего которыи в соответствии с поступившимнэлемента Формируемого столбца матри- кодом УП коммутирует признак "Ст 2=(М цы символа. Считанная МК в поле уп- на управляющий вход коммутатора 44,равляющих сигналов имеет сигналы с 10 который, в свою очередь, в зависимос 17-го и 22-го разрядов ПЗУ 41 (умень- ти от поступившего сигнала (О или 1)шение содержимого счетчика 6 на 1 ,коммутирует на вход регистра,42 адреи -1 у), которые подаются на входы са либо адрес с группы выходов 57Уэлементы И 48, на третий вход которой либо адрес с группы выходов 58. Еслиподается (11-1)-й разряд сдвигового 15 "Ст 2=(М) "=0 (т. е. содержимое второрегистра 2, Таким образом, если го счетчика 4 не равно константе (М)О (СР) -1и,1(СР) =1, то на выходе элемента что означает окончание развертки очеЭ 1И 48 формируется логическая "1", ко- Редного элемента столбца матрицы, ноторая через элемент ИЛИ 49 передает- не столбца в целом), то необходимося на выход устройства, что являетСя 20 пРодолжать генерацию текущего столбцапризнаком генерации, При О( ,(СР) =О, матрицы символа и адрес считываниякак и в предыдущем случае, такой при- очередной МК будет 10011. Еслизнак не формируется, следовательно, "Ст 2=(М)" (генерация столбца заверосуществляется только приращение ко- шена), то адрес перехода 10110ординаты, В этом же такте по сигналу 25 (блок С 39) ), МК, считанная по этомус 17-го разряда ПЗУ МК 41 происходит адресу, в поле управляющих сигналовуменьшение счетчика 6 на единицу ипроверка признака равенства нулю со- и декрементаа пятого счетчиков, что7держимого этого счетчика "Ст 4=0", фор- соответствует сигналам с 29-го и 37-гомируемого блоком 15, так как поле 30 разрядов ПЗУ МК 41, В этом же тактеУП=100. Если "Ст 4=0"=0 то произойдет производится анализ признака равензацикливание блоков (33Я 35 , чтоства нулю содержимого пятого счетчиприведет к развертке увеличиваемого ка 7 "Ст 5=0", формируемого блоком 15элемента столбца сверху вниз (в от- (блок С 40) ),личии от зацикливания блоков фЗ) ., (25), З 5где приращение по У положительно +1 у, Возможны два варианта. Если1следовательно, развертка снизу-вверх). Ст 5=0"=О то это значит, что текуЗацикливание обуславливается комму- щий коэффициент увеличения элементатацией на вход регистра 42 адреса при матрицы по координате Х, хранимыйСт 4=0=0 адреса возврата на текущий 40, в счетчике 7, не равен нулю и следу -блок - 10100. При "Ст 4=0"=1 (т.е. ет продолжать генерацию выбранногосодержимое счетчика 6 равно нулю) столбца матрицы, предварительно сдеследующая МК будет считываться с. ад- лав шаг по Х и у (+1 х, -1 у, блок Я ),реса 10101 (блок Я 37 ). СчитанныйВ этом случае выполняется. ЯК по адреМК в поле управляющих сигналов имеет .45 су 10111, котоРая выдает сигналы сигналы уменьшения содержимого счетчи , 22 го и 24 го разрядов ПЗУ МКка 4 на единицу и сдвига содержимого управление передается по адресу 01110сдвигового регистра 2 на один разряд (на блок Я 22 ), Если фСт 5:0":1влево. Выполнение действия Ст 2=Ст 2-1 (блок 40 ), то это свидетельствует опроисходит по сигналу с 30-го разряда 50 завершении генерации текущего столбцаПЗУ МК 41, С 26-го и 27-го разряда матрицы как по координате Х, так иПЗУ МК 41 на управляющий вход сдвиго- по У В этом случае по адресу 11000вого регистра 2 поступают сигналы, ко- считывается МК, которая выпает управторые устанавливают режим работы ляющий сигнал инкрементирования1рования сСдвиг влево, который осуществляет-го разряда ПЗУ МК 41 кото ый55ся по сигналу с выхода элемента ИЛИ Увеличивает на единицу содержимого50, так как 28-й разряд ПЗУ МК 41 ра- третьего 5 и первого 3 счетчиковвен 1. В этом же такте осуществляется (блок Я 4 ), что означает изменениеанализ признака равенства константе адреса для выборки из блока 8 следу

СмотретьЗаявка

4235066, 23.04.1987

ДОНЕЦКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

КОБА ЮРИЙ АНАТОЛЬЕВИЧ, АНОПРИЕНКО АЛЕКСАНДР ЯКОВЛЕВИЧ, БАШКОВ ЕВГЕНИЙ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G09G 1/08

Опубликовано: 15.03.1990

Код ссылки

<a href="https://patents.su/16-1550572-generator-simvolov.html" target="_blank" rel="follow" title="База патентов СССР">Генератор символов</a>

Предыдущий патент: Тренажер сварщика

Следующий патент: Устройство для отображения информации на экране электронно лучевой трубки

Случайный патент: Операционный усилитель