Логический процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

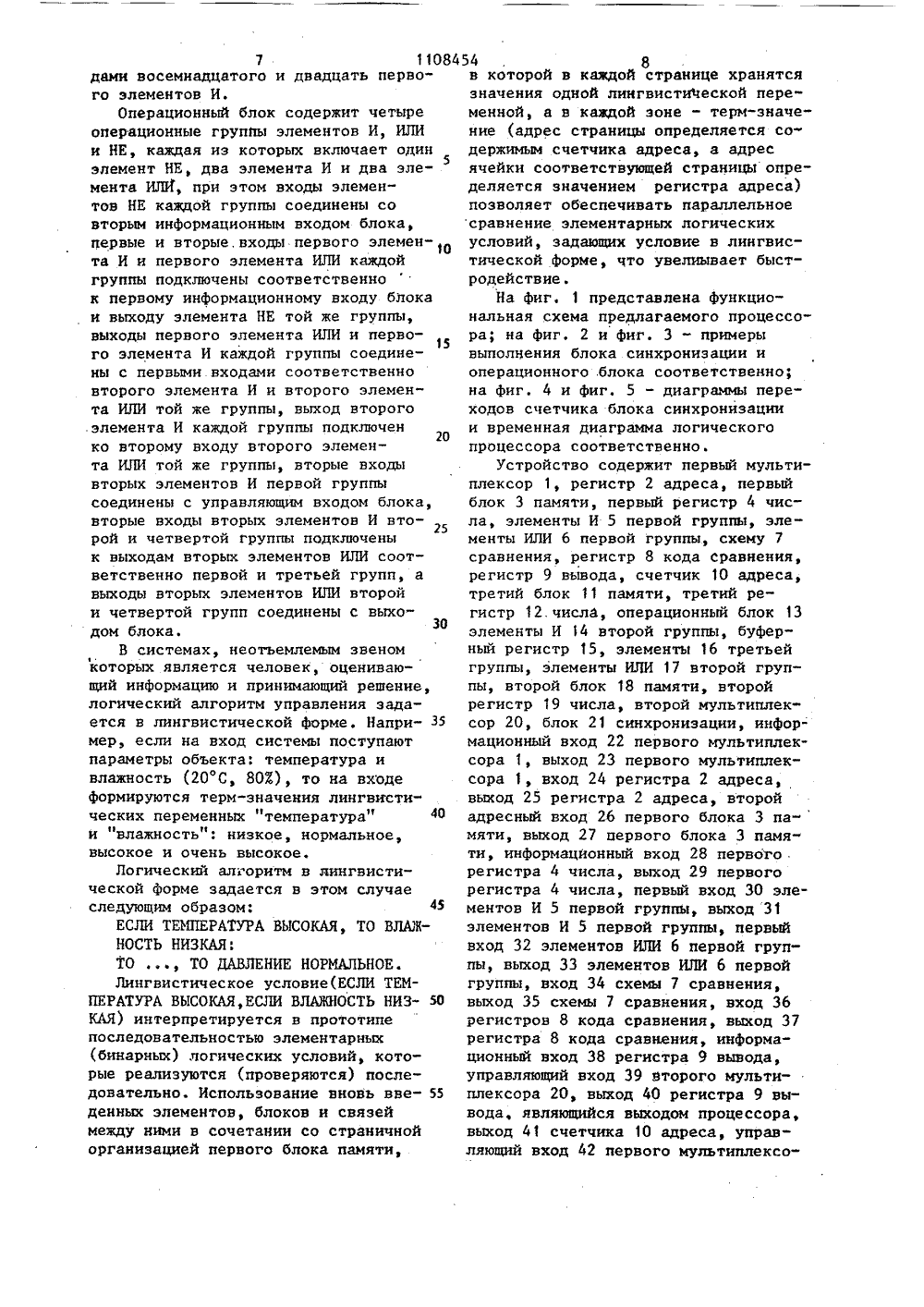

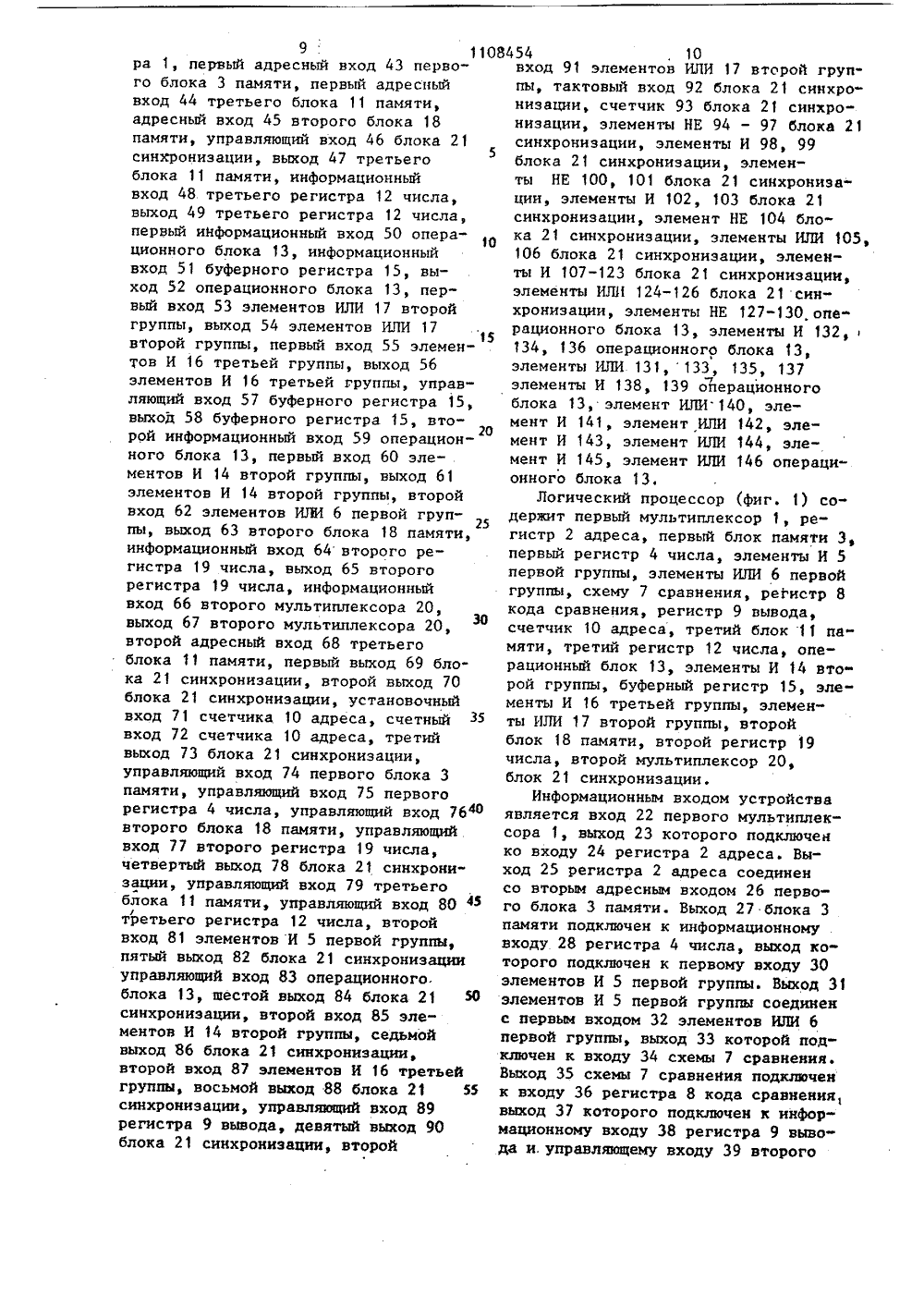

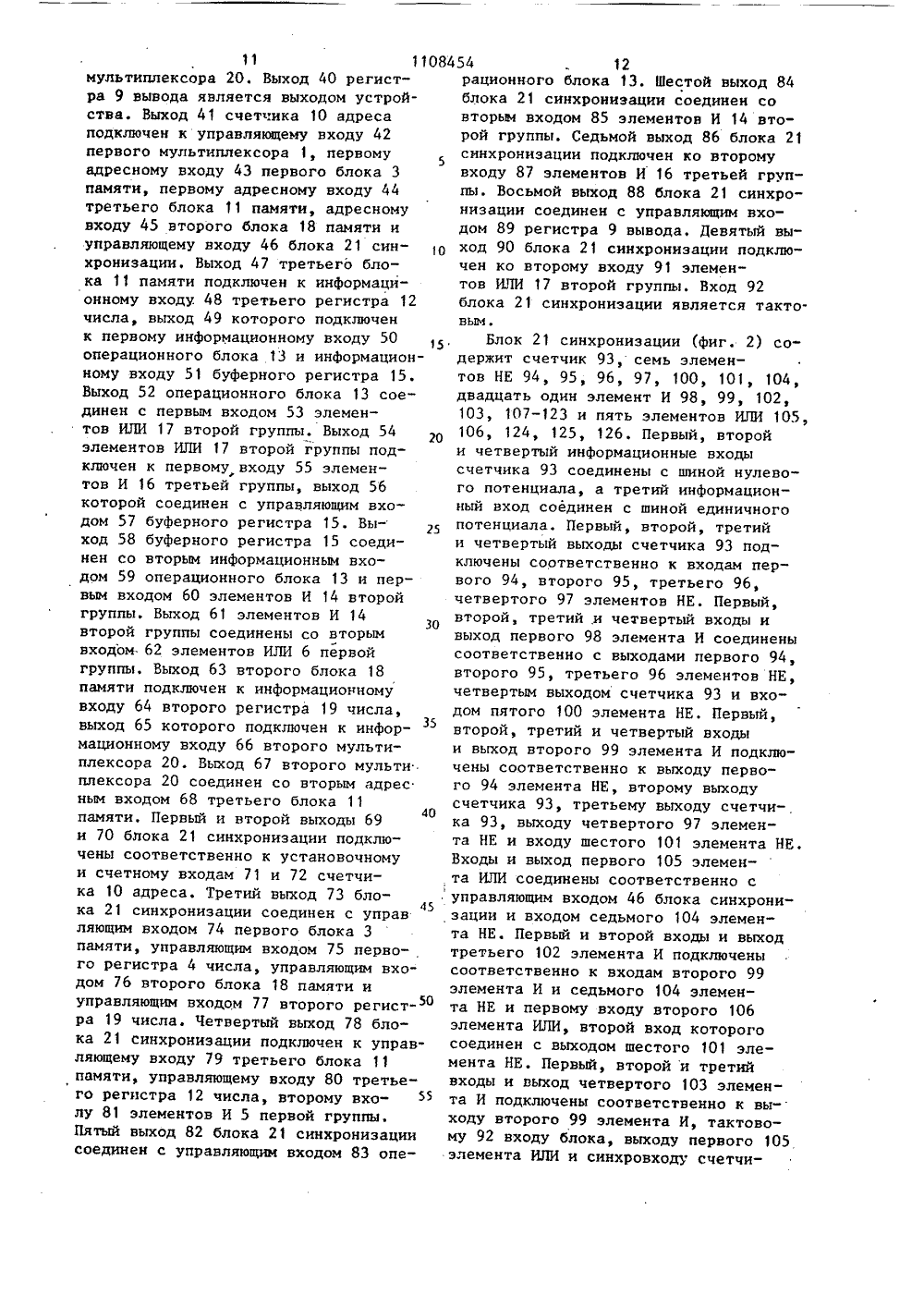

СОЮЗ СОВЕ СОЦИАЛ ИС РЕСПУБЛИ(19) 111) 3159 0 0 ете Е ИЗО Я У л с СУДАРСТВЕННЫЙ КОМИТЕТ СССРДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИИ ТОРСКОМУ СВИДЕТЕЛЬСТ(71) Ленинградский институт авиационного приборостроения,(56) 1. Авторское свидетельство СССРВ 2817309/18-24, кл. С 06 Р 15/20,2. Балашов Е.П, и др. Многофункциональные регулярные вычислительныеструктуры. М., "Советское радио",1978, с. 218 (прототип).(54)(57) 1, ЛОГИЧЕСКИЙ ПРОЦЕССОР,содержащий первый мультиплексор, ре"гистра адреса, счетчик адреса, дваблока памяти, два регистра числа,схему сравнения, операционный блоки блок синхронизации, управляющийвход, тактовый вход, первый и второйвыходы которого соединены соответственно с выходом счетчика адреса, тактовым входом процессора, установочным входом и счетным входом счетчикаадреса, третий выход блока синхронизации подключен к управляющим входампервого и второго блоков памяти ипервого и второго регистров числа,выход счетчика адреса соединен суправляющим входом первого мульти-.плексора и первыми адресными входамипервого и второго блоков памяти, выходы которых подключены к информационным .входам соответственно первогои второго регистров числа, информационный вход и выход первого мультиплексора соединены соответственнос информационным входом процессораи входом регистра адреса, выход которого подключен ко второму адресному входу первого блока памяти, о ти ч а ю щ и й с я тем, что, целью повышения быстродействия, он содержит второй мультиплексор, тре" тий блок памяти, третий регистр числа, буферный регистр, регистр кода сравнения, регистр вывода, три группы элементов И и две группы элементов ИЛИ, причем первые и вторые входы и выходы элементов И первой группы соединены соответственно с выходом первого регистра числа, четвертым выходом блока синхронизации и первыми входами элементов ИЛИ первой группы, вторые входы и выходы которых подключены соответственно к вьоодам элементов И второй группы и входу схемы сравнения, первый и второй адресные входы, управляющий вход и выход третьего блока памяти соедиЯ иены соответственно с выходом счетчика адреса, выходом второго мультиплексора, четвертым выходом блока синхронизации и информационным входом третьего регистра числа, управляющий вход и выход которого подключены соответственно к четвертому выходу блока синхронизации и первому информационному входу операционного блока, второй информационный вход, управ" ляющий вход и выход операционного блока соединены соответственно с выходом буферного регистра, пятым выходом блока синхронизации и первыми ,ЗЭК входами элементов ИЛИ второй группы, первые и вторые входы элементов И второй группы подключены соответственно к выходу буферного регистра и шестому выходу блока синхронизации, информационный и управляющий входы1108454 16Продолжение таблицы 0 1 плексора 1. ВыИнформ. Вход 22 Управл. Вход 42 ход23 11 Х 1 Х 2 ХЗ 45 Управл. Инфо Вход Вход Выхо йХ (хранен дыдущег таяния)15вой и третьей группы. Выходы вторых элементов ИЛИ 142, 146 второй н четвертой групп соединены с выходом 52 блока.Логический процессор работает сле 5 дующим образом.Третий 11 блок памяти имеет страничную организацию.Страничная органиэация третьего 11 блока памяти где в каждой странице 10 хранятся решения системы по одной лингвистической переменной, а в каж- дой зоне - множество этих решений, адрес страницы определяется значением счетчика 10 адреса, а адрес ячейки в соответствующей странице определяется значением второго 19 регистра числа, позволяет осуществить преобразование решения системы иэ лингвистической формы в числовую. Для страничной организации первого 3 и третьего 11 блоков памяти один набор адресных входов блоков памяти условно разбит на два: старшие разряды адреса (первый адресный вход) определяет номер страницы, а второй адресный вход (младшие разряды адреса) определяют ячейку в странице. Управляющий вход является входом "Чтение",Во втором 18 блоке памяти хранят 30 ся значения входных параметров из множества параметров, характеризующих состояние объекта, при которых функция принадлежности лингвистических переменных к терм-значениям максимальна.В первом такте по сигналу с выхода 69 блока 21 синхронизации счетчик 10 адреса устанавливается в Н.Таблица истинности счетчика 10адреса. Выходное значение 41 счетчика 10адреса поступает на вход 43 блока 3памяти, выбирая страницу, на вход 45блока 18 памяти, выбирая ячейку,на вход 46 блока 21 синхронизациии вход 42 первого мультиплексорапропуская значени . В-го параметрачерез первый мультиплексор 1.Таблица истинности первого мультиУ 1 У 2 УЗ У 4 У 5 Уб У 7 У 0 0 0 У 1 Х Х Х Х Х Х Х У 1 О 0 1 Х У 2 Х Х Х Х Х Х У 2 О 1 0 Х Х УЗ Х Х Х Х Х УЗ 0 1 1 Х Х Х У 4 Х Х Х Х У 4 1 0 0 Х Х Х Х У 5 Х Х Х У 5 1 0 1 Х Х Х Х Х Уб Х Х Уб 1 1 О Х Х Х Х Х Х У 7 Х У 7 1 1 1 Х Х Х Х Х Х Х У 8 У 8 Х - безразличное состояние С выхода 23 первого мультиплексора 1 значение Ю-го параметра поступа ет на вход 24 регистра 2 адреса.Таблица истинности регистра 2 адреса.17 11084Эта таблица истинности относится так же к регистрам 4, 19, 12 числа, регистру 8 кода сравнения, регистру 9 вывода и буферному регистру 15. Для регистра 2 адреса и регистра 8 кода сравнения управляющий вход жест 5 ко соединен с сигналом "Лог. 1".С выхода 25 регистра 2 адреса информации поступает на вход 26 блока памяти 3.В этом же также по сигналу с выхода 73 блока 21 синхронизации, поступающему на вход 74 блока 3 памяти, вход 76 блока 18 памяти, вход 75 регистра 4 числа и вход 77 регистра 1915 числа происходит чтение информации из блоков 3 и 18 памяти соответственно на регистры 4 и 19, входы 28, 64, На регистре 4 числа - функции принадлежности значения входного параметра для20 термов Ю-ой лингвистической переменной, а на регистре 19 числа - значе" .ния входной переменной для всех термов, при которых функция принадлежности максимальна.Во втором, такте по сигналу с выхода 78 блока 21 синхронизации, поступающему на вход 81 элементов И 5 первой группы, на вход 79 блока 11 памяти и вход 80 регистра 12 числа происходит следующее. Информация с выхода 31 элементов И 5 первой группы поступает на вход 32 элементов ИЛИ 6 первой группы, с выхода 33 элементов ИЛИ 6 первой группы на вход 34 схемы 7 сравнения. Схема 7 сравнения выявляет максимальное значение функции принадлежности для всех термов. Выход 35 схемы 7 сравнения имеет разрядность равную числу термов. Логическая единица появляется .4 О на том разрядном выходе, где функция принадлежности максимальна.Через вход 36 эта единица записывается в регистр 8 кода сравнения, Выход 37 регистра 8 кода сравнения 45 подключается ко входу 39 второго мультиплексора 20 и тем самым пропус-. кает адрес на вход 68 блока 11 памяти. С выхода 47 блока 11 памяти происходит считывание через вход 48 на 50 регистр 12 числа решений для известных значений лингвистической переменной и терма, к которому ее отнесли.В третьем такте но сигналам с выхода 90 и 86 блока 21 синхронизации, 55 поступающим соответственно на вход 91 элементов ИЛИ 17 второй группы и на вход 87 элементов И третьей группы 54 18и по образовавшемуся разрешающему сигналу на входе 57 буферного регистра 15, информация с выхода 49 регистра 12 числа записывается в буферный регистр 15 через вход 51.В четвертом такте по сигналу с выхода 70 блока 21 синхронизации на вход 72 счетчика 1 О поступает сигнал вычета единицы, т.е. осуществляется переход к следующему параметру системы и, соответственно, к следующей странице блоков 3 и 11 памяти, По сигналу с выхода 73 блока синхронизации происходит выборка функций при" надлежности из блока 3 памяти и зна-, чения параметра, при котором Функция принадлежности максимальна, из блока 18 памяти аналогично первому так" туПятый такт аналогичен второму, но производится на следующем входном параметре.В шестом такте происходит сравнение значений решений системы в лингвистической форме для входного пара" метра, хранящегося в буферном регистре 15 и считанного в регистр числа. По сигналу с выхода 82 блока 21 синхронизации, поступающего на вход 83 операционного блока 13 информация с выхода 49 регистра 12 числа и выхода 58 буферного регистра 15 поступает соответственно на входы 50, 59 опера- ционного блока 13. На выходе 52 операционного блока 13 имеются минимальные решения системы из сравниваемых. Минимальные решения поступают на входы элементов ИЛИ 17 второй группы, а с ее выхода 54 записываются в буферный регистр 15 аналогично третьему такту. Содержимое счетчика 10 адреса во время работы устройства поступает на вход 46 блока 21 синхронизации, в шестом такте производится анализ его на нуль. При неравенстве счетчи" ка 10 адреса нулю, управление передается четвертому такту, т.е. происходит ввод и анализ значения следующего параметра системы, Если счетчик 10 адреса равен нулю, т.е. анализ всех параметров системы произведен, то управление передается седьмому такту. В седьмом такте производится выбор решения для системы. По сигналу с выхода 84 блока 21 синхронизации, поступающему на вход 85 элементов И 14 второй группы с выхода 58 буферного регистра 15 минимальные решения системы в лингвистической1108454 Состоянисчетчика93 19форме поступают на вход 60 элементов И 14 второй группы, а с ее выхода 61 " на вход 62 элементов ИЛИ 6 первой группы, с выхода 33 элементов ИЛИ 6 первой группы - на вход 34 схемы сравнения 7; таким образом, в регистре кода сравнения 8 оказывается записанной логическая единица в том разряде, который соответствует максимальному значению решения систе мы из минимальных.В восьмом такте производится запись окончательного решения в регистр 9 вывода. По сигналу с выхо" да 88 блока 21 синхронизации решение системы с выхода 37 регистра кода сравнения поступает на регистр 9 выво да по входу 38.Таблица истинности блока 21 синхро. низации. 20 Выходы блока 21 синхронизации 9 70 73 78 82 84 86 88 90 25 0000 0 0 0 0 0 0 0 0 0 0001 1 0 1 0 0 0 0 0 030 0010 0 0 0 1 0 0 0 0 0 0011 0 0 0 0 0 О 1 0 1 0100 0 1 1 0 О О 0 0 О35 0101 0 0 0 1 0 0 0 0 0 0110 0 0 0 0 1 0 1 0 0 0111 0 0 0 0 0 О 1 0 040 1000 0 О 0 0 0 0 0 1 О 20Описанный логический процессор может использоваться в системах управления, для которых точная мате матическая модель функционирования объекта управления не известна, например в системах прогнозирования с учетом большого числа параметров, в системах управления технологическими процессами, в процессе биосинтеза антибиотиков, экспресс-диагностика и т.д.Реализация возможности принятия решения в условиях неопределенности позволяет облегчить труд человека- оператора данного класса систем, повысить их быстродействие, надежность и качество принимаемых решений,Время, необходимое для обработкипредлагаемых логическим процессором М параметров, равноТр=(5 + 3 М) ,где М - число параметров, характеризующих состояние объекта;Т - период тактовых импульсов.Время, необходимое для обработки М параметров прототипом, равноТр =2(ш)+53 МС,где М - число параметров, .характеризующих состояние объекта;ш - число элементов множества,представляющего терм"значение;С - период тактовых импульсов.вЕсли число входных параметров.характеризующих объект М=10, ш=20,й=2 мкс, тоТдр 860 мксТд др =70 мкс еТаким образом, предлагаемый логический процессор дает значительныйвыигрыш в быстродействии по сравнению с прототипом.Составитель В.БялыйРедактор С.Тимохина Техред О.Неце Корректор М. шаро аказ ал ППП "Патент", г,Ужгород, ул.Проектная, 4 7 Я 7 Ф 66/35 Тираж 699ВНИИПИ Государственного комипо делам изобретений и 3035, Москва, Ж, Раушская н Подписноеета СССРоткрытийб., д, 4/511буферного регистра соединены соответственно с выходом третьего регистрачисла и выходами элементов И третьейгруппы, первые и вторые входы которых подключены соответственно к выходам элементов ИЛИ второй группы иседьмому выходу блока синхронизации,восьмой и девятый выходы которогосоединены соответственно с управляющим входом регистра вывода и вторыми входами элементов ИЛИ второйгруппы, информационный и управляющийвходы второго мультиплекстора подключены соответственно к выходу второгорегистра числа и выходу регистра кода сравнения, вход которого соединенс выходом схемы сравнения, а информационный вход и выход регистра выводаподключены соответственно к выходурегистра кода сравнения и выходупроцессора,2. Процессор по и, 1, о т л и -ч а ю щ и й с я тем, что блок синхронизации содержит счетчик, семьэлементов НЕ двадцать один элемент Ии пять элементов ИЛИ, при этом первый, второй и четвертый информационные входы счетчика соединены с шинойнулевого потенциала, а третий информационный вход счетчика - с шинойединичного потенциала, первый, второй, третий и четвертый выходы счетчика подключены ко входам соответственно первого, второго, третьего ичетвертого элементов НЕ, первый, вто-,рой, третий и четвертый входы и выходпервого элемента И соединены соответственно с выходами первого, второгои третьего элементов НЕ, четвертымвыходом счетчика и входом пятого элемента НЕ, первый, второй, третийи четвертый входы и выход второгоэлемента И подключены соответственнок выходу первого элемента НЕ второму выходу счетчика, третьему выходусчетчика, выходу четвертого элемента НЕ и входу шестого элемента НЕ,входы и выход первого элемента ИЛИсоединены соответственно с управляющим входом блока и входом седьмогоэлемента НЕ, первый и второй входыи выход третьего элемента И подключены соответственно к выходам второго элемента И, седьмого элемента НЕи первому входу второго элемента ИЛИ,второй вход которого соединен с выхо-.дом шестого элемента НЕ, первый,второй и третий входы и выход четвертого элемента И подключены соответ 08454ственно к выходу второго элемента И, тактовому входу блока, выходу первого элемента ИЛИ и синхровходу счетчика, первый и второй входы и выход пятого элемента И соединены соответственно с тактовым входом блока, выходом пер" вого элемента И и входом сброса счет чика, первый, второй и третий входыи выход шестого элемента И подключе"ны соответственно к тактовому входублока, выходу пятого элемента НЕ, выходу второго элемента ИЛИ и счетному входу счетчика, первый и второй входы седьмого элемента И соединеныс выходами третьего и четвертого элементов НЕ, первый и второй входывосьмого элемента И подключены к выходу четвертого элемента НЕ и третьему выходу счетчика, первый и второйвходы девятого элемента И соединены с четвертым выходом счетчика и выходом третьего элемента НЕ, первый ивторой входы десятого элемента И подключены к первому и второму выходам счетчика, первый и второй входы одиннадцатого элемента И соединены с выходом второго элемента НЕ и первым выходом счетчика, первый и второй входы двенадцатого элемента И подключены к выходам первого и второго элементов НЕ, первый и второй входы тринадцатого элемента И соединены с выходом первого элемента НЕ и вторым выходом счетчика, первый и второй входы четырнадцатого элемента И подключены к выходам седьмого и тринадцатого элементов И, первый и второй входы пятнадцатого элемента И соединены с выходами седьмого и одиннадцатого элементов И, первый и второй входы шестнадцатого элемента И подключены к выходам восьмого и двенадцатого элементов И, первый и второй входы семнадцатого элемента И соединены с выходами восьмого и одиннадцатого элементов И, первый и второй входы восемнадцатого элемента И подключены к выходам седьмого и десятого элементов И, первый и второй входы девятнадцатого элемента И соединены с выходами седьмого и восьмого элементов И, первый и второй входы двадцатого элемента И подключены к выходам девятого и двенадцатого элементов И, первый и второй входы двадцать первого элемента И соединены с выходами восьмого и тринадцатого элементов И, выход шестнадцатого элемента И подключен к перво108454 му выходу блока и первому входу третьего элемента ИЛИ, второй вход ивыход которого соединены соответственно с выходом пятнадцатого элемента И и третьим выходом блока, выходпятнадцатого элемента И подключенко второму выходу блока, первый ивторой входы и выход четвертого элемента ИЛИ соединены соответственнос выходами четырнадцатого и семнадцатого элементов И и четвертым выходом блока, выходы двадцать первогоэлемента И, девятнадцатого элемента И, пятого элемента ИЛИ, двадцатогэлемента И и восемнадцатого элемента И подключены соответственно к пятому, шестому, седьмому, восьмомуи девятому выходам блока, а первыйи второй входы пятого элемента ИЛИсоединены с выходами восемнадцатогои двадцать первого элементов И. 3. Процессор по п. 1, о т л и - ч а ю щ и й с я теш, что операционный блок содержит четыре операционные группы элементов И, ИЛИ и НЕ,1Изобретение относится к вычислительной технике и может быть использовано для классификации ситуации в многопараметрических системах, например для функциональной диагностики в автоматических системах многопрофильной оценки здоровья, в системах управления уличным движением, в системах управления теплицами.Известно устройство, содержащее 1 О блок памяти, регистр сдвига, регистр адреса, регистр числа, два триггера режима, счетчик, устройство управления, входные шины аргумента и выходные шины результата, причем выход 15 регистра адреса соединен с первымвходом блока памяти, первый, второй и третий выходы которого соответственно подключены к информационному входу регистра числа, к первому вхо ду первого триггера режима и к первому входу второго регистра режима, первый разрядный выход регистра числа является выходом результата, а второй, третий разрядные .выходы 25 каждая иэ которых включает один элемент НЕ, два элемента И и два элемента ИЛИ, при этом входы элементов НЕкаждой группы соединены со вторыминформационным входом блока, первыеи вторые входы первого элемента Ии первого элемента ИЛИ каждой группыподключены соответственно к первомуинформационному входу блока и выходуэлемента НЕ той же группы, выходыпервого элемента ИЛИ и первого элемента И каждой группы соединеныс первыми входами соответственно вто"рого элемента И и второго элемен"та ИЛИ той же группы, выход второгоэлемента И каждой группы подключенко второму входу второго элемента ИЛИ той же группы, вторые входыэлементов И первой группы соединеныс управляющим входом блока, вторыевходы вторых элементов И второй ичетвертой групп подключены к выходамвторых элементов ИЛИ соответственнопервой и третьей групп, а выходывторых элементов ИЛИ второй и четвертой групп соединены с выходом блока,2регистра числа подключены соответственно к информационному входу регистра адреса и к первому входу счетчика, входом управляющего процессораявляется вход регистра сдвига, выход которого подключен ко второмувходу блока памяти 1 .Данное устройство предназначенодля преобразования множества параметров, характеризующих состояние объекта, в двоичный код,Недостатком данного устройстваявляется низкое быстродействие, обус.ловленное тем, что выбор решенияпроизводится путем последовательного сравнения текущего значения параметра с эталонными значениями.Наиболее близким по техническойсущности и достигаемому результатук предлагаемому является устройстводля реализации разветвленных алгоритмов.Логический процессор содержит первый мультиплексор, регистр адреса,счетчик адреса, два блока памяти, 110845440 два регистра числа, схему сравнения,операционный блок и блок синхронизации, управляющий вход, тактовый вход,первый и второй выходы которого соединены соответственно с выходом 5счетчика -адреса, тактовым входомпроцессора, установочным входом исчетным входом счетчика адреса, третий выход блока синхронизации подключен к управляющим входам первогои второго блоков памяти и первогои второго регистров числа, выходсчетчика адреса соединен с управляющим входом первого мультиплексораи первыми адресными входами первогои второго блоков памяти, выходы которых подключены к информационным входам соответственно первого и второгорегистров числа, информационный входи выход первого мультиплексора соедииены соответственно с информационнымвходом процессора и входом регистраадреса, выход которого подключенко второму адресному входу первогоблока памяти2 .25Недостатком данного устройстваявляется низкое быстродействие, таккак производится последовательноесравнение текущего значения параметра с хранимыми в блоке памяти эталонными значениями.Целью изобретения является повышение быстродействия за счет параллельного сравнения текущего значенияпараметра с эталонными. 35указанная цель достигается тем,что в логический процессор, содержащий первый мультиплексор, регистрадреса, счетчик адреса, два блокапамяти, два регистра числа, схемусравнения, операционный блок и блоксинхронизации, управляющий вход,тактовый вход, первый и второй выходы которого соединены соответственнос выходом счетчика адреса, тактовым 45входом процессора, установочным вхо, дом и счетным входом счетчика адреса,третий выход блока синхронизации подключен к управляющим входам первогои второго блоков памяти и первого 50и второго регистров числа, выходсчетчика адреса соединен с управляющим входом первого мультиплексораи первыми адресными входами первогои второго блоков памяти, выходы которых подключены к информационным входам соответственно первого и второгорегистров числа, информационный входи выход первого мультиплексора соединены соответственно с информационным входом процессора и входом регистра адреса, выход которого подключен ко второму адресному входу первого блока памяти, введены второй мультиплексор, третий блок памяти, третий регистр числа, буферный регистр,регистр кода сравнения, регистр вывода, три группы элементов И и двегруппы элементов ИЛИ, причем первыеи вторые входы и выходы элементов Ипервой группы соединены соответственно с выходом первого регистра числа,четвертым выходом блока синхронизациии первыми входами элементов ИЛИ первой группы, вторые входы и выходыкоторых подключены соответственнок выходам элементов И второй группыи входу схемы сравнения, первый ивторой адресные входы, управляющийвход и выход третьего блока памятисоединены соответственно с выходомсчетчика адреса, выходом второго мультиплекстора, четвертым выходом блокасинхронизации и информационным входом третьего регистра числа, управляющий вход и выход которого подключены соответственно к четвертому выходу блока синхронизации и первомуинформационному входу операционногоблока, второй информационный вход,управляющий вход и выход операционного блока соединены соответственнос выходом буферного регистра, пятымвыходом блока синхронизации и первыми входами элементов ИЛИ второй группы, первые и вторые входы элементов Ивторой группы подключены соответственно к выходу буферного регистраи шестому выходу блока синхронизации,информационный и управляющий входы бу"ферного регистра соединены соответственно с выходом третьего регистрачисла и выходами элементов И третьейгруппы, первые и вторые входы которыхподключены соответственно к выходамэлементов ИЛИ второй группы и седьмому выходу блока синхронизации, восьмой и девятый выходы которого соединены соответственно с управляющимвходом регистра вывода и вторымивходами элементов ИЛИ второй группы,информационный и управляющий входывторого мультиплексора подключенысоответственно к выходу второго регистра числа и выходу регистра кодасравнения, вход которого соединенс выходом схемы сравнения, а информационный вход и выход регистра выводадевятого элемента И соединен:1 с четвертым выходом счетчика и выходомтретьего элемента НЕ, первый и второйвходы десятого элемента И подключенык первому и второму выходам счетчика,первый и второй входы одиннадцатогоэлемента И соединены с выходом второго элемента НЕ и первым выходомсчетчика, первый и второй входы двенадцатого элемента И подключены к вы" ходам первого и второго элементов НЕ,первый и второй входы тринадцатогоэлемента И соединены с выходом первого элемента НЕ и вторым выходом счетчика, первый и второй входы четырнадцатого элемента И подключены к выходам седьмого и тринадцатого элементов И, первый и второй входы пятнадцатого элемента И соединены с выходами седьмого и одиннадцатого элементов И, первый и второй входы шестнадцатого элемента И подключены к выходам восьмого и двенадцатого элемента И, первый и второй входы семнадцатого элемента И соединены с выходамивосьмого и одиннадцатого элементов И,первый и второй входы восемнадцатого элемента И подключены к выходамседьмого и десятого элементов И, первый и второй входы девятнадцатогоэлемента И соединены с выходами седь-мого и восьмого элементов И, первыйи второй входы двадцатого элемента Иподключены к выходам девятого и две"надцатого элементов И, первый и второй входы двадцать первого элемента Исоединены с выходами восьмого и тринадцатого элементов И, выход шестнадцатого элемента И подключен к первому выходу блока и первому входу третьего элемента ИЛИ, второй вход и выход которого соединены соответственнос выходом пятнадцатого элемента Ии третьим входом блока, выход пятнадцатого элемента И подключен ко вто"рому выходу блока, первый и второйвходы и выход четвертого элемента ИЛИсоединены соответственно с выходами четырнадцатого и семнадцатого элементов И и четвертым выходом блока, выходы двадцать первого элемента И,девятнадцатого элемента И, пятогоэлемента ИЛИ, двадцатого элемента Ии восемнадцатого элемента И подключены соответственно к пятому, шестому,седьмому, восьмому и девятому выходам блока, а первый и второй входыпятого элемента ИЛИ соединены с выхо 3 1108454 подключены соответственно к выходу регистра кода сравнения и выходу процессора.Блок синхронизации содержит счетчик, семь элементов НЕ, двадцать один элемент И и пять элементов ИЛИ, при этом первый, второй и четвертый информационйые входы счетчика соединены с шиной нулевого потенциала, а третий информационный вход счетчика - с ши О ной единичного потенциала, первый, второй, третий и четвертый выходы счетчика подключены ко входам соответственно первого, второго, третьего и четвертого элементов НЕ, первый, 15 второй, третий и четвертый входы и выход первого элемента И соединены соответственно с выходами первого, второго и третьего элементов НЕ, четвертым выходом счетчика и входом р 0 пятого элемента НЕ, первый, второй, третий и четвертый входы и выход второго элемента И подключены соответственно к выходу первого элемента НЕ, второму выходу счетчика, третьему вы ходу счетчика, выходу четвертого элемента НЕ и входу шестого элемента НЕ, входы и выход первого элемента ИЛИ соединены соответственно с управляющим входом блока и входом30 седьмого элемента НЕ, первый и второй входы и выход третьего элемента И подключены соответственно к выходам второго элемента И, седьмого элемента НЕ и первому входу второго элемента ИЛИ, второй вход которого соединен с выходом шестого элемента НЕ, первый, второй и третий входы и выход четвертого элемента И подключены соответственно к выходу второго элемента И, тактовому входу блока,40 выходу первого элемента ИЛИ и синхровходу счетчика, первый и второй входы и выход пятого элемента И соединены соответственно с тактовым входом блока, выходом первого элемен 45 та И и входом сброса счетчика, первый, второй и третий входы и выход ,шестого элемента И подключены соответственно к тактовому входу блока, выходу пятого элемента НЕ, выходу второго элемента ИЛИ и счетному входу счетчика, первый и второй входы седьмого элемента И соединены с выходами третьего и четвертого элементов НЕ, первый и второй входы восьмо го элемента И подключены к выходу четвертого элемента НЕ и третьему выходу счетчика, первый и второй входы7 1108дами восемнадцатого и двадцать перво"го элементов И.Операционный блок содержит четыреоперационные группы элементов И, ИЛИи НЕ, каждая из которых включает один5элемент НЕ, два элемента И и два элемента ИЛИ, при этом входы элементов НЕ каждой группы соединены совторым информационным входом блока,первые и вторые. входы первого элемента И и первого элемента ИЛИ каждойгруппы подключены соответственнок первому информационному входу блокаи выходу элемента НЕ той же группы,выходы первого элемента ИЛИ и первого элемента И каждой группы соединены с первыми входами соответственновторого элемента И и второго элемента ИЛИ той же группы, выход второгоэлемента И каждой группы подключен20ко второму входу второго элемента ИЛИ той же группы, вторые входывторых элементов И первой группысоединены с управляющим входом блока,вторые входы вторых элементов И второй и четвертой группы подключенык выходам вторых элементов ИЛИ соответственно первой и третьей групп, авыходы вторых элементов ИЛИ второйи четвертой групп соединены с выхо 30дом блока.В системах, неотъемлемым звеномкоторых является человек, оценивающий информацию и принимающий решение,логический алгоритм управления задается в лингвистической форме, Напри- З 5мер, если на вход системы поступаютпараметры объекта: температура ивлажность (20 С, 803), то на входеформируются терм-значения лингвксти"ческих переменных "температура" 40и "влажность": низкое, нормальное,высокое и очень высокое,Логический алгоритм в дингвистическои форме задается в этом случаеследующим образом: 45ЕСЛИ ТЕМПЕРАТУРА ВЫСОКАЯ, ТО ВЛАЖНОСТЬ НИЗКАЯТО е, ТО ДАВЛЕНИЕ НОРМАЛЬНОЕ.Лингвистическое условие(ЕСЛИ ТЕМПЕРАТУРА ВЫСОКАЯ, ЕСЛИ ВЛАЖНОСТЬ НИЗКАЯ) интерпретируется в прототипепоследовательностью элементарных(бинарных) логических условий, которые реализуются (проверяются) последовательно. Использование вновь введенных элементов, блоков и связеймежду ними в сочетании со страничнойорганизацией первого блока памяти,454 8 в которой в каждой странице хранятся значения одной лингвистической леременной, а в каждой зоне - терм-значение (адрес страницы определяется содержимым счетчика адреса, а адрес ячейки соответствующей страницы определяется значением регистра адреса) позволяет обеспечивать параллельное сравнение элементарных логических условий, задающих условие в лингвистической форме, что увелиывает быстродействие.На фиг. 1 представлена функциональная схема предлагаемого процессора; на фиг. 2 и фиг. 3 - примерывыполнения блока синхронизации иоперационного .блока соответственно;на фиг. 4 и фиг. 5 - диаграммы переходов счетчика блока синхронизациии временная диаграмма логическогопроцессора соответственно. Устройство содержит первый мультиплексор 1, регистр 2 адреса, первыйблок 3 памяти, первый регистр 4 числа, элементы И 5 первой группы, элементы ИЛИ 6 первой группы, схему 7сравнения, регистр 8 кода сравнения,регистр 9 вывода, счетчик 10 адреса,третий блок 11 памяти, третий регистр 12. числа, операционный блок 13элементы И 14 второй группы, буферный регистр 15, элементы 16 третьейгруппы, элементы ИЛИ 17 второй группы, второй блок 18 памяти, второйрегистр 19 числа, второй мультиплексор 20, блок 21 синхронизации, инфор-мационный вход 22 первого мультиплексора 1, выход 23 первого мультиплексора 1, вход 24 регистра 2 адреса,выход 25 регистра 2 адреса, второйадресный вход 26 первого блока 3 па-мяти, выход 27 первого блока 3 памяти, информацйонный вход 28 первогорегистра 4 числа, выход 29 первогорегистра 4 числа, первый вход 30 элементов И 5 первой группы, выход 31элементов И 5 первой группы, первыйвход 32 элементов ИЛИ б первой группы, выход 33 элементов ИЛИ б первойгруппы, вход 34 схемы 7 сравнения,выход 35 схемы 7 сравнения, вход 36регистров 8 кода сравнения, выход 37регистра 8 кода сравнения, информационный вход 38 регистра 9 вывода,управляющий вход 39 второго мультиплексора 20, выход 40 регистра 9 вывода, являющийся выходом процессора,выход 41 счетчика 1 О адреса, управляющий вход 42 первого мультиплексовход 91 элементов ИЛИ 7 второй груп"пы, тактовый вход 92 блока 2 1 синхро"низации, счетчик 93 блока 21 синхро"низации, элементы НЕ 94 - 97 блока 2 15синхронизации, элементы И 98, 99блока 21 синхронизации, элементы НЕ 100, 101 блока 21 синхронизации, элементы И 102, 103 блока 21синхронизации, элемент НЕ 104 блока 21 синхронизации, элементы ИЛИ 105,106 блока 21 синхронизации, элементы И 107-123 блока 21 синхронизации,элементы ИЛ 1 124-126 блока 21 синхронизации, элементы НЕ 127-130, операционного блока 13, элементы И 132,134, 136 операционного блока 13,элементы ИНИ 13 1,133, 135, 137элементы И 138, 139 операционногоблока 13, элемент ИЛИ 140, элемент И 41, элемент ИЛИ 142, элемент И 143, элемент ИЛИ 144, элемент И 145, элемент ИЛИ 146 операци"онного блока 13.Логический процессор (фиг. 1) содержит первый мультиплексор 1, ре"гистр 2 адреса, первый блок памяти Э,первый регистр 4 числа, элементы И 5первой группы, элементы ИЛИ 6 первойгруппы, схему 7 сравнения, регистр 8кода сравнения, регистр 9 вывода,счетчик 10 адреса, третий блок 11 па"мяти, третий регистр 12 числа, операционный блок 13, элементы И 14 второй группы, буферный регистр 15, элементы И 16 третьей группы, элементы ИЛИ 17 второй группы, второйблок 18 памяти, второй регистр 19числа, второй мультиплексор 20,блок 21 синхронизации,Информационным входом устройстваявляется вход 22 первого мультиплексора 1, выход 23 которого подключенко входу 24 регистра 2 адреса. Выход 25 регистра 2 адреса соединенсо вторым адресным входом 26 первого блока 3 памяти. Выход 27 блока 3памяти подключен к информационномувходу 28 регистра 4 числа, выход которого подключен к первому входу 30элементов И 5 первой группы. Выход 31элементов И 5 первой группы соединенс первым входом 32 элементов ИЛИ 6первой группы, выход 33 которой подключен к входу 34 схемы 7 сравнения.Выход 35 схемы 7 сравнения подключенк входу 36 регистра 8 кода сравнения,выход 37 которого подключен к информационному входу 38 регистра 9 вывода и. управляющему входу 39 второго 9: 110 ра 1, первый адресный вход 43 первого блока 3 памяти, первый адресный вход 44 третьего блока 11 памяти, адресный вход 45 второго блока 18 памяти, управляющий вход 46 блока 2 1 синхронизации, выход 47 третьего блока 11 памяти, информационный вход 48 третьего регистра 12 числа, выход 49 третьего регистра 12 числа, первый ийформационный вход 50 опера 1 ционного блока 13, информационный вход 5 1 буферного регистра 15, выход 52 операционного блока 13, первый вход 53 элементов ИЛИ 17 второй группы, выход 54 элементов ИЛИ 17 второй группы, первый вход 55 элемен 1 тов И 16 третьей группы, выход 56 элементов И 16 третьей группы, управляющий вход 57 буферного регистра 15, выход 58 буферного регистра 15, второй информационный вход 59 операционного блока 13, первый вход 60 элементов И 4 второй группы, выход 61 элементов И 14 второй группы, второй вход 62 элементов ИЛИ 6 первой группы, выход 63 второго блока 18 памяти,25 информационный вход 64 второго регистра 19 числа, выход 65 второго регистра 19 числа, информационный вход 66 второго мультиплексора 20, выход 67 второго мультиплексора 20, второй адресный вход 68 третьего блока 11 памяти, первый выход 69 блока 21 синхронизации, второй выход 70 блока 21 синхронизации, установочный вход 71 счетчика 10 адреса, счетный З 5 вход 72 счетчика 10 адреса, третий выход 73 блока 21 синхронизации, управляющий вход 74 первого блока 3 памяти, управляющий вход 75 первого регистра 4 числа, управляющий вход 764 О второго блока 18 памяти, управляющий вход 77 второго регистра 19 числа, четвертый выход 78 блока 21 синхронизации, управляющий вход 79 третьего блока 11 памяти, управляющий вход 80 45 lтретьего регистра 12 числа, второй вход 81 элементов И 5 первой группы, пятый выход 82 блока 21 синхронизации управляющий вход 83 операционного. блока 13, шестой выход 84 блока 21 50 синхронизации, второй вход 85 элементов И 14 второй группы, седьмой выход 86 блока 21 синхронизации, второй вход 87 элементов И 16 третьей группы, восьмой выход 88 блока 21 55 синхронизации, управляющий вход 89 регистра 9 вывода, девятый выход 90 блока 21 синхронизации, второй 8454 1011 1108 мультиплексора 20. Выход 40 регистра 9 вывода является выходом устройства. Выход 41 счетчика 10 адреса подключен к управляющему входу 42 первого мультиплексора 1, первому адресному входу 43 первого блока 3 памяти, первому адресному входу 44 третьего блока 11 памяти, адресному входу 45 второго блока 18 памяти и управляющему входу 46 блока 21 синхронизации. Выход 47 третьего блока 11 памяти подключен к информационному входу 48 третьего регистра 12 числа, выход 49 которого подключен к первому информационному входу 50 операционного блока 13 и информационному входу 51 буферного регистра 15. Выход 52 операционного блока 13 соединен с первым входом 53 элементов ИЛИ 17 второй группы. Выход 54 элементов ИЛИ 17 второй группы подключен к первому входу 55 элементов И 16 третьей группы, выход 56 которой соединен с управляющим входом 57 буферного регистра 15. Выход 58 буферного регистра 15 соединен со вторым информационным входом 59 операционного блока 13 и первым входом 60 элементов И 14 второй группы. Выход 61 элементов И 1430 второй группы соединены со вторым входом. 62 элементов ИЛИ 6 первой группы, Выход 63 второго блока 18 памяти подключен к информационному входу 64 второго регистра 19 числа, выход 65 которого подключен к информационному входу 66 второго мультиплексора 20, Выход 67 второго мульти плексора 20 соединен со вторым адрес ным входом 68 третьего блока 1 памяти, Первый и второй выходы 69 и 70 блока 21 синхронизации подключены соответственно к установочному и счетному входам 71 и 72 счетчика 10 адреса. Третий выход 73 блока 2 синхронизации соединен с управ45 ляющим входом 74 первого блока 3 памяти, управляющим входом 75 первого регистра 4 числа, управляющим входом 76 второго блока 18 памяти и управляющим входом 77 второго регистра 19 числа. Четвертый выход 78 блока 21 синхронизации подключен к управляющему входу 79 третьего блока 11 памяти, управляющему входу 80 третьего регистра 12 числа, второму вхолу 81 элементов И 5 первой группы. Пятый выход 82 блока 2 1 синхронизации соединен с управляющим входом 83 опе 454 12 рационного блока 13. Шестой выход 84 блока 21 синхронизации соединен со вторым входом 85 элементов И 14 второй группы. Седьмой выход 86 блока 21 синхронизации подключен ко второму входу 87 элементов И 16 третьей группы. Восьмой выход 88 блока 21 синхронизации соединен с управляющим входом 89 регистра 9 вывода. Девятый выход 90 блока 2 1 синхронизации подключен ко второму входу 91 элементов ИЛИ 17 второй группы. Вход 92 блока 2 1 синхронизации является такто. вым.Блок 21 синхронизации (фиг. 2) содержит счетчик 93, семь элементов НЕ 94, 95, 96, 97, 100, 101, 104, двадцать один элемент И 98, 99, 102, 03, 107-123 и пять элементов ИЛИ 105, 106, 124, 125, 126. Первый, второй и четвертый информационные входы счетчика 93 соединены с шиной нулевого потенциала, а третий информационный вход соединен с шиной единичного потенциала. Первый, второй, третий и четвертый выходы счетчика 93 подключены соответственно к входам первого 94, второго 95, третьего 96, четвертого 97 элементов НЕ. Первый, второй, третий .и четвертый входы и выход первого 98 элемента И соединены соответственно с выходами первого 94, второго 95, третьего 96 элементов НЕ, четвертым выходом счетчика 93 и входом пятого 100 элемента НЕ. Первый, второй, третий и четвертый входы и выход второго 99 элемента И подключены соответственно к выходу первого 94 элемента НЕ, второму выходу счетчика 93, третьему выходу счетчика 93, выходу четвертого 97 элемента НЕ и входу шестого 101 элемента НЕ. Входы и выход первого 105 элемента ИЛИ соединены соответственно с управляющим входом 46 блока синхронизации и входом седьмого 104 элемента НЕ. Первый и второй входы и выход третьего 102 элемента И подключены соответственно к входам второго 99 элемента И и седьмого 04 элемента НЕ и первому входу второго 106 элемента ИЛИ, второй вход которого соединен с выходом шестого 101 элемента НЕ. Первый, второй и третий входы и выход четвертого 103 элемента И подключены соответственно к выходу второго 99 элемента И, тактовому 92 входу блока, выходу первого 105 элемента ИЛИ и синхровходу счетчи8454 14 мого 110 и тринадцатого 115 элементов И. Выход шестнадцатого 118 элемента И подключен к первому 69 выходублока и первому входу третьего 124 5элемента ИЛИ, второй вход и выходкоторого соединены соответственно свыходом пятнадцатого 117 элемента Ии третьим 73 выходом блока. Выходпятнадцатого 117 элемента И подключенко второму 70 выходу блока. Первыйи второй входы и выход четвертого 125элемента ИЛИ соединены соответственно с выходами четырнадцатого 116и семнадцатого 119 элементов И и четвертым 78 выходом блока, Выходы двад-,цать первого 123 элемента И, девятнадцатого 121 элемента И, пятого 126элемента ИЛИ, двадцатого 122 элемента И и восемнадцатого 120 элемента И Оподключены соответственно к пятому 82, шестому 84, седьмому 86, восьмому 88 и девятому 90 выходам блока.Первый и второй входы пятого 126 элемента ИЛИ соединены с выходами восем"надцатого 120 и двадцать первого 123элементов И.Операционный блок 13 (фиг, 3) содержит четыре операционных группыэлементов И, ИЛИ и НЕ, каждая иэ которых включает один элемент НЕ 127130, два элемента И 132, 134, 136,138, 139, 141, 143, 145 и два элемента ИЛИ 131, 133, 135, 137, 140, 142,144, 146. При этом входы элемен"тов НЕ 127 в . 130 соединены со вторыминформационным 59 входом блока, Первые и вторые входы первых элементов И 132, 134, 136, 138 и первыхэлементов ИЛИ 13 1, 133, 135, 137 подключены соответственно к первому информационному 50 входу блока и выходам элементов НЕ 127-130 своей группы. Выходы первых элементов ИЛИ 13 1,133, 135, 137 и первых элементов И 132, 134, 136, 138 соединеныс первыми входами соответственно вторых элементов И 139, 141, 143, 145и вторых элементов ИЛИ 140, 142, 144146 своей группы, Выход вторых элементов И 139, 141, 143, 145 подклю"чен ко вторым входам вторых элементов ИЛИ 140, 142, 144, 146 своейгруппы. Вторые входы вторых элементов И первой и третьей групп 139, 143соединены с управляющим входом блока. 13 110 ка 93. Первый и второй входы и вы" ход пятого 107 элемента И соединены соответственно с тактовым 92 входом блока, выходом первого 98 элемента И и входом сброса счетчика 93, Первый, второй и третий входы и выход шестого 108 элемента И подключены соответственно к тактовому 92 входу блока, выходу пятого 100 элемента НЕ, выходу второго 106 элемен 1 та ИЛИ и счетному входу счетчика 93. Первый и второй входы седьмого 109 элемента И соединены с выходами третьего 96 и четвертого 97 элементов НЕ. Первый и второй входы восьмого 1101 элемента И подключены к выходу четвертого 97 элемента НЕ и третьему выходу счетчика 93. Первый и второй входы девятого 111 элемента И соединены с четвертым выходом счетчика 93 и выходом третьего 96 элемента НЕ.2 Первый и второй входы десятого 112 элемента И подключены к первому и второму выходам счетчика 93. Первый и второй входы одиннадцатого 11325 элемента И соединены с выходом второго 95 элемента НЕ и первым выходом счетчика 93. Первый и второй входы двенадцатого 114 элемента И подключены к выходам первого 94 и второго 95 элементов НЕ. Первый и второй входы тринадцатого 115 элемента И соединены с выходом первого 94 элемента НЕ и вторым выходом счетчика 93. Первый и второй входы четырнадцатого 116 элемента И подключены к выходам седьмого 109 и тринадцатого 115 элементов И. Первый и второй входы пятнадцатого 117 элемента И подключены к выходам седьмого 109 и одиннадцатого 113 элементов И. Первый и второй 40 входы шестнадцатого 118 элемента И подключены к выходам восьмого 110 и двенадцатого 114 элементов И. Первый и второй входы семнадцатого 119 элемента И соединены с выходами восьмого 110 и одиннадцатого 113 элемен" тов И. Первый и второй входы восемнадцатого 120 элемента И подключены к выходам седьмого 109 и десятого 112 элементов И. Первый и второй входы 50 девятнадцатого 121 элемента И соеди" иены с выходами седьмого 109 и восьмого 110 элементов И. Первый и второй входы двадцатого 122 элемента И подключены к выходам девятого 111 и две надцатого 114 элементов И. Первый и второй входы двадцать первого 123 элемента И соединены с выходами воаьВторые входы вторых элементов И второй и четвертой группы 141, 145 подключеиы к выходам вторых элементов ИЛИ 140, 144 соответственно пер

СмотретьЗаявка

3474903, 19.06.1982

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

БАЛАШОВ ЕВГЕНИЙ ПАВЛОВИЧ, БАРСЕГЯН АРМЕНАК АРТАВАЗДОВИЧ, БЯЛЫЙ ВИКТОР ОСКАРОВИЧ, КУПРИЯНОВ МИХАИЛ СТЕПАНОВИЧ

МПК / Метки

МПК: G06F 17/00

Метки: логический, процессор

Опубликовано: 15.08.1984

Код ссылки

<a href="https://patents.su/16-1108454-logicheskijj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Логический процессор</a>

Предыдущий патент: Устройство для функционально-динамического контроля логических схем

Следующий патент: Вероятностный автомат

Случайный патент: Учебное устройство для определения степени деформации материалов