Микропрограммный модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

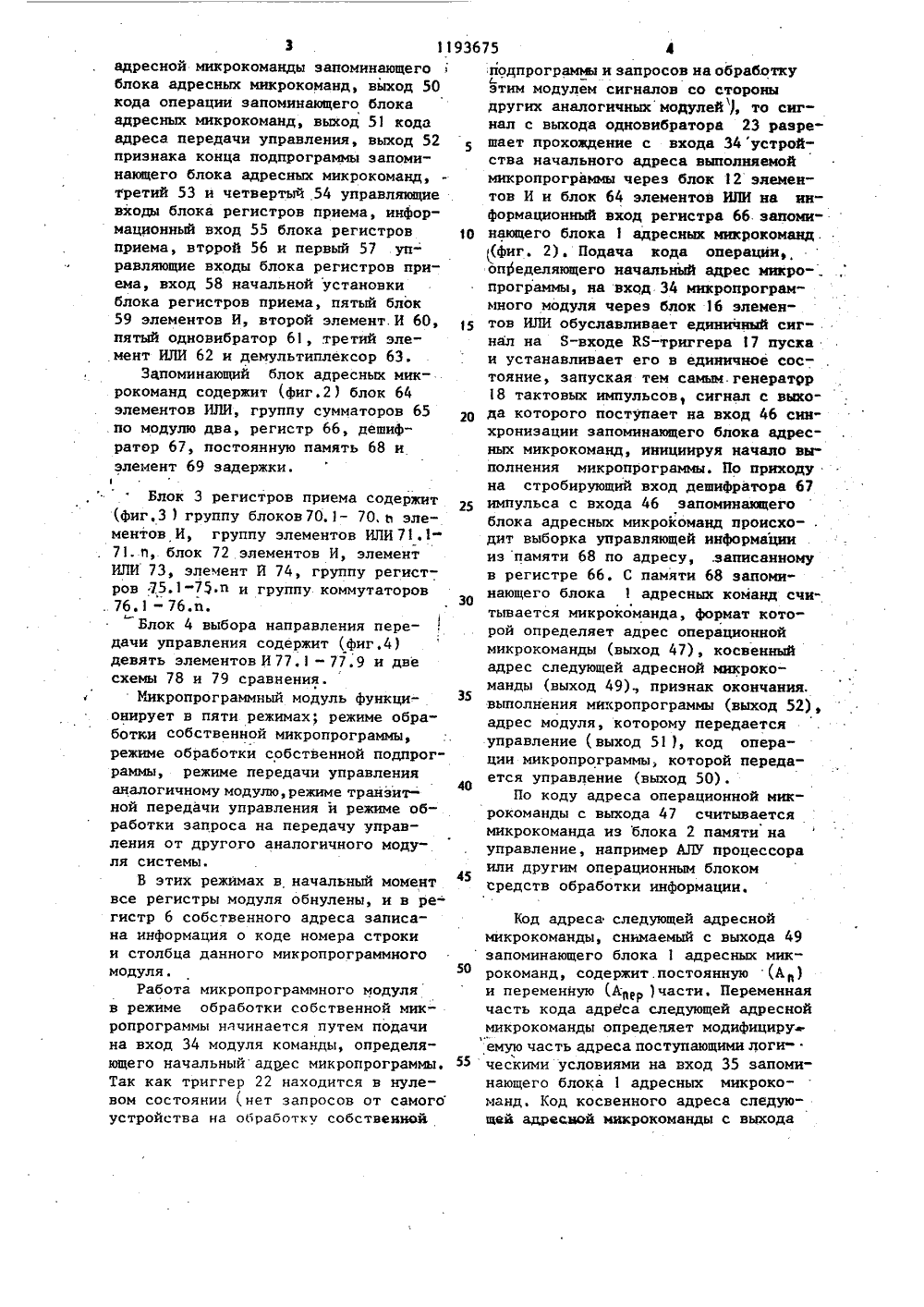

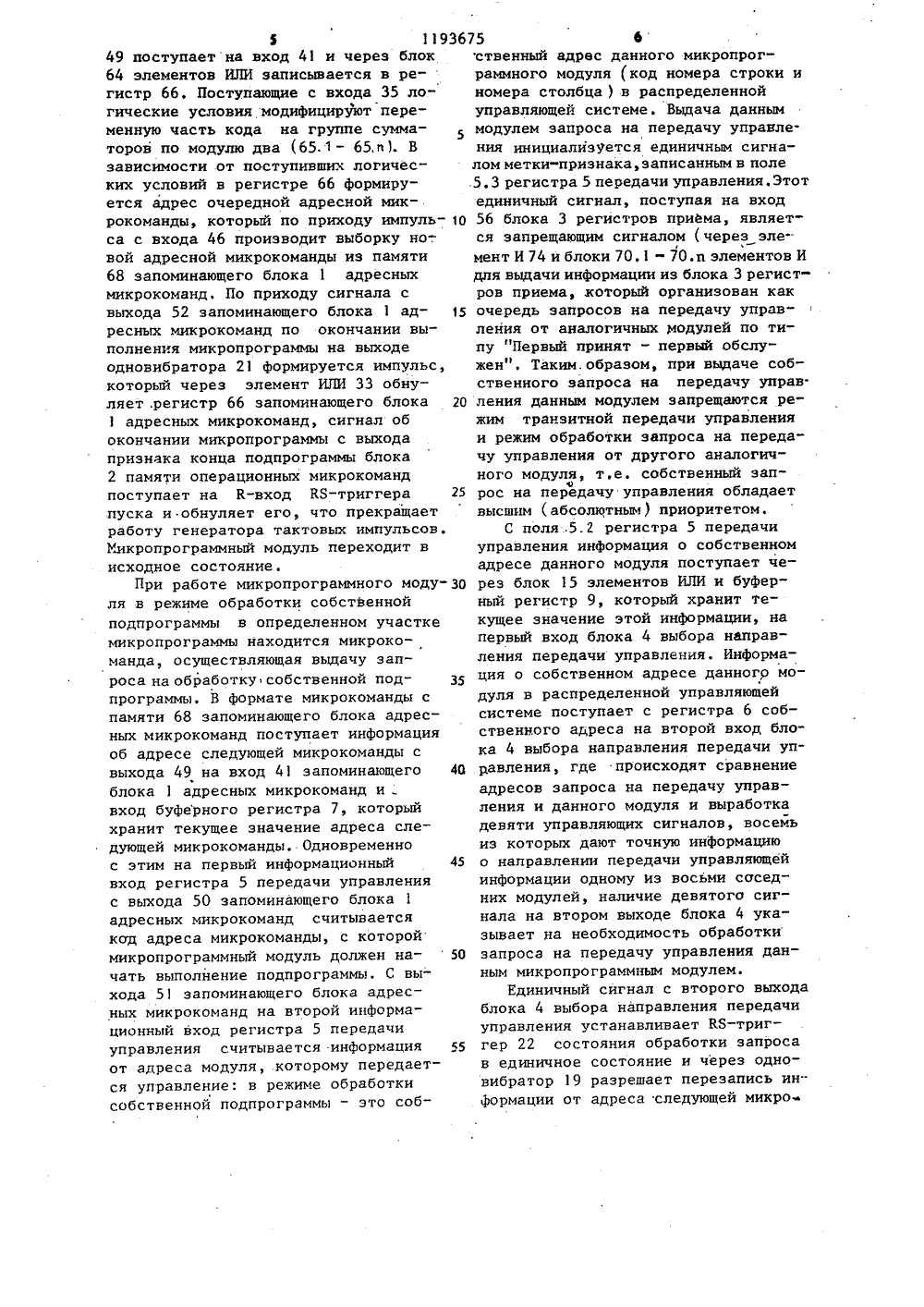

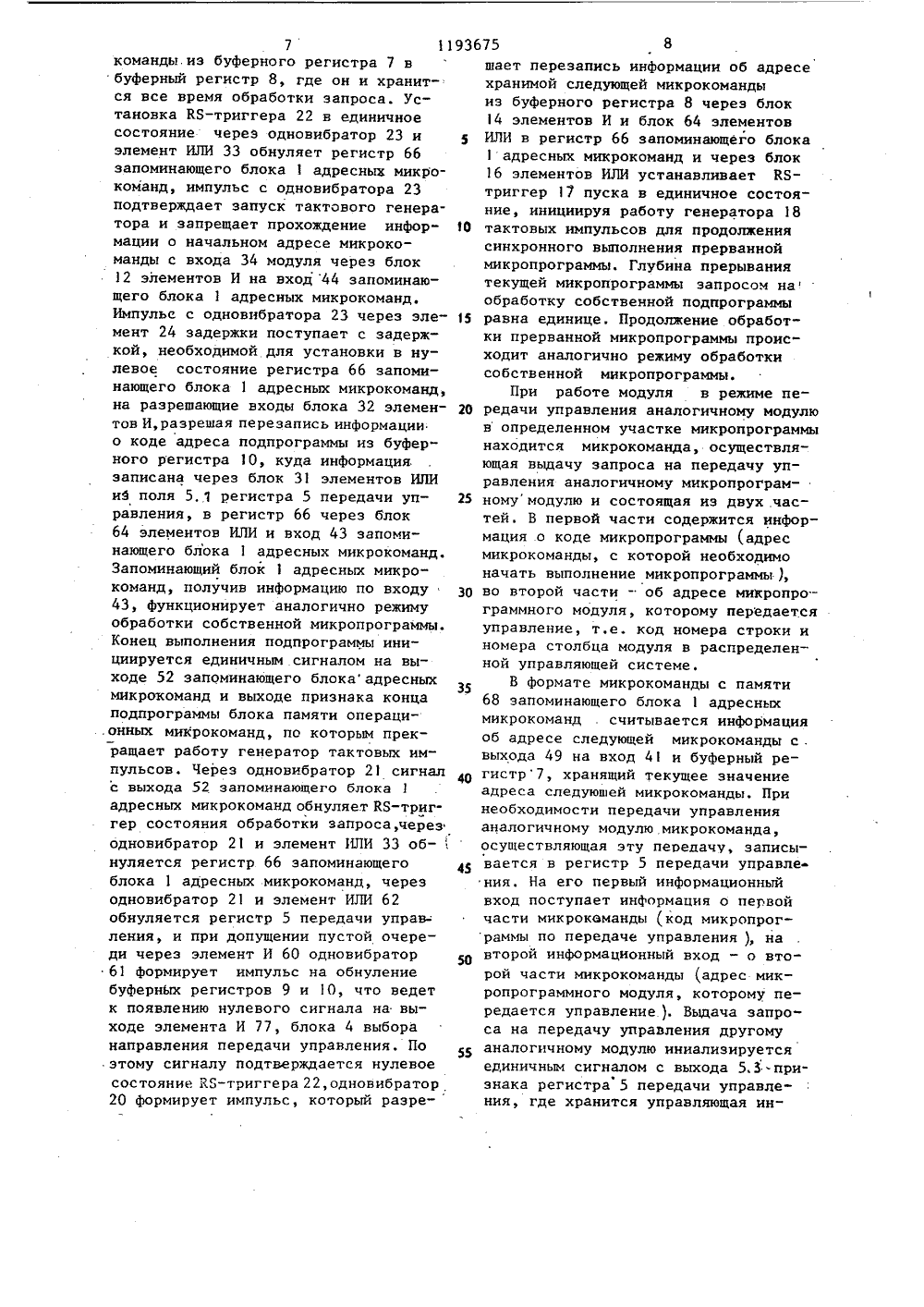

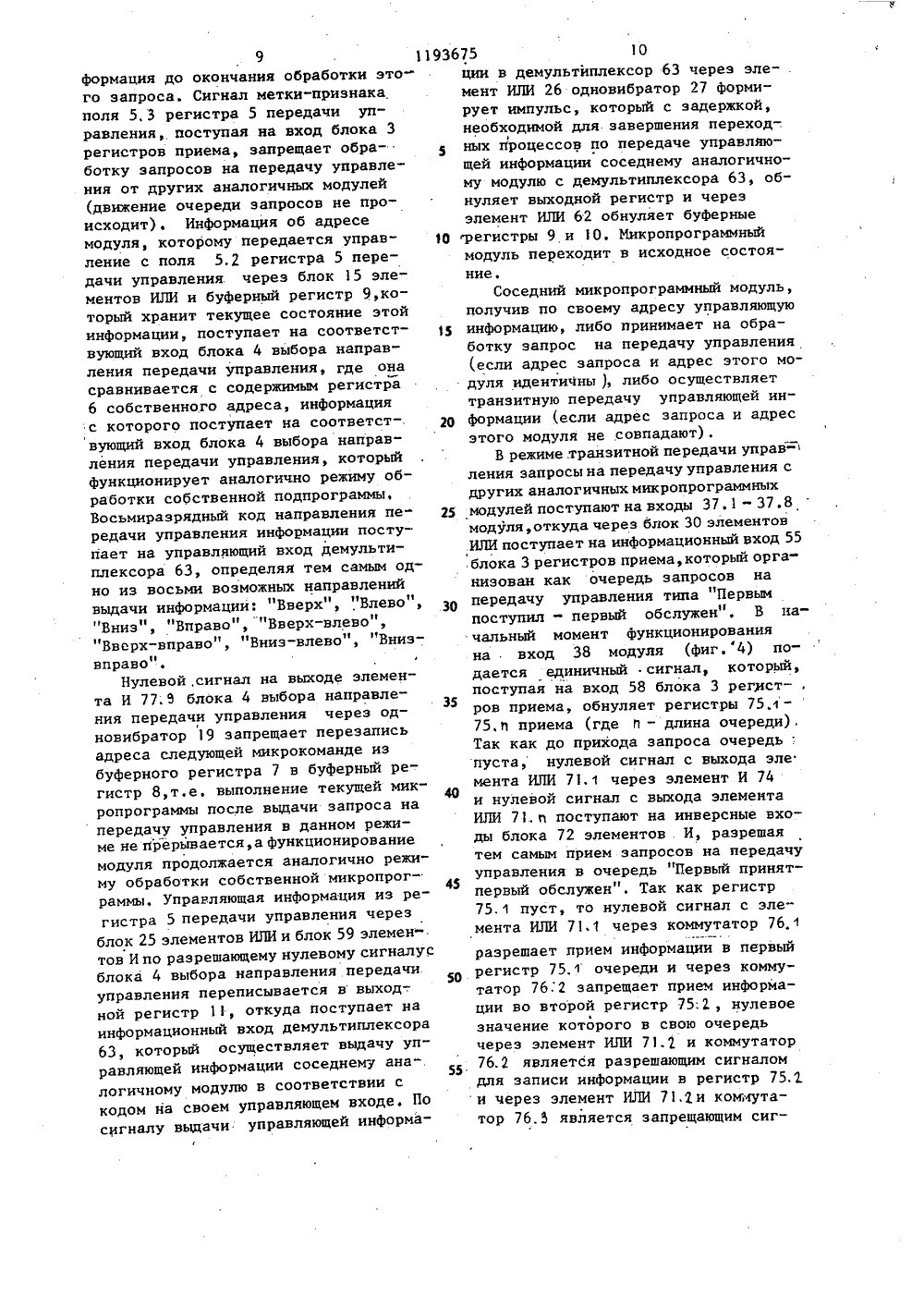

(46) 23.11.85, Бю 4 микрокоманд, выход к ции которого являетс ляющим выходом модул микроопе первым управгруппа вхоментов ИЛИ явзапросов на одуля, выход истра соединен го блока элеменсоединен с м запоминаюдов первого блока эл ляется группой входо ередачу управленияервого буферного ре с первым вх тов И, выхо первым адре щего блока выход кода динен с пер дом перв которог ным входмикрокоманд, оторого соеационным вхо адресных пераций ым ин о ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(72) В.А. Мельников, В.Н. СамошиГ.Н. Тимонькин и В.С. Харченко 3) 681.325(088.8)6) Авторское свидетельство СССР 959080, кл. С 06 Р 9/22, 1980 Авторское свидетельство ССС11 596947, кл. С 06 Г 9/22, 197(54)(57) 1. МИКРОПРОГРАММНЫЙ МОДУЛЬсодержащий запоминающий .блок адресных микрокоманд, блок памяти опрацинных микрокоманд, регистр передачи управления, первый, второй итретий блоки элементов И, первыйблок элементов ИЛИ, первый и второйбуферные регистры, триггер пуска игенератор тактовых импульсов, причемвыход кода адреса операционной микрокоманды запоминающего блока адресных микрокоманд соединен с адресныывходом блока памяти операционных дом регистра передачи управления, второй информационный вход которого соединен с выходом кода адреса передачи управления запомина)ощего блока адресных микрокоманд, выход кода косвенного адреса следующей адресной микрокоманды которого соединен с информационным входом второго буферного регистра, выход которого соединен с первым входом второго блока элементов И,выход признака обращения к блоку памяти операционных микрокоманд запоминающего блока адресных микрокоманд соединен с входом управления записью блока памяти операционных микрокоманд, единичный ф выход триггера пуска соединен с входом запуска генератора тактовых импульсов, выход которого соединен С с входом синхронизации запоминающего блока адресных микрокоманд, выход признака конца подпрограммы блока Май памяти операционных микрокоманд сое- ы, динен с входом установки в "О триггера пуска, о т л и ч а ю щ и й с я (д тем, что, с целью расширения области р применения модуля путем организации транзитной передачи управляющей информации, он дополнительно содержит блок регистров приема, регистр собственного адреса, гретий и четвертый буферные регистры, второй , третий и четвертый блоки элементов ИЛИ, четвертый и пятый блоки элементов, И, триггер состояния обработки запроса, выходной регистр, пять элементов ИЛИ, шесть одновибраторов, два элемента И, элемент задержки, демультиплексор и блок выбора направления передачи управления, содержащий две13 1 передачу управления (единичный сигнал признака поля 5.3 регистра 5 передачи управления очередь, блока 3регистров приема находится в состо-. .янии ожидания до тех пор, пока этот запрос не будет обслужен (регистр передачи управления обнулен).Режим транзитной передачи данно-го запроса на передачу управления в модулях распределенной управляющей системы проходит до тех пор, пока адрес этого запроса не совпадет с собственным адресом модуля, обрабатывающего этот запрос в текущий момент времени.В режиме обработки запроса на передачу управления от другого аналогичного модуля после приема запросов на передачу управления и формирование очереди в блоке 3 регистров приема. работа микропрограммного модуля до выработки сигналов направления передачи управления блоком 4 протекает аналогично режиму транзитной передачи управления. Если управление передано именно этому мо" дулю, то единичный сигнал с выхода элемента И 77. В блока 4 выбора нап- равления передачи управления запрещает запись управляющей информации через блок 59 элементов И в выходной регистр 11, устанавливает КБ- триггер 22 состояния обработки запроса в единичное состояние и через одновибратор 19 разрешает перезащ ь адреса следующей микрокоманды из буферного регистра 7 в буферный регистр 8 через блок 13 элементов И, где эта информация хранится пока не будут обслужены все запросы на передачу управления, адресованные этому модулю. По переходу РЭ-триггера 22 в единичное состояние одновибратор 23 вырабатывает импульс, который через блок 16 элементов ИЛИ подтверждает функционирование генератора 18 тактовых импульсов, запрещает подачу с входа 34 начального адреса микрокоманцы, через элемент ИЛИ 33 обнуляет регистр 66 запоминающего блока 1 адресных микрокоманд, через элемент 24 задержки, которая необходима для обнуления регистра 66, разрешает прохождение начального адреса микрокоманды запроса ыа передачу управления с буферного регистра 10, который хранит ее текущее состояние, через блок193675 1410 15 20 25 30 35 40 45 50 55 32 элементов И на вход 43 запоминающего блока 1 адресных микрокоманд,По завершении выполнения микропрограммы запроса на передачу управления на выходе 52 запоминающего блока 1 адресных микрокомандвырабатывается единичный сигнал, который поступает на одновибратор 21. С соответствующего выхода блока 2 памяти операционных микрокоманд единичный сигнал окончания подпрограммы обнуляет ЙВ-триггер 17 пуска, и работа генератора 18 тактовых импульсов прекращается. Импульс с выхода одновибратора 21,поступая на вход 57 блока 3 регистров приема, разрешает продвижение очереди через элемент ИЛИ 33, обнуляет регистр 66 запоминающего блока 1 адресных микрокоманд, подготавливая его к обслуживанию следующего запроса на передачу управления. Если следующий запрос на передачу управления, так же как и предыдущий, пред-. назначается для данного модуля, то на выходе элемента И 77,9 блока 4 выбора направления передачи управления единичный уровень сигнала не изменяется, так как содержимое буферного регистра 9 после перезаписи в него информации следующего запроса не изменяется. Следовательно, буферный регистр 8 продолжает хранение информации об адресе микрокоманды, с которой продолжено выполнение микро; программы после обработки всех; зап-. росов, предназначенных для этого мо- дуля.Единичный уровень сигнала на Я- ) входе КБ-триггера 22 не изменяется. Импульс с одновибратора 21 по окончании микропрограммы запроса на передачу управления обнуляет КБ-триггер 22 на время длительности импульса. Возвращение КЯ-триггера 22 в единичное состояние сопровождается импульсом с одновибратора 23, который через блок 16 элементов ИЛИ и с КЯ -триггера 17 пуска запускает генератор 18 тактовых импульсов и далэ) нейшее функционирование происходит аналогично указанному.Если следующий запрос на передачу управления в отличие от предыдущего предназначен для транзитной передачи, то дальнейшее продвижение очереди приводит к появлению нулевого сигнала на выходе элемента И 77.9 олока 4 выбора,направления передачи15 ,11 управления, так как характер информации, хранящейся в буферном регистре 9, изменяется. Импульс, сформированный одновибратором 21, по окончании программы обнуляет КЯ-триггер 22 и через элемент ИЛИ 33 регистр 66 запоминающего блока 1 адресных микро-" команд, Импульс с одповибратора 20 разрешает прохождение информации об адресе следующей микрокоманды из буферного регистра 8 через блок 14 элементов И на вход 42 запоминающего блока 1 адресных микрокоманд, и модуль переходит к обработКе собственной микропрограммы и транзитной передачи управления одновременно,93675 16Таким образом, прерывание текущей микропрограммы происходит тольков режимах обработки собственной подпрограммы и в режиме обработки запроса на передачу управления от другогоаналогичного модуля. В режиме обработки собственной микропрограммы, врежиме передачи управления аналогичному модулю и в режиме транзитной 10 передачи управления аналогичному модулю прерывания текущей микропрограммыт.е. запоминание адресаследующей микрокоманды в первомбуферном регистре 8): не происхо дит.,4/ Патент" оектная, 4 Ужгород,Тираж 709 Подписное ИИПИ Государственного комитета СССР по делам изобретений и открытий 3035, Москва, Ж, Раушская наб.,схемы сравнения и девять элементовИ, причем выход третьего блока элементов И соединен с вторым адреснымвходом запоминающего блока адресныхмикрокоманд, третий адресный входкоторого соединен с выходом кода косвенного адреса следующей адресноймикрокоманды запоминающего блока адресных микрокоманд, четвертый адресный вход которого соединен с выходомчетвертого блока элементов И, первый вход которого соединен с выходом третьего буферного регистра,информационный вход которого соединен с выходом второго блока элементов И, второй вход которого соединенс первым входом первого элемента ИЛИи с выходом первого одновибратора,вход которого соединен с первым инверсным входом первого элемента И,с выходом первого элемента И блокавыбора направления передачи управления, с инверсным входом пятогоблока элементов И, с входом установки в "1" триггера состояния обработки запроса .и с входом второго одновибратора, выход которого соединенс вторым входом второго блока элемен.тов И, пятый адресный вход запоминающего блока адресных микрокомандявляется входом условий модуля, входустановки в 0 триггера состоянияобработки запроса соединен с первымивходами второго и третьего элементов ИЛИ, с первым управляющим входомблока регистров приема и с выходомтретьего одновибратора, вход которого соединен с выходом признака концаподпрограммы запоминающего блока адресных микрокоманд, вход начальнойустановки которого соединен с выходом второго элемента ИЛИ, второйвход которого соединен с инверснымвходом третьего блока элементов И,свторым входом первого элемента ИЛИ,с выходом четвертого одновибратораи с входом элемента задержки, выходкоторого соединен с вторым входомпервого блока элементов И, выходтриггера состояния обработки запросасоединен с входом четвертого одновибратора, выход первого элементаИЛИ соединен с входом установки в"1" триггера пуска, прямой входтретьего блока элементов И и третийвход первого элемента ИЛИ подключенк входу кода команды модуля, выходкода операционной части запроса на передачу управления регистра передачи управления соединен с первыми входами третьего и четвертого блоков элементов ИЛИ, выходы которых соеди- нены соответственно с прямьпк входбмпятого блока элементов И и с информационным входом первого буферногорегистра, вход установки в "О" которого соединен с входом установки в "О" четвертого буферного регистра и с выходом пятого одновибратора, вход которого соединен с выходом второго элемента И, первый инверсный вход которого соединен с вторым управляющим входом блока регистров приема и с выходом признака наличия собственного адреса регистра передачи управления, выход кода адресной части запроса на передачу управления которого соединен с первым входом второго блока элементов ИЛИ и с вторым входом третьего блока элементов ИЛИ, третий вход которого соединен с первым информационным чвыходом блока регистров приема и с вторым входом второго блока элементов ИЛИ, выход которого соединенс информационным входом четвертогобуферного регистра, выход которогосоединен с первыми входами первойи второй схем сравнения, второй информационный выход блока регистров приема соединен с четвертым входом третьего блока элементов ИЛИ и с вторим входом четвертого блока, эле-, ментов ИЛИ, информационный вход блока регистров приема соединен с выходом первого блока элементов ИЛИ, вход начальной установки модуля подключен к входу начальной установки блока регистров приема, третий управляющий вход которого соединен с .выходом первого элемента И, второй инверсный вход которого соединен с выходом четвертого элементаИЛИ, входы которого с первого по восьмой соединены соответственно с первого по восьмой управляющими входами демультиплексора и с выходами соответственно с второго по девятый элементов И блока выбора направления передачи управления, вторые входы схем сравнения соединены с выходом регистра собственного адреса, информационный вход которого является входом собственного адреса модуля, выход пятого блока элементов И соединен с информационным входом выходного регистра, выход которого соединен с информационным входом демультиплексора и с входом пятого элемента ИЛИ, выход которого соединен через шестой одновибратор с входом установки в ."0" выходного регистра, с четвертымуправляющим входом блока регистров приема и с вторым входом третьего элемента ИЛИ, выход которого соединен с входом установки в "0" регистра передачи управления, второй инверсный вход второго элемента И соединен с третьим информационным выходом блока регистров приема, выходы с первого по восьмой демультиплексора являются соответственно с второго по девятый управляющими выходами модуля, первые входы второго, третьего и четвертого элементов И блока выбора направления передачи управления соединены с выходом "Больше" первой схемы сравнения, выход "Меньше" которой соединен с первыми входами пятого, шестого и седьмого элементов И блока выбора направления передачи управления, выход "Равно" первой схемы сравнения соединен с первыми входами первого, восьмого и девятого элементов И блока выбора направления передачи управления, выход "Больше" второй схемы сравнения соединен с вторыми входами второго, пятого и восьмого .элементов И блока выбора направления передачи управления, выход "Меньше" второй схемы сравнения соединен с вторыми входами третьего, шестого и девятого элементов И блока выбора направления передачи управления, выход "Равно" второй схемы сравнения соединен с вторыми входами четвертого, седьмого и первого элементов И блока выбора направления передачи.2. Модуль по п.1, о т л и ч а ю - щ и й с я тем, что блок регистров приема содержит группу из р регистров (ь = 1, 2,), группу из (иблоков элементов ИЛИ, группу из в блоков элементов И, группу из л элементов ИЛИ, группу изкоммутаторов, блок элементов И, элемент И и элемент ИЛИ, причем входы установки в нОв регистров группы подключены к входу начальной установки блока, первый управляющий вход блока подключен к первому входу элемента ИЛИ, второй и третий входы которого подключены соответственно к третьему и четвертому управляющим входам блока,выход элемента ИЛИ подсоединен. к первому прямому входу элемента И, инверсный вход которого подключен к второму управляющему входу модуля, второй прямой вход элемента И соединен с первыми управляющими входамис второго по Ь)-й коммутаторовтгруппы, с управляющим входом первого коммутатора группы и с выходом первого элемента ИЛИ группы, который . является третьим информационным выхо. дом блока, остальные управляющиевходы с второго по .(й)-й коммутаторов группы соединены с соответ-.ствующими выходами с второго по;-1)-й элементов ИЛИ группы, выход 1-го регистра группы (1=1,2,й)соединен с первым входом 1 -го блока элементов И группы и с входом 1-го элемента ИЛИ группы, информационный вход 1-го регистра группы ( 1 = 1,2, л) соединен с выходом 1-го блока элементов ИЛИ группы, первый и второй входы которого соединены соответственно с выходами 1-го коммутатора группы и , 1 +1)- го блока элементов И группы, информационный вход о-го регистра группы соединен с выходом и-го коммутатора, первый управляющий вХод которого соединен с выходом л -го коммутатора группы и с первым инверсным входом блока элементов И, остальные управляющие входы и-гокоммутатора соединены с соответствующими выходами с второго по (в)-й коммутаторов группы, выход элемента И соединен с вторыми входами с первого по -й блоков элементов И группы и с вторым инверсным входом блока элементов И, прямой вход которого является информационным входом блока, первый и второй выходы первого блока элементов И группы являются соответственно первым и вторым информационными выходами модуля.3. Модуль по п.1, о т л и ч а ющ и й с я тем, что запоминающий блок адресных микрокоманд содержит постоянную память, дешифратор, регистр, группу сумматоров по модулю два, элемент задержки и блок элементов ИЛИ, причем первый, второй, третий и четвертый входы блока элементов ИЛИ являются соответственно первым, вторым, третьим и четвертым адресными входами блока, первый выход119 группы выходов блока элементов ИЛИ соединен с первыми входами сумматоров по модулю два группы, остальные выходы . группы блока элементов ИЛИ соединены с первой группой информационных входов регистра, вторая группа информационных входов которого подключена к выходам сумматоров по модулю два группы, вторые входы которых подключены к пятому адресному входу блока, вход установки в "0" регистраявляется входом начальной установки блока, выход регистра соединен с информационным входом дешифратора, стробирующий вход которого соединен с входом элемента задержки 3675и является входом синхронизации блока, выход элемента задержки является выходом признака обращения к запоминающему блоку операционных микрокоманд блока, выход дешифратора соединен с адресный входом постоянной памяти, первый, второй, третий, четвертый и пятый выходы которой являются соответственно выходами кода адреса операционной микрокоманды блока, кода косвенного адреса следующей адресной микрокоманды блока, кода операции. блока, кода адреса передачи управления блока и признака конца подпрограммы блока.Изобретение относится к вычислительной технике и может быть использовано при построении высокопроизводительных управляющих и вычислительных систем с использованием множества 5 25 однотипных микропрограммных управляющих устройств (модулей).Цель изобретения - расширение области применения модуля путем организации транзитной передачи управляющей .10информации,На фиг.1 представлена функциональная схема предлагаемого микропрограммного модуля; на фиг.2 - функциональная схема запоминающего блока 15адресных микрокоманд; на фиг,3 -функциональная схема блока регистровприема; на фиг.4 - функциональнаясхема блока выбора направления передачи управления, 20Микропрограммный модуль распределенной вычислительной системы(фиг. ) содержит запоминающий блок 1адресных микрокоманд, блок 2 памятиоперационных микрокоманд, блок 3регистров приема, блок 4 выбора напРавления передачи управления, регистр5 передачи управления с выходами 5,15,3 соответственно кода операционнойчасти запроса на передачу управления, 30кода адресной части запроса на передачу управления и признака наличиясобственного запроса данного модуля,регистр 6 собственного адреса, второй 7, третий 8, четвертый 9 и первый 10 буферные регистры, выходной регистр 11, третий 12, второй 13 и четвертый 14 блоки элементов И, второй 15 и первый 16 блоки элементов ИЛИ, триггер 17 пуска, генератор 18 тактовых импульсов, второй 19, первый 20 и третий .21 одновибраторы, триггер 22 состояния обработки запроса, четвертый одновибратор 23, элемент 24 задержки, третий блок 25 элементов ИЛИ, пятый элемент ИЛИ 26, шестой одновибратор 27, четвертый элемент ИЛИ 28, первый элемент И 29, первый блок 30 элементов ИЛИ, четвертый блок 31 элементов ИЛИ, первый блок 32 элементов И, второй элемент ИЛИ 33, вход 34 кода команды, вход 35 логических условий, вход 36 собственного адреса, группу входов 37.1 37.8 запросов на передачу управления, вход 38 начальной установки, первый управляющий выход 39, с второгр 40.1. по девятый 40,8 управляющие выходы, третий 41, четвертый 42, первый 43, второй 44 и пятый 45 адресные входы запоминающего блока адресных микрокоманд, вход 46 синхронизации запоминающего блока адресных микрокоманд, выход 47 кода адреса операционной микрокоманды запоминающего блока адресных микрокоманд, выход 48 признака обращения к блоку памяти операционных микрокоманд запоминающего блока адресных микрокоманд, выход 49 кода косвенного адреса следующей3 11адресной микрокоманды запоминающегоблока адресных микрокоманд, выход 50кода операции запоминающего блокаадресных микрокоманд, выход 51 кодаадреса передачи управления, выход 52признака конца подпрограммы запоминающего блока адресных микрокоманд,третий 53 и четвертый 54 управляющиевходы блока регистров приема, информационный вход 55 блока регистровприема, втррой 56 и первый 57 управляющие входы блока регистров приема, вход 58 начальной установкиблока регистров приема, пятый блок59 элементов И, второй элемент. И 60,пятый одновибратор 61, третий элемент ИЛИ 62 и демультиплексор 63.Запоминающий блок адресных микрокоманд содержит (фиг.2) блок 64элементов ИЛИ, группу сумматоров 65по модулю два, регистр 66, дешифратор 67, постоянную память 68 иэлемент 69 задержки.1Блок 3 регистров приема содержит(фиг,3 ) группу блоков 70.1 в 70. ь элементов И, группу элементов ИЛИ 71.171. и, блок 72 элементов И, элементИЛИ 73, элемент Й 74, группу регистров 75,1 -75 и и группу коммутаторов. 76.1 - 76.п,Блок 4 выбора направления передачи управления содержит (фиг,4)девять элементов И 77,1 - 77.9 и двесхемы 78 и 79 сравнения.Микропрограммный модуль функционирует в пяти режимах; режиме обработки собственной микропрограммы,режиме обработки собственной подпрог"раммы, режиме передачи управленияаналогичному модулю, режиме транзитной передачи управления н режиме обработки запроса на передачу управления от другого аналогичного модуля системы.В этих режимах в начальный моментвсе регистры модуля обнулены, и в регистр 6 собственного адреса записана информация о коде номера строкии столбца данного микропрограммногомодуля.Работа микропрограммного модуляв режиме обработки собственной микропрограммы начинается путем подачина вход 34 модуля команды, определяющего начальный адрес микропрограммы.Так как триггер 22 находится в нулевом состоянии (нет запросов от самогоустройства на обработку собственнок 93675 4подпрограмм и запросов на обработкуэтим модулем сигналов со стороныдругих аналогичных модулей ), то сигнал с выхода одновибратора 23 разрешает прохождение с входа 34 устройства начального адреса выполняемоймикропрограммы через блок 12 эяементов И и блок 64 элементов ИЛИ на информационный вход регистра 66. запоми нающего блока 1 адресных микрокомаид.фиг. 2). Подача кода операцииопределяющего начальный адрес микро- .программы, на вход 34 микропрограммного модуля через блок 16 элементов ИЛИ обуславливает единичный сигнал на Я-входе КЯ-триггера 17 пускаи устанавливает его в единичное состояние, запуская тем самым генератрр18 тактовых импульсов, сигнал с выхода которого поступает на вход 46 синхронизации запоминающего блока адресных микрокоманд, инициируя начало выполнения микропрограммы. По приходуна стробирующий вход дешифратора 67 25 импульса с входа 46 запоминающегоблока адресных микрокоманд происхо- .дит выборка управляющей информациииз памяти 68 по адресу, .записанномув регистре 66, С памяти 68 запоминающего блока 1 адресных команд счи"тывается микрокоманда, формат которой определяет адрес операционноймикрокоманды (выход 47), косвенныйадрес следующей адресной микрокоманды (выход 49) признак окончания.35выполнения микропрограммы (выход 52),адрес модуля, которому передаетсяуправление ( выход 51 ), код операции микропрограммы, которой передается управление (выход 50).По коду адреса операционной микрокоманды с выхода 47 считываетсямикрокоманда из блока 2 памяти науправление, например АЛУ процессора 45или другим операционным блокомсредств обработки информации. Код адреса следующей адресной микрокоманды, снимаемый с выхода 49запоминающего блока 1 адресных микрокоманд, содержит. постоянную (А) и переменную (А )части. Переменная часть кода адреса следующей адресной мнкрокоманды определяет модифициру емую часть адреса поступающими логическими условиями на вход 35 запоминающего блока 1 адресных микрокоманд. Код косвенного адреса следующей адресыой микрокоманды с выхода40 3 1193649 поступает на вход 41 и через блок64 элементов ИЛИ записывается в регистр 66. Поступающие с входа 35 логические условия модифицир 9 от переменную часть кода на группе сумма 5торов по модулю два (65,1 - 65,о). Взависимости от поступивших логических условий в регистре 66 формируется адрес очередной адресной микрокоманды, который по приходу импуль Оса с входа 46 производит выборку но-.вой адресной микрокоманды из памяти68 запоминающего блока 1 адресныхмикрокоманд, По приходу сигнала свыхода 52 запоминающего блока 1 адресных микрокоманд по окончании выполнения микропрограммы на выходеодновибратора 21 формируется импульс,который через элемент ИЛИ 33 обнуляет .регистр 66 запоминающего блока 201 адресных микрокоманд, сигнал обокончании микропрограммы с выходапризнака конца подпрограммы блока2 памяти операционных микрокомандпоступает на К-вход КЯ-триггера 25пуска и обнуляет его, что прекращаетработу генератора тактовых импульсов,Микропрограммный модуль переходит висходное состояние,При работе микропрограммного модуля в режиме обработки собственнойподпрограммы в определенном участкемикропрограммы находится микрокоманда, осуществляющая выдачу запроса на обработкусобственной под- З 5программы, В формате микрокоманды спамяти 68 запоминающего блока адресных микрокоманд поступает информацияоб адресе следующей микрокоманды свыхода 49 на вход 41 запоминающегоблока 1 адресных микрокоманд ивход буферного регистра 7, которыйхранит текущее значение адреса следующей микрокоманды. Одновременнос этим на первый информационный 45вход регистра 5 передачи управленияс выхода 50 запоминающего блока 1адресных микрокоманд считываетсякод адреса микрокоманды, с котороймикропрограммный модуль должен на-50чать выполнение подпрограммы, С выхода 51 запоминающего блока адресных микрокоманд на второй информационный вход регистра 5 передачиуправления считывается информация 55от адреса модуля, которому передается управление; в режиме обработкисобственной подпрограммы - это соб 75 Фственный адрес данного микропрограммного модуля (код номера строки и номера столбца ) в распределенной управляющей системе. Выдача данным модулем запроса на передачу управления инициализуется единичным сигналом метки-признака, записанным в поле 5.3 регистра 5 передачи управления, Этот единичный сигнал, поступая на вход 56 блока 3 регистров приема, является запрещающим сигналом (через эле-.1мент И 74 и блоки 70. 1 - 70.п элементов И для выдачи информации из блока 3 регистров приема, который организован как очередь запросов на передачу управления от аналогичных Модулей по типу "Первый принят - первый обслужен", Таким. образом, при выдаче собственного запроса на передачу управления данным модулем запрещаются режим транзитной передачи управления и режим обработки запроса на передачу управления от другого аналогичного модуля, т.е. собственный эапцрос на передачу управления обладает высшим (абсолютным) приоритетом,С поля,5.2 регистра 5 передачи управления информация о собственном адресе данного модуля поступает через блок 15 элементов ИЛИ и буферный регистр 9, который хранит текущее значение этой информации, на первый вход блока 4 выбора направления передачи управления. Информация о собственном адресе данногр модуля в распределенной управляющей системе поступает с регистра 6 собственного адреса на второй вход блока 4 выбора направления передачи управления, где происходят сравнение адресов запроса на передачу управления и данного модуля и выработка девяти управляющих сигналов, восемь из которых дают точную информацию о направлении передачи управляющей информации одному из восьми соседних модулей, наличие девятого сигнала на втором выходе блока 4 указывает на необходимость обработки запроса на передачу управления данным микропрограммным модулем.Единичный сигнал с второго выхода блока 4 выбора направления передачи управления устанавливает КЯ-триггер 22 состояния обработки запроса в единичное состояние и через одно- вибратор 19 разрешает перезапись информации от адреса следующей микро5 10 15 20 команды.из буферного регистра 7 вбуферный регистр 8, где он и хранится все время обработки запроса. Установка КБ-триггера 22 в единичноесостояние через одновибратор 23 иэлемент ИЛИ 33 обнуляет регистр 66запоминающего блока 1 адресных микрокоманд, импульс с одновибратора 23подтверждает запуск тактового генератора и запрещает прохождение информации о начальном адресе микрокоманды с входа 34 модуля через блок12 элементов И на вход 44 запоминающего блока 1 адресных микрокоманд.Импульс с одновибратора 23 через элемент 24 задержки поступает с задержкой, необходимой для установки в нулевое состояние регистра 66 запоминающего блока 1 адресных микрокоманд,на разрешающие входы блока 32 элементов И,разрешая перезапись информациио коде адреса подпрограммы из буферного регистра 10, куда информация.записана через блок 31 элементов ИЛИиз поля 5, 1 регистра 5 передачи управления, в регистр 66 через блок64 элементов ИЛИ и вход 43 запоминающего блока 1 адресных микрокоманд.Запоминающий блок 1 адресных микрокоманд, получив информацию по входу43, функционирует аналогично режимуобработки собственной микропрограммы.Конец выполнения подпрограммы инициируется единичным сигналом на выходе 52 запоминающего блокаадресныхмикрокоманд и выходе признака концаподпрограммы блока памяти операци.онных микрокоманд, по которым прекращает работу генератор тактовых им" пульсов. Через одновибратор 21 сигнал с выхода 52 запоминающего блока 1адресных микрокоманд обнуляет КБ-триггер состояния обработки запроса, черезодновибратор 21 и элемент ИЛИ 33 об-нуляется регистр 66 запоминающегоблока 1 адресных микрокоманд, черезодновибратор 21 и элемент ИЛИ 62обнуляется регистр 5 передачи управления, и при допущении пустой очереди через элемент И 60 одновибратор61 формирует импульс на обнулениебуферньи регистров 9 и 1 О, что ведетк появлению нулевого сигнала на выходе элемента И 77, блока 4 выборанаправления передачи управления. Поэтому сигналу подтверждается нулевое состояние КВ-триггера 22,одновибратор 20 формирует импульс, который разре-25 30 35 40 45 50 55 шает перезапись информации об адресе хранимой следующей микрокоманды из буферного регистра 8 через блок 14 элементов И и блок 64 элементов ИЛИ в регистр 66 запоминающего блока 1 адресных микрокоманд и через блок 16 элементов ИЛИ устанавливает КБ- триггер 17 пуска в единичное состояние, инициируя работу генератора 18 тактовых импульсов для продолжения синхронного выполнения прерванной микропрограммы. Глубина прерывания текущей микропрограммы запросом на обработку собственной подпрограммы равна единице. Продолжение обработки прерванной микропрограммы происходит аналогично режиму обработки собственной микропрограммы.При работе модуля в режиме передачи управления аналогичному модулю в определенном участке микропрограммы находится микрокоманда, осуществляющая выдачу запроса на передачу управления аналогичному микропрограмномумодулю и состоящая из двух частей. В первой части содержится информация о коде микропрограммы (адрес микрокоманды, с которой необходимо начать выполнение микропрограммы ), во второй части - об адресе микропрограммного модуля, которому передается управление, т.е. код номера строки и номера столбца модуля в распределенной управляющей системе.В формате микрокоманды с памяти 68 запоминающего блока 1 адресных микрокоманд . считывается информация об адресе следующей микрокоманды с . выхода 49 на вход 41 и буферный регистр 7, хранящий текущее значение адреса следуюшей микрокоманды. При необходимости передачи управления аналогичному модулю микрокоманда, осуществляющая эту передачу, записывается в регистр 5 передачи управления. На его первый информационный вход поступает информация о первой части микрокоманды (код микропрограммы по передаче управления ), на второй информационный вход - о второй части микрокоманды (адрес микропрограммного модуля, которому передается управление ). Выдача запроса на передачу управления другому аналогичному модулю иниализируется единичным сигналом с выхода 5,3 признака регистра 5 передачи управления, где хранится управляющая ин 9 1формация до окончания обработки этого запроса. Сигнал метки-признакаполя 5,3 регистра 5 передачи управления, поступая на вход блока 3регистров приема, запрещает обработку запросов на передачу управления от других аналогичных модулей(движение очереди запросов не происходит). Информация об адресемодуля, которому передается управление с поля 5.2 регистра 5 передачи управления через блок 15 элементов ИЛИ и буферный регистр 9,который хранит текущее состояние этойинформации, поступает на соответствующий вход блока 4 выбора направления передачи управления, где онасравнивается с содержимья регистра6 собственного адреса, информацияс которого поступает на соответствующий вход блока 4 выбора направления передачи управления, которыйфункционирует аналогично режиму обработки собственной подпрограммы.Восьмиразрядный код направления передачи управления информации поступает на управляющий вход демультиплексора 63, определяя тем самым одно из восьми возможных направленийвыдачи информации: "Вверх", "Влево","Вверх-вправо", "Вниз-влево", "Вниэвправо".Нулевой, сигнал на выходе элемента И 7.9 блока 4 выбора направления передачи управления через одновибратор 19 запрещает перезапись адреса следующей микрокоманде из буферного регистра 7 в буферный регистр 8,т.е. выполнение текущей микропрограммы после выдачи запроса на передачу управления в данном режиме не прерывается, а функционирование модуля продолжается аналогично режиму обработки собственной микропрограммы, Управляющая информация из регистра 5 передачи управления через блок 25 элементов ИЛИ и блок 59 элементов И по разрешающему нулевому сигналус блока 4 выбора направления передачи управления переписывается в выход-. ной регистр 11, откуда поступает на информационный вход демультиплексора 63, который осуществляет выдачу управляющей информации соседнему ана-. логичному модулю в соответствии с кодом на своем управляющем входе. По сигналу выдачи управляющей информа 193675 10ции в демультиплексор 63 через эле- .мент ИЛИ 26 одновибратор 27 формирует импульс, который с задержкой, необходимой для завершения переход-.ных процессов по передаче управляющей информации соседнему аналогичному модулю с демультиплексора 63, обнуляет выходной регистр и через элемент ИЛИ 62 обнуляет буферные 10 регистры 9 и 10, Микропрограммныймодуль переходит в исходное состояние.Соседний микропрограммный модуль,получив по своему адресу управляющую 15 информацию, либо принимает на обработку запрос на передачу управления (если адрес запроса и адрес этого модуля идентичны ), либо осуществляет транзитную передачу управляющей ин формации (если адрес запроса и адресэтого модуля не совпадают).В режиме .транзитной передачи управ=ления запросы на передачу управления с других аналогичных микропрограммных 25 модулей поступают на входы 37, 1 - 37,8модуля, откуда через блок 30 элементов ИЛИ поступает на информационный вход 55 блока 3 регистров приема, который организован как очередь запросов на передачу управления типа "Первым поступил - первый обслужен". В начальный момент функционирования на вход 38 модуля (фиг.4) подается единичный сигнал, который, поступая на вход 58 блока 3 регист- .35ров приема, обнуляет регистры 75.1 - 75,п приема (где и - длина очереди), Так как до прихода запроса очередь: пуста, нулевой сигнал с выхода эле 40мента ИЛИ 71, 1 через элемент И 74 и нулевой сигнал с выхода элемента ИЛИ 71. и поступают на инверсные входы блока 72 элементов И, разрешая тем самым прием запросов на передачу управления в очередь "Первый принятпервый обслужен", Так как регистр 75. 1 пуст, то нулевой сигнал с элемента ИЛИ 71, 1 через коммутатор 76, 1 разрешает прием информации в первый регистр 75.1 очереди и через коммутатор 76:2 запрещает прием информации во второй регистр 75:2, нулевое значение которого в свою очередь через элемент ИЛИ 71.2 и коммутатор 76.2 является разрешающим сигналом для записи информации в регистр 75,1 и через элемент ИЛИ 71,2 и коьяутатор 76,5 является запрещающим сиг193675 12 51015 20 25 30 35 40 45 50 11 1 налом для записи информации в третий регистр 75,5 . Таким образом, группа элементов ИЛИ 71.1 - 71,п и группа коммутаторов 76.1 - 76.пметодом попарного запрета-разрешения меж" ду регистрами 75.1 - 75, и организует очередь так, что запись информации в блок 3 регистров приема осуществляется в строгой последовательности, начиная с регистра 75. 1 и кончая регистром 75 п . Так, например, в первый момент времени запись информации разрешена только в первый регистр 75.1 . После заполнения этого регистра единичный сигнал с элемента ИЛИ 71,1 запрещает через коммутатор 76. 1 запись информации в регистр 75. 1 разрешает запись следующего запроса на передачу управления во второй регистр 75.2 и т.д. Если очередь заполнена, то единичные,сигналы с группы элементов ИЛИ 711 - 71. и, поступая на управляющие входь коммутаторов 76.1 - 76.п, .запрещают прием информации во все регистры 75.1 - 75,п. Единичный сигнал с выхода элемента ИЛИ 71,п, поступая на инверсный вход блока 72 элементов И подтверждает этот запрет.Продвижение очереди осуществляется через группу блоков 70,1 - 70.п элементов И по разрешающему сигналу с выхода элемента И 74 при отсутствии собственной выдачи запроса на передачу управления (нулевОй сигнал с поля 5,3 регистра передачи управления поступает на вход 56 блока регистров приема, что являетсяинверсным входом элемента И 74) и при условии, что очередь содержит хотя бы одну заявку на передачу управления. ВО время продвижения очереди единичный сигнал с выхода элемента И 74 запрещает через блок 72 элементов И прием информации в блок 3 регистров приема. Продвижение очереди происходит по трем управляющим сигналам, единичное состояние которых говорит о возможности продвижения очереди в блоке 3 регистров приема. Первый сигнал поступает с выхода одновибратора 27 на вход 54 блока 3 регистров приема, если модуль производил либо транзитную передачу управления, либо передачу собственного запроса управляющей информации в со-седний аналогичный модуль. Второй сигнал продвижения очереди поступает с выхода одновибратора 21 на вход 57блока 3 регистров приема после окончания выполнения микропрограммы позапросу на передачу управления. Третий управляющий сигнал продвиженияочереди поступает с выхода элементаИ 29 на вход 53 блока 3 регистровприема, задает начальное продвижениеочереди, если модуль до данного момента времени функционировал тольков режиме обработки собственной микропрограммы. При отсутствии собственного запроса на передачу управления(признак поля 5.3 регистра 5 передачи управления в нулевом состоянии )и появлении очереди в блоке 3 регистров приема сформированный до этого на блоке 4 выбора направленияпередачи управления нулевой сигнал на всех его выходах через элемент ИЛИ 28 и элемент И 29 разрешаетначальное продвижение очереди. Информация об адресе микропрограммногомодуля, которому необходимо передатьуправление через блок 1 элементовИЛИ и буферный регистр 9, который хранит текущее значение этойинформации, поступает на соответству.ющий вход блока 4 выбора направления передачи управления, где сравнивается с адресной информацией данного модуля, которая поступает насоответствующий вход блока 4 выборанаправления передачи управления с регистра 6 собственного адреса модуля, и вырабатывается код адреса передачи управления, который поступаетна управляющие входы демультиплексора 63, Управляющая информация с .блока регистров приема поступает на блок 25 элементов ИЛИ, откуда по разрешающему сигналу с выхода элемента И 77,5 блока 4 выбора направления переда-чи управления через блок 59 элементов И записывается в выходной ре-гистр 11, откуда поступает на демультиплексор 63. Выдача информации одному из соседних микропрограммных модулей происходит аналогично режиму передачи управления аналогичному модулю. Когда выдача информации за вершена, импульс с выхода одновибра- .тора 27, поступая на вход 54 блока 3 регистров приема, разрешает продвижение очереди, если очередь не пуста и .нет собственных запросов на передачу управления данного модуля. Если появляется собственный запрос на

СмотретьЗаявка

3738231, 04.05.1984

ФИЛИАЛ "ВОСХОД" МОСКОВСКОГО ОРДЕНА ЛЕНИНА И ОРДЕНА ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ АВИАЦИОННОГО ИНСТИТУТА ИМ. СЕРГО ОРДЖОНИКИДЗЕ

МЕЛЬНИКОВ ВЛАДИМИР АЛЕКСЕЕВИЧ, САМОШИН ВЛАДИМИР НИКОЛАЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммный, модуль

Опубликовано: 23.11.1985

Код ссылки

<a href="https://patents.su/14-1193675-mikroprogrammnyjj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный модуль</a>

Предыдущий патент: Аналого-цифровой интегратор синусоидальных сигналов

Следующий патент: Устройство приоритета с шифрацией номера абонента

Случайный патент: 411499