Аналоговый декодер кода с ортогональными проверками

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

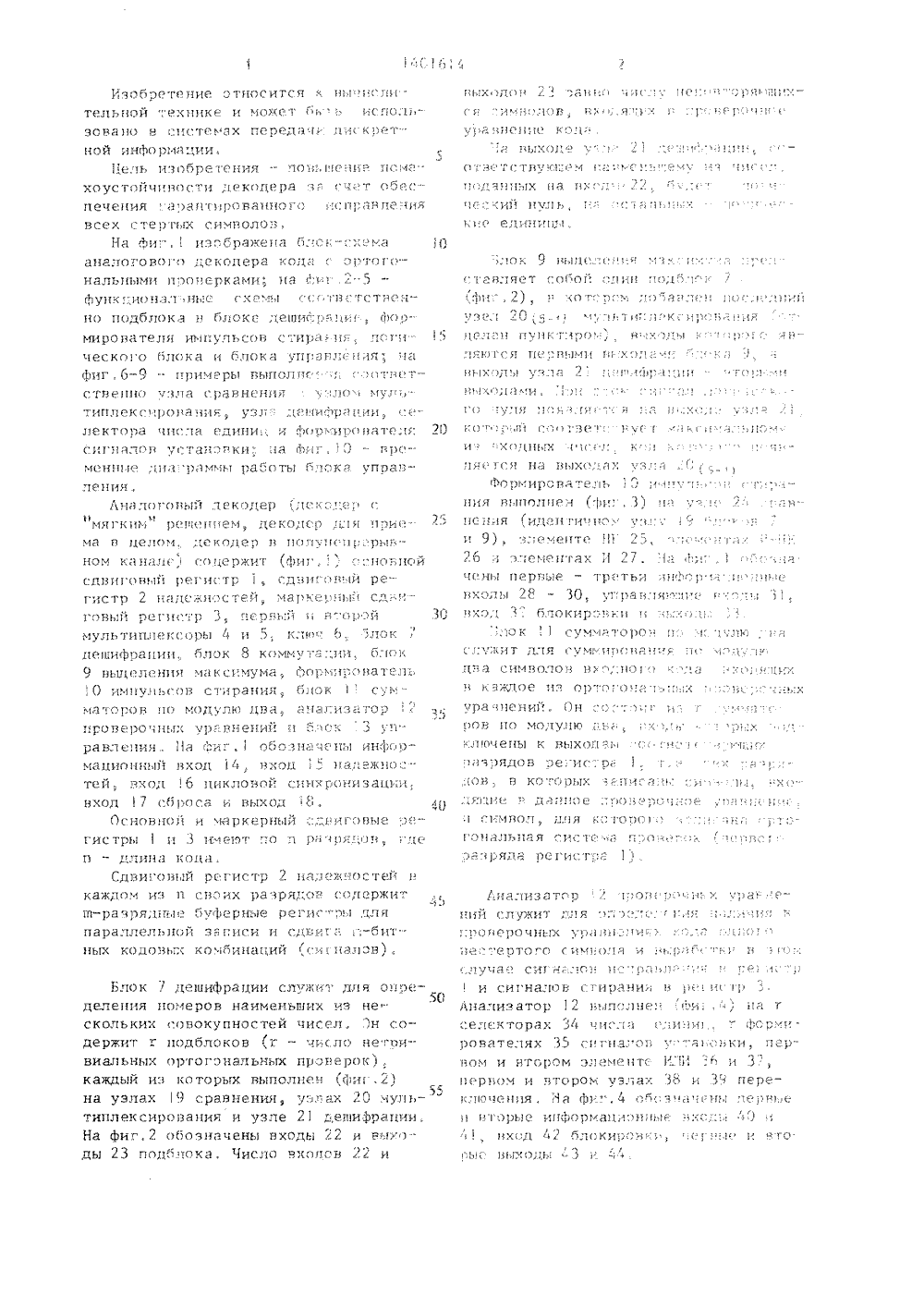

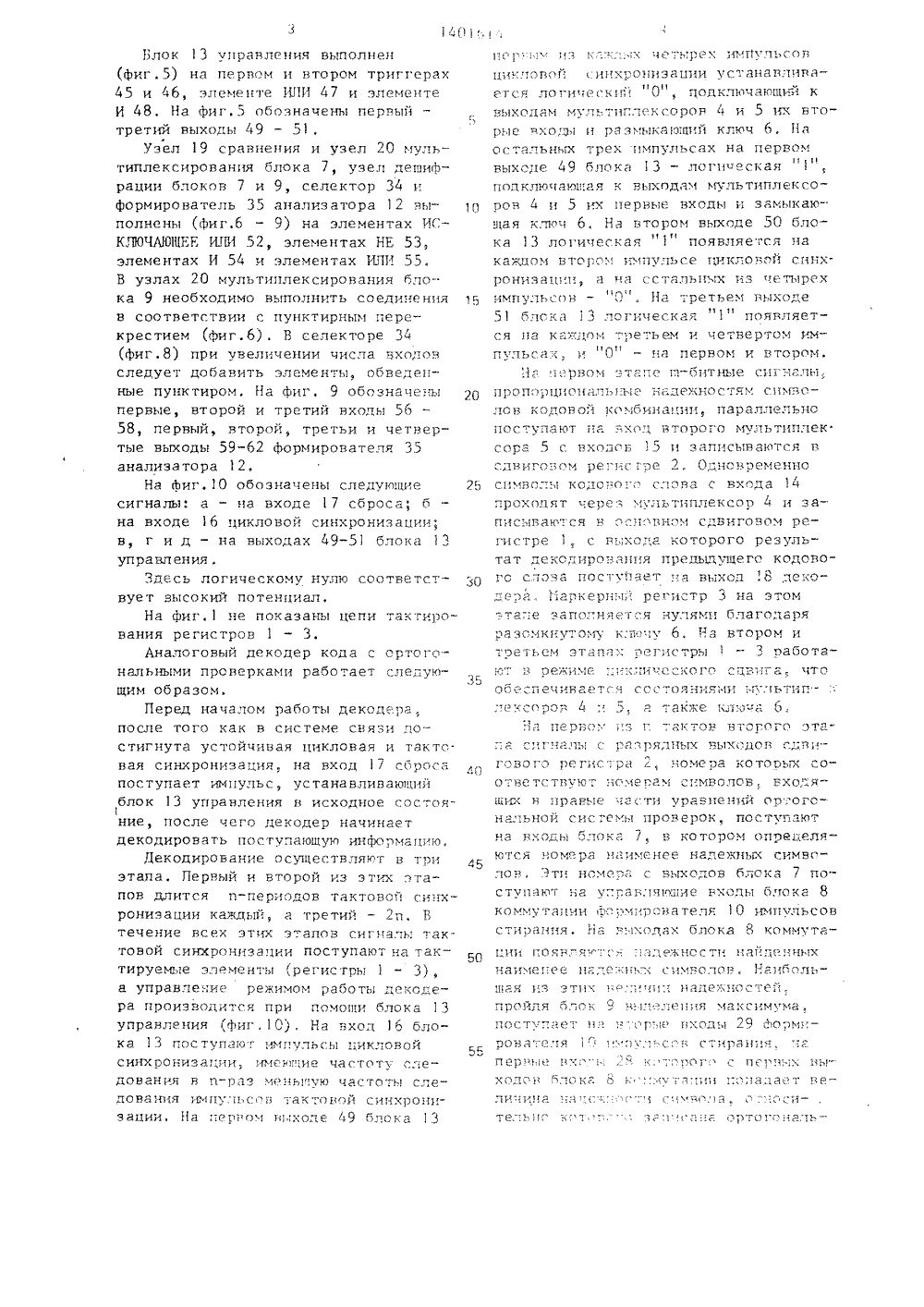

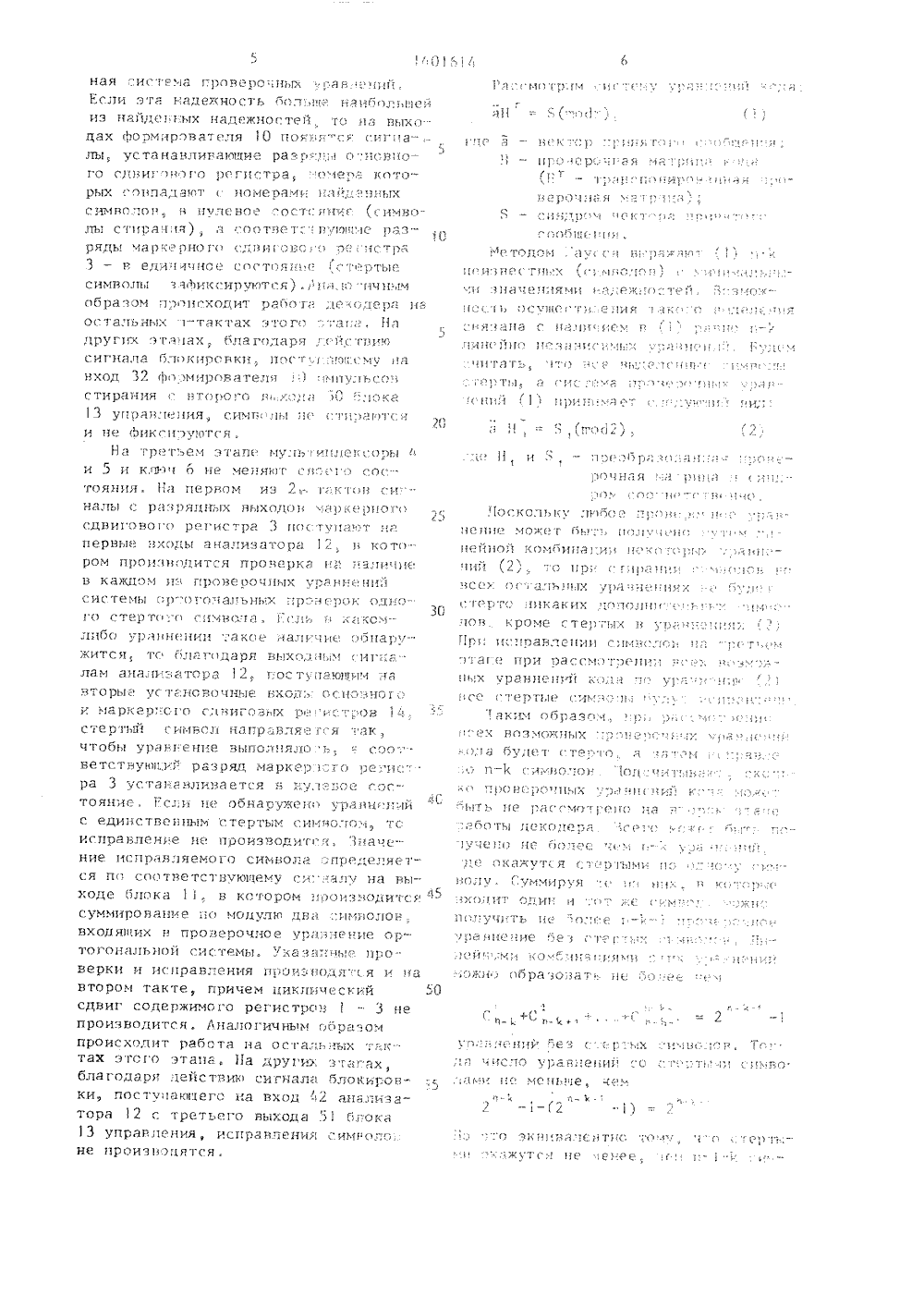

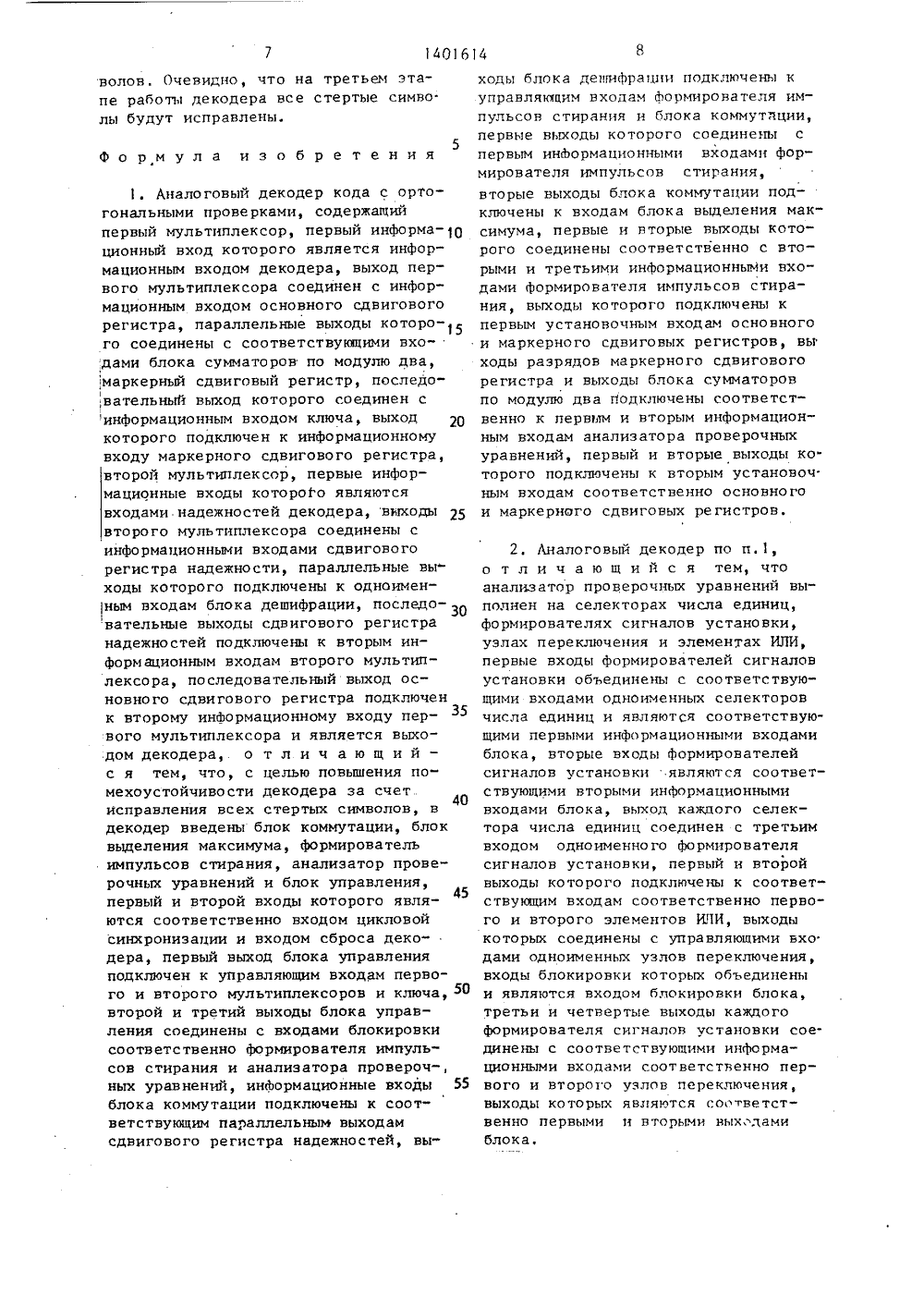

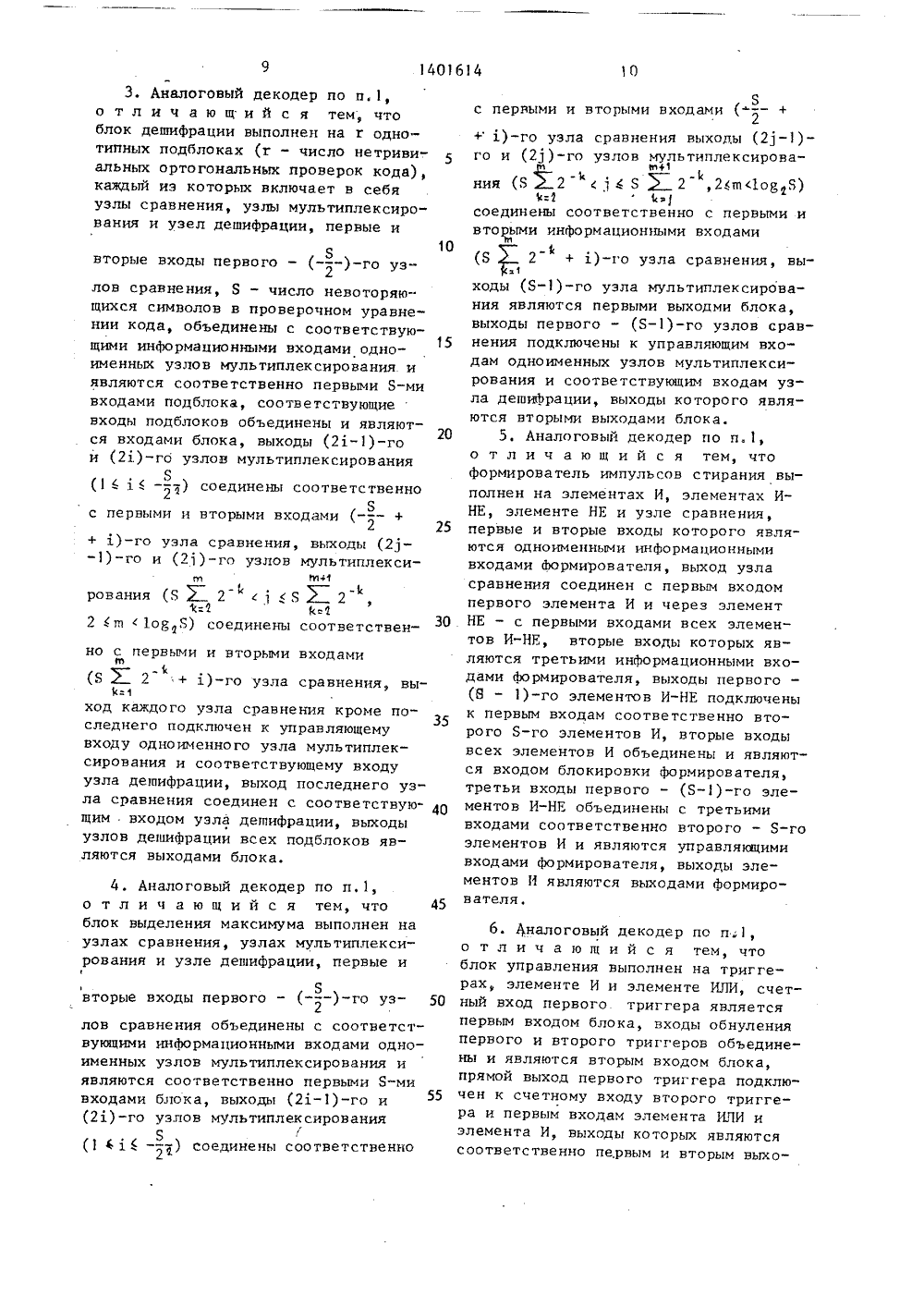

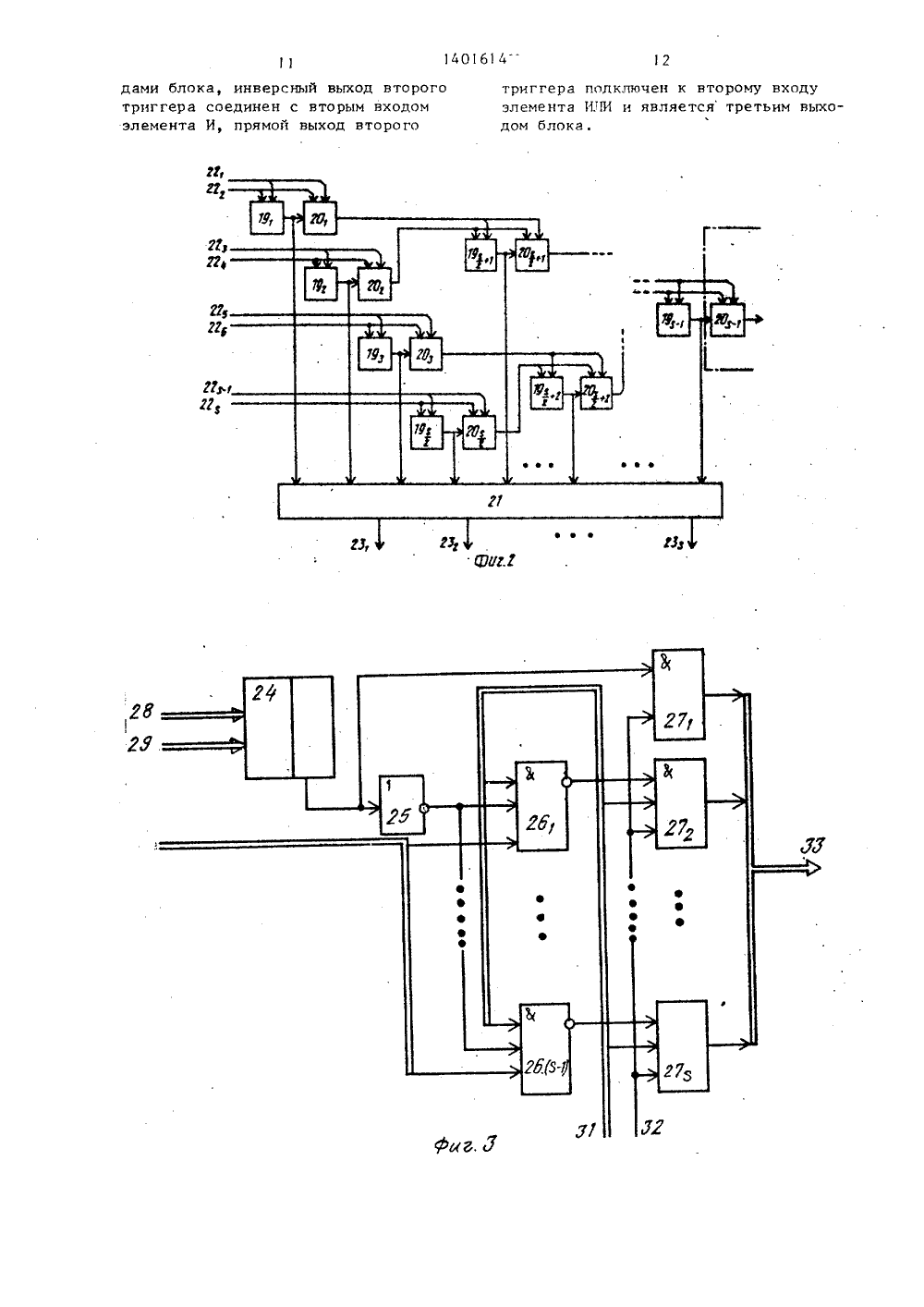

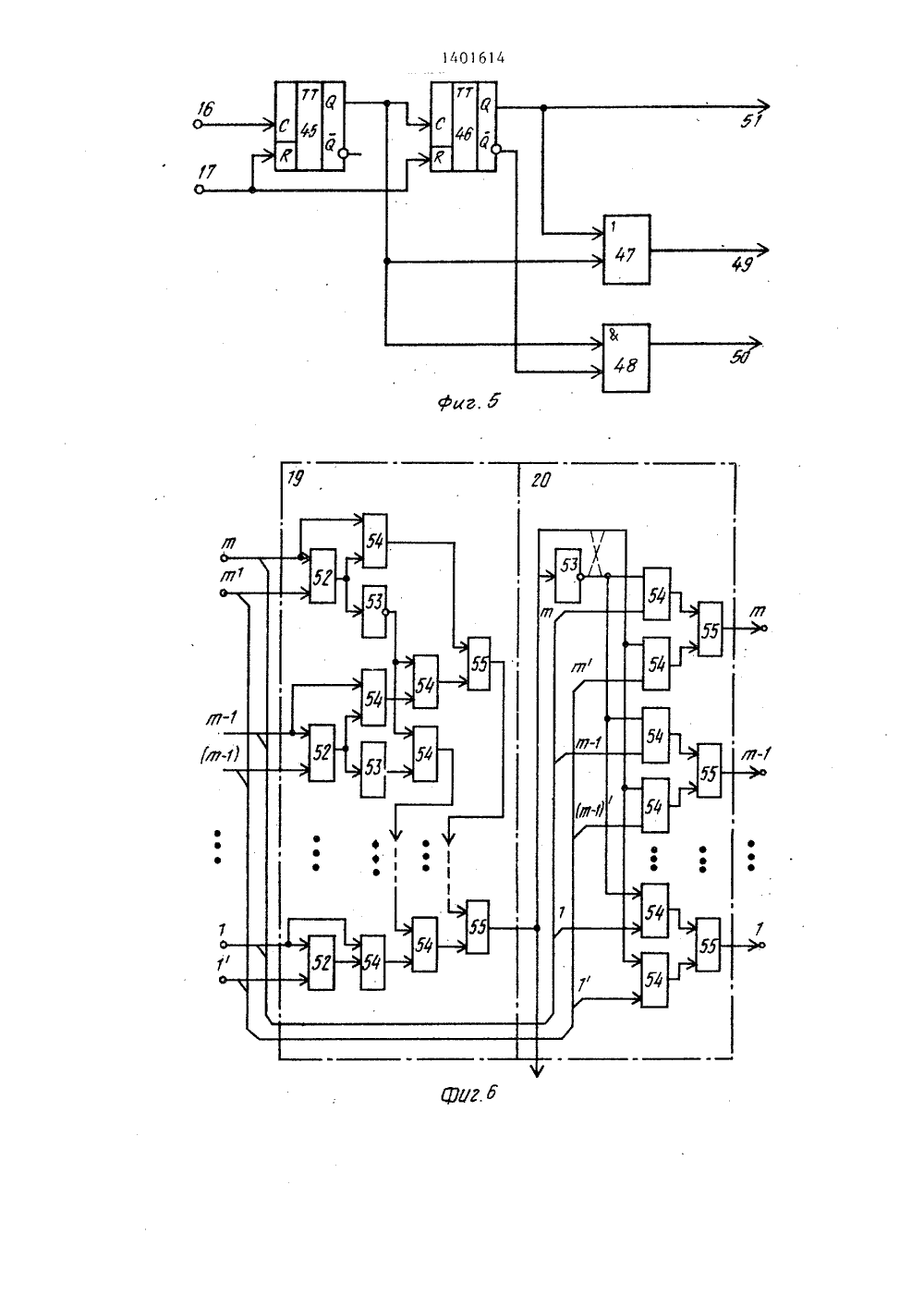

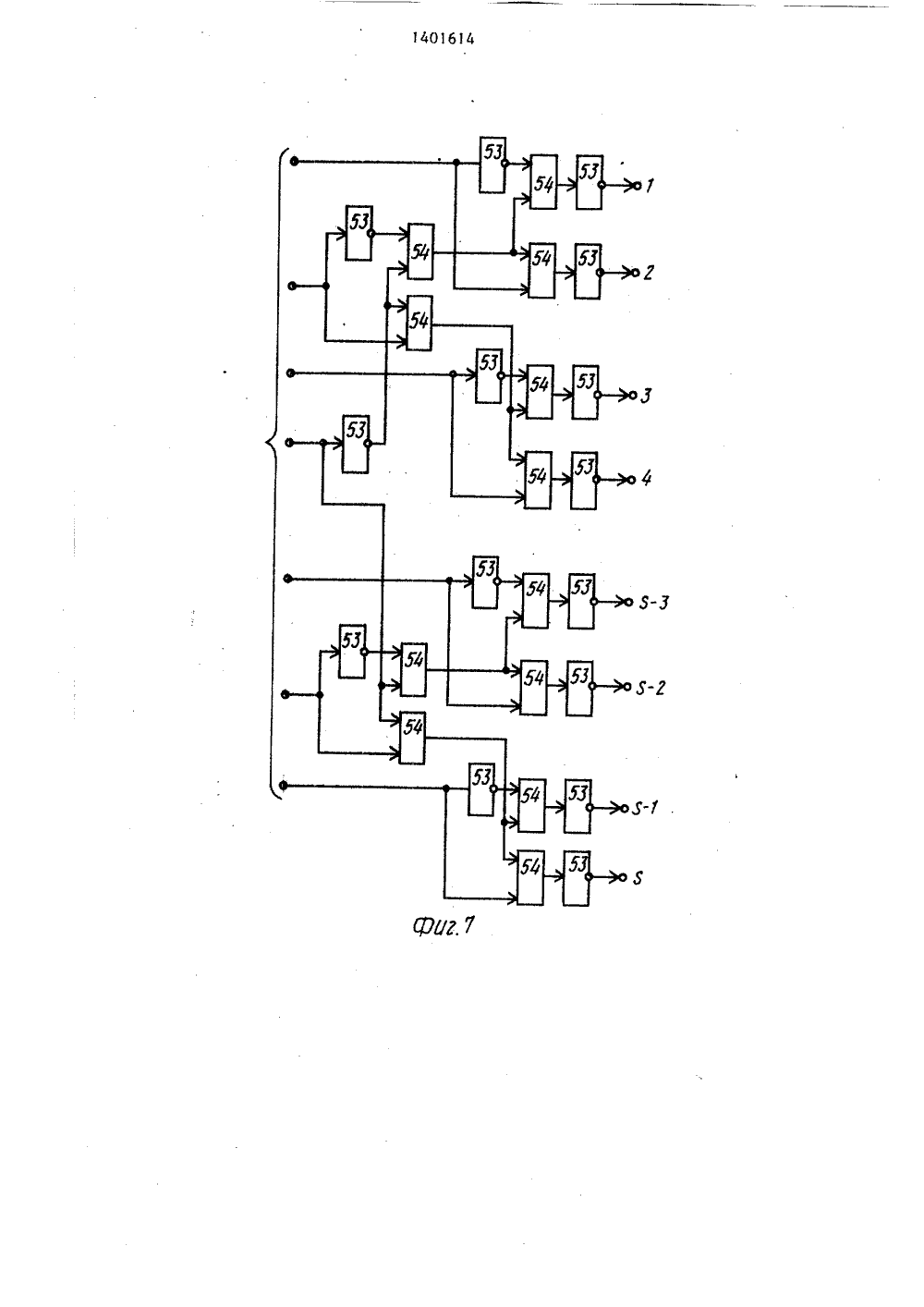

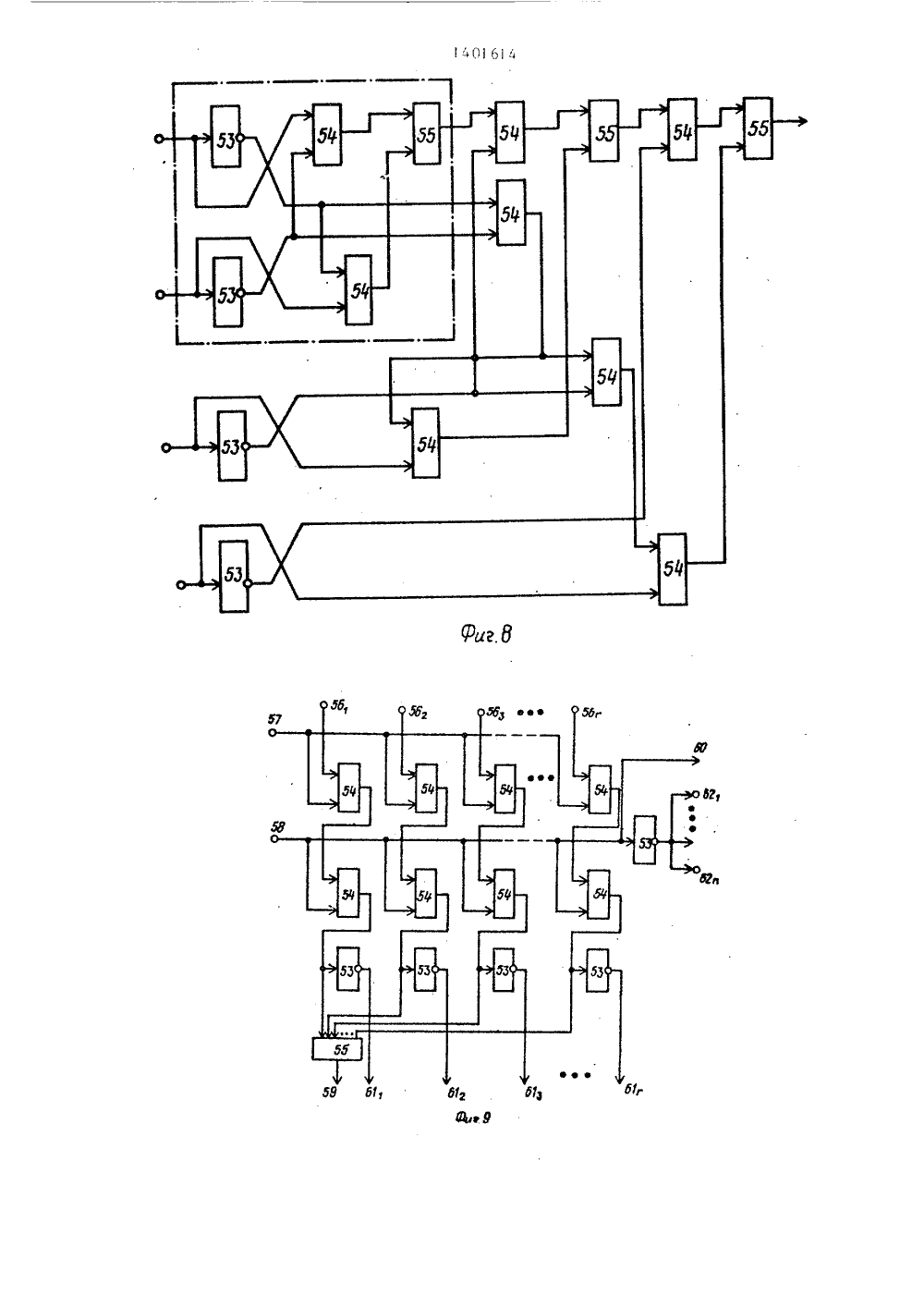

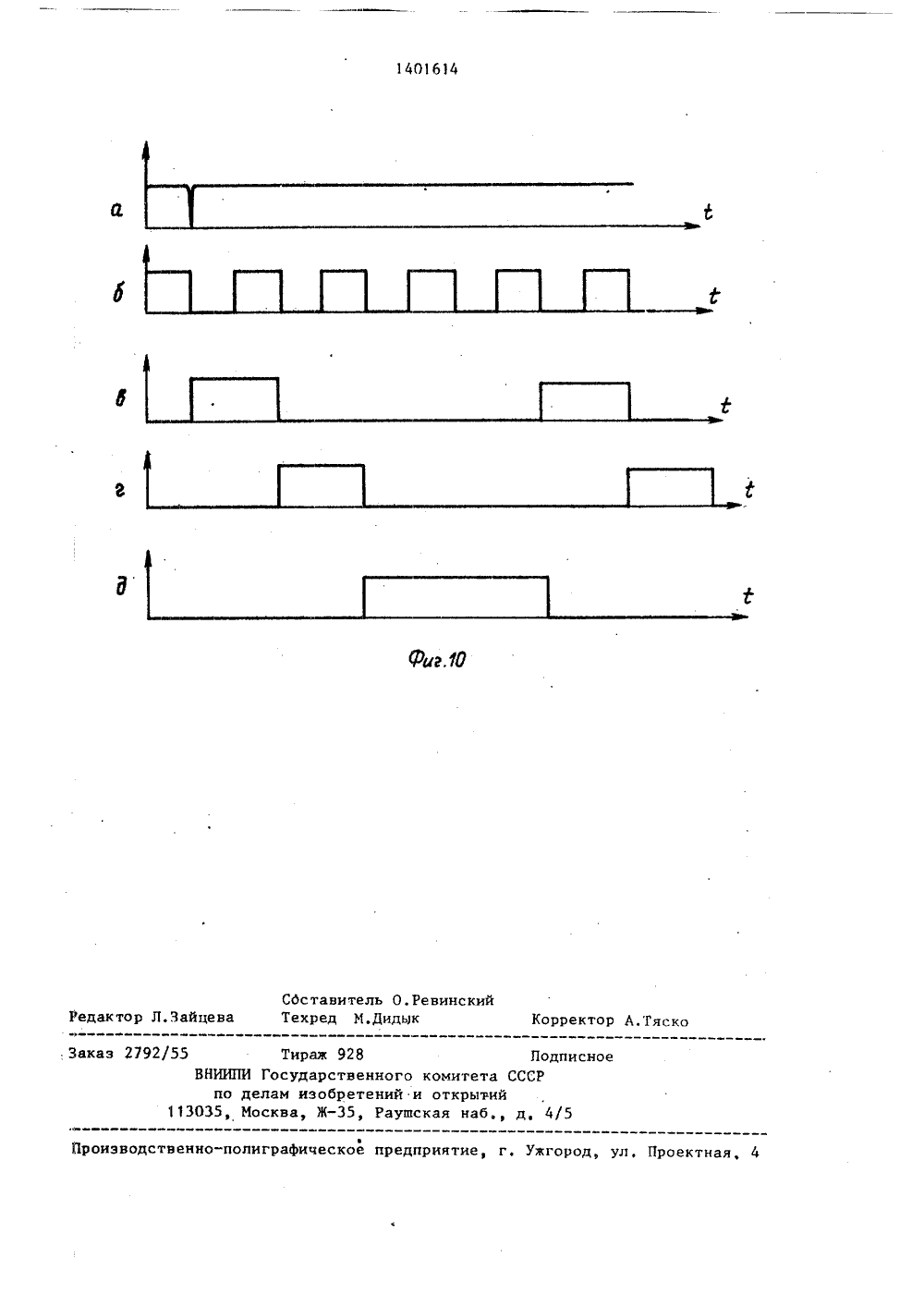

1 л Н 03 М 13/02 УДАРСТВЕННЫИ НОМИТЕТ СССРделдм изовРетений и отнята АНИЕ ИЗОБРЕТЕНИЯНОМУ СВИДЕТЕЛЬСТВУ 405/24-248,866.88. Бюл. У 21инградский злектротесвязи им, проф, М,А,ретной информа помехоустойчииии дачи дис ц позволяет гсвыситость декодера загарантированногостертых символов,кода с ортогоцалыдержит Основной ссдниговь:й регистркерцый сдв;1 гоныйлексоры 4, 5, к 1 юрации, блск 11 судва, Благодаря ввмтац 11 и, блока Оформирователя 10а .ализатора 12 при блока 13 управлОбес 11 еН 1 вается ис беспеченияения нсехОВЫй ДЕКОДЕоверками со счет о испранл Аналог 1 ЫМИ ПР в хническийБонч-Бруер(56) КолесДекодироваМ.: Связь,АнторскВ 945986,харон и А.С,Наумов4.5:681.325 (088.8)ик В.Д., Мирончикон Е.ие циклических кодов,1968, с. 103-108.е свидетельство СССРл, Н 03 М 13/02, 1981,двиговыи регистр 1,2 цадежностей, маррегистр 3, мультип 6, блок 7 дегдифмматоров ПО модулю е 1 ецию блока 8 комвыделеция максимума, импульсов стирания, Оверочцых уравнений ения в декодере правление ис стср 1401614Производственно-полиграфическое предприятие, г. Ужгор Проектна Редактор Л.Зайцеваи.Заказ 2792/55 ВНИИПИ по 035, Тираж 928Государственнолам изобретенисква, Ж, Ра Подпимитета СССРткрычийя наб д, 4/53 1;Г СТР.И Еер)ки; для- б ИТ"ОБ 1 130 брРте циР О т 1 Осится к 13113( Гц тельной ;ехнике и минет бьТхсполь ЗОБЯ 30 Б СЦС:ТЕЬЯХ ГЕРРДЗ 15 Пи КУЕТ . НОЙ 5 НфорМЯ"ииЦе.ь изобретения - о Б,1 Р;и) Г име" ХОуст)ТЕЧВИГ"И;РКИДРрЯ Тй (ЕРс Обс/- печения й )яцтривйц)оги цпрйвпГ ия всех стергых символов,Нй фиг, . изображе 1 й б.(с.г; - г );( ма ацялоговои декодера коде . ОгтиггНЯЛЬцЫМИ ПроЕрКяМИ) ца . 2 - с) фУТКТ.,ИИЕЯС ЦЬ:Г ГХР ГЬ (/ВГТСТБРП - НИ ПодбЛОКЯ и 6 ХГОКГ ГЕПсТГ 51 . О)О/)мирователя импульсов стиря)ця, псгцЧЕСКИ О бЛС)Ка И Г,ТЕОКЯ;ГТГБГ:С)Н,я; Сфцг . 6-9 - цри: Рры выполпс:. , итие тСтн РццО ГТт Гй Г рав Нецця . Т ЛГ К(у) ГГгиплекс г;рива 3353, у:3 т де Гифрйии,:Р- лектора чис:1 Я едини и ф( рирствйтеля сиг:Ялов утаеовки,", тй ФигО - и рс - менп к;ий р(мсГы рабс) ть б с)к/ упраитЕ(11(ЛИГЕТЫ 3 ДЕК 05 ЕР ;С К; .(:.;МЯГК М РРТ(ТгРМ ) 1 СКОГР Д;15 Емя в целим,;.Р кодер 3 пс)утгс;1КГЦЯЕ, С:С) г.;Рр)жиТ И)3)т,СД 1 ИГОНЫЙ РРГЦГТРСД 31" (131 ИГтестр 2 цйесжцс;стРЙ ЬТЯр;Р 1.1говый 1)егГ(ттр 3, Гс:.рее/:йвс О)МУ 51 ЬТИП)1 ЕК(ОРЫ .Т и 5. К(11// Б,леТтифряп 33, бт 1 эк 8 кс)мму.яг,цтЕЫПРЛРН 1351 М 3 КС СЕУ МЯ с С)ГТ/Ь:30)) тр ц/ и ь ( с) Б с т те р я ц и я бО кмйтиров пи М 07 улк) цвя, я:ализаГрое 130 "цьх уря внеций искрявл ения, 1 Я "тг . г ибО нс Не 15/1мацииццьЙ вход 1(т вход 1: цадтей) вход 16 икловий иеГрокивход 17 (.брося и ВыхОд В,Основной и кйркереьЙ Гдстиггистры 1:3 3 смеГ)т по и рй 305:д П - Д 51 ИНЯ ХОДЯСГвигОьЙ рс:Гистр 2 наде)кгоках(дим и3 и своих разрядс)в Гиде(т-разря;ег 1 б ферные региГ" лПаваЛЛЕЛЬЦИЙ ЗЯПИГИ И СгБИГЯ11 ых кодовы:. ки" Оиня 1 ий ,( Нял Блок 7 децифряции служит для определения номеров еаемеыььеих из не: скольких .Овокупностей чисел, Он содержит г подблоков г - число не гривиальных иртогэняльньгх проверок)5 каждый и. ко торьсх выпален (1(те, 2) на узлах 19 сравнения, ез/лах 2 у муцьтиплексировация и узле 21 ггеГГифраеи 53. НЯ фиг.2 обозначены входы 22 и Бьх )" ды 23 подблокя. Число Бхиетов 22 и ВЫХ)ДИВ ./, ,ЯВ 1: .ТГ. , ЦР; " " и Я1 Х.) :).;,ЕГ 1 с. ЦТЯХя(ТЕ 1 ПЕРВЫЕ - ТРРтЬИ,ЦТ Р;-; входы //" - 30, уи иа 3:я,1 т( ".: ь ), т ТТХЭ, 3 бПОКИрсКИО к г 1 с",/мсР торо" 11 т .тк С:.Х/,1(ЕЕТ Д:Я . /МЕ ЦПИ Я Цт/Я 11/ сВ Я СИМВО.Ог 3 Б ХО/. ЦОТ:ЯИ В/-; В К ВЕ ДИЕ ТТЗ ОрГИ ГИТс 1 1.:(1, -И/ТХурй 3 ситт, Он; и( Г ) ".;(;11)чеця:15 ф/., (т ибозчячвтл Теди Рвторые ицформаци;ц(ьРхсдь(фиг.5) на первом и втором триггерах45 и 46, элементе ИЛИ 47 и элементеИ 48, На фиг,5 обозначены первыйтретий выходы 49 - 51.Узел 19 сравнения и узел 20 мультиплексирования блока 7, узел дещифрации блоков 7 и 9, селектор 34 иформирователь 35 анализатора 12 выполнены (фкг.6 - 9) на элементах И(",КДОЧАЮ 1 ЦЕЕ ИЛИ 52, элементах НЕ 53,элементах И 54 к элементах ИЛИ 55.В узлах 20 мультиплексирования бло-.ка 9 необходимо выполнкть соединенгяв соответствии с пунктирным перекрестием (фиг,6). В селекторе 34(фиг.8) при увелкчении числа входовследует добавить элементы, обведенные пунктиром. На фиг. 9 обозначеныпервые, второй и третий нходы 5658, первый, второй, третьи и четвертые выходы 59-62 формирователя 35анализатора 12.Ня фиг.10 обозначены следующкесигналы: а - на входе 17 сброса, бна входе 16 цикловой синхронизации;в, г и д - на ныходах 49-51 блока 13управления,Вдесь логическому нулю соответствует высокий потенциал.На фиг.1 не показаны цепи такткронания регистров 1 - 3.Аналоговый декодер кода с ортогональными проверками работает следующим образом.ПеРеД началом Работы ДекоДРРатпосле того как н системе связи постигнута устойчивая цикловая к такто.вая синхронкзация, на вход 17 сбросяпоступает импульс, устанавливающийблок 13 управления н исходное состояние, после чего декодер начинаетдекодировать поступающую информацию.Декодирование осуществляют в тркэтапа. Первый и второй из этих этапов длится и-периодов тактовой ситхрониэации каждый, а третий - 2 п, Втечение всех этцх этапов сигналы тактовой синхронизации поступают на тактируеюе элементы (регистры 1 - 3),е управление режимом работы декогера производится при помопи блока 13управления (фиг.10). На вход 16 блока 13 поступают импульсы циклонойсинхронизации, имеющие частоту сПРдовянкя н и - раз мець 11 ую чястоты следовачия жмпу и.стактовой сихроцзации. На пером выходе 49 блока 13( т 1.ц Н тт: 1 Я, т :". О (. И ЗР:11тя тт тот 01(я тЬ -ПР 1 т 1 (1 Э 1 т Гт,. ЧРТт, 1 РХ 1 И,УЛЬСОНцик.оной (инхроциэяции устанав:ца( (РТСЯ ЛО ГИР(К 1 П 1 О т ОПК.1 ЮЧЯЮЩ 151 К выходам му.ьтипл(Рк(оров 4 и 5 их вторые ххоттЬ 1 ц размыкающий ктюч 6, Наостальных трех импульсах на первом выходе 49 блока 13 - лсгцттеская "1, подключающая к выходам мультиплексоров 4 и 5 цх первые входы и замыкающая ключ 6, Ня втором выходе 50 бло -ка 13 логическая 1 появляется ня Каждок Второ тиил.т(ЛЬСР 1 ККЛОНО 1"тт СИИХРСНИЗапт. Я ЦЯ ССтЯЛЬЦЬХ ЦЗ ЧРТЫРРХ импульсон - 0. На третьем выходе 51 блока 13 логкческая "1" поягляется ца каждом третьем и четвертом км- ПУ:1 ЬСЯХ( и "0 - Ца ПЕРВОМ И ВТОРОМ.(РРном этяпР и-битные сигца.(ытПРОПОРЦИОЦЯЛЬЯ(1 Р НЯежНОСТЯМ СЦМтоЛОВ КОдОВОй КОКбиЯ 1,Ит ПараЛЛЕЛЬНОпоступают я вход второго мультиплек.соря 5 с вход("н 15 ц загцсьнаются г,СдНКГОВОМ рЕГИС ГтОЕ 2, ОдцОНрРМЕННОсимноль 1 кодового с:оня с входа ,4проходят через му;ьтцплексор 4 и записыняктся н Ос 1 Овном сдвиговом ре 1 и с тре 1, с выходя ко то рого рез ультат декодированя предЫдущего кодового с.;овя пос 1 уяет .я выход8 дско- Рря 11 гркернь 1 й регистр 3 ча этом этапе заполняется ну;ямц благодаря разомкцугом; ключу 6. На втором и третьсм этапа; регистры 1 - 3 работаЮ, Б РЕж,1 Р 1" ЦК:,Ит.Р С.КО ГО СЦВ". (Г Я, ЧТО об Рог(ечцняетс 5 ссстояния 1(и: 1 ульткплексорон 4 и 5, я также л:(гтя 6.Нх 1 Р ттвр, - ,". г - РК тох т;тОГО ГО -тя-.я СИГ Я.1 ы С Газ р 5 д 51 гх выходов "н 1(" гового Пегс-,ра 2, номера которь;х соответствуют номерам символов, входящкх н пряные чя стц урявце 1 й Ор;огональной системы проверок, поступают на гходы блока в котором опрегелятотСЯ ЦОМРРЯ ЦЯИМРРЕ ЦЯДЕжЦЫХ СИМВО- гон. ти номера с выходов блока 7 по- СТуПЯК(Т ца т ,ЯН;тяЮтИР ВХОДЫ бт,ОКЯ 8 коммутации тто 1 ц(5 Оятеля 10 импульсон стирания, г 1 я выходах блока 8 коммутяИИ ПОЯНЛЯ:С;:. ЛЯДРКЦОСТ. ЦЯИПЕЦЦЫХ наине:РР цяде:ц,с сцмноон. Няцболь 1 ПЯЯ ЦЗ Э ТИ: 1(Р 1 тип ЦЯДРжнс С Тей, поиля Олоквь 1:ел(ция ма к сцмтмя, поступает и в (тр(т. 1 ходы 29 (1(О-м 1: - Т 1 ОНЯТРя 1т(11 т. 1 т (",1 С ( 1 ряцтя ГЕрттм(т 1 Х( "1 В ("-, ГП 01 Р г Петт 1,15, НЬ 1 г0ЗНЯЯ Си(ЗЕ)га Г;ОВ(. рг. ЧИЬГЗ, (:я г ЕП 1ЕСЛИ Эта НадЕжНОСть бо:т:,ие Зябг)Л И(й пэ найде 1 ых надежно стей то ця вьхо- даХ С)ОрМЬронятЕ.гя 10 ПОЯС 5)-СВ С ИГ .а " лы, ус танавливяозие раз рго:цсв;Ого сдвиг)Гзог О рсгигтоа, (е которьгх созпадаят ( номерами (я 1,;еццх СИЫВОПОВ, З З).-ЕВОЕ;ОС Гг 5 гнке (СЗМНОЛЫ СТИРЯ 1 Я 5, Я СО ОТЕ ТС т ВгС)Я,С РЯЗ- РЯДЬ 4 ЯР(СЕ РНО ГС) СДГИГ 01;"СОЕ ИСТР ) - В ЕДИ(ИЧЦСЕ СОСТОЯ (1 (С 1(:.РтЫЕ СИМВО 1 Ы 3 Я(З)ИК ( Г)ГПТ Ся 1,(, " ЗЧ и 11 Образом з) эцсход)ит раг О га дсз,сдеря ца 0(тазнных 1 тактах з "Ог) ",за яНя друГ,Х ЭтяЯХ бЛЯ Годаря,г. й ТЗИг) сигнала блокирс;вки пост :г)( му я Вход 32 (1)мировятслл1 ьпзч:ьсс) 3(г и не (Ьикс")уптс я,На трет:ем этап( му)н ип)се 1(оры (5 И 5 и Кгп)О НЕ МЕЗЯК)т С)ЗОС О (.О(-. тс)яция. Ня Ггсзрвом из 2 -, Гс ГОБ си на:зы ( разрядньгх выходов ярерцог СДНИОЗОГО РЕГИСТР 3 К)С ТЧП;т га ПЕРВЫЕ;ЗХДЫ а Ца (ИЗ атОРЯ2 1 КО т- ром про 1 15(дится прогзерка 2 пя)и(1 е В КажДОМ ПЗ ГРОВЕРОЧ(ЫХ УРЯВЦ(.Ццй СИСтЕМЫ С:Р"ОГОЯЗ(ЬНЬГХ ПРО;ЗС РОК ОД- ЗГ Г( С т(Р Т(г С СГМН СЯ . " ,;:., П Х СС)- л:бо урзцц(ции акое,зал чин Обцару- ЖИТС 51ТО б (я Годаря ВЫХОд И 0 ( И Г а лам аца, п(затора 1 1 ос т; зао 15 к:а вторые ус та ново чные Бхсд,. Ос цо.-ПО 1 сИ МаРКЕРПСГО С;1(ЗИГОВЫХ Р 1 .т,:ОН стертьпз симвсз(;аязрявляе г я тяк, чтобь ура 1:ение выполцяпо ь, . - . сооз . ветстнус й вяз ояд маркер с ге реист . ра 3 устава в)пива ется в ву. з;ое состояние, Если 1 е обнару)кев урявн: пиис едкцстневцым стерть 1 символо З, тс ИСПРЯЗПЕЗ 5.Е НЕ ПРОИЗВОДИТРЯ. Цаннние исправляемого символа )пределяет- СЯ ПО СООТВЕт" ТЗЗУЮгЕМУ СИ; азУ Ца НЫ- ходе блока 1, н котором Зрозз)зог(и Гс 5 , г(суммирование по мог)ул дна .им;олов, ВХОДЯЯ(ИХ В ПРОВЕРОЧЦОЕ г),ГЗ.ЗЕнгЕ ОР 01 ОИЖ 1 ЬИОЙ СИС 1 МЫ о уха 11 Яцгяе Про"ВЕРКИ И ИС ПРаН;:ЕНИЯ ПРОИЗВОДЯ,(.Я И Ца втором так Ге, гричем Зикпчсски г;д сдвиг содержимого регистров- 3 це ПрОИЗВОдИТСя, дна)10 КЧИ ОоргЗО:"происходит работа ца ос ЯГььх ": ктах этого этапа, На других атагах5 благодаря действия) сигнал блоккровКИ, ПОСТУПКЕГО На вход с(2 анализатора 12 с третьего выхода )1 бгока 13 уп 1)явления, ис:ц)явления символо: не цроизвэпятся,я.Н =- Е , .);1";,Д Р Я 1 ( З((; ;И 1.1 5: Г:1 1" ; 1ГгЦ О ЕРОЧ ЯЯ а" ;",волов. Очевидно, что на третьем этапе работы декодера все стертые симво. лы будут исправлены.5Формула изобретения1. Аналоговый декодер кода с ортогональными проверками, содержащий первый мультиплексор, первый информа О ционный вход которого является информационным входом декодера, выход первого мультиплексора соединен с информационным входом основного сдвигового регистра, параллельные выходы которого соединены с соответствующими вхо,дами блока сумматоров по модулю два, ,маркерный сдвиговый регистр, последо,вательный выход которого соединен с информационным входом ключа, выход которого подключен к информационному входу маркерного сдвигового регистра, второй мультиплексор, первые информационные входы которого являются входами. надежностей декодера, выходы 25 второго мультиплексора соединены с информационными входами сдвигового регистра надежности, параллельные выходы которого подключены к одноименным входам блока дешифрации, последовательные выходы сдвигового регистра надежностей подключены к вторым информационным входам второго мультиплексора, последовательный выход основного сдвигового регистра подключен к второму информационному входу первого мультиплексора и является выходом декодера, о т л и ч а ю щ и й - с я тем, что, с целью повышения помехоустойчивости декодера за счет исправления всех стертых символов, в декодер введены блок коммутации, блок выделения максимума, формирователь импульсов стирания, анализатор проверочных уравнений и блок управления, первый и второй входы которого явля 45 ются соответственно входом цикловой синхронизации и входом сброса декодера, первый выход блока управления подключен к управляющим входам первого и второго мультиплексоров и ключа, 5 О второй и третий выходы блока управления соединены с входами блокировки соответственно формирователя импульсов стирания и анализатора провероч-, ных уравнений, информационные входы 55 блока коммутации подключены к соответствующим параллельным выходам сдвигового регистра надежностей, выходы блока дешифрации подключены куправляющим входам формирователя импульсов стирания и блока коммутации,первые выходы которого соединены спервым инйормационными входами формирователя импульсов стирания,вторые выходы блока коммутации подключены к входам блока выделения максимума, первые и вторые выходы которого соединены соответственно с вторыми и третьими информационными входами Формирователя импульсов стирания, выходы которого подключены кпервым установочным входам основногои маркерного сдвиговых регистров, выходы разрядов маркерного сдвиговогорегистра и выходы блока сумматоровпо модулю два Подключены соответственно к перв 1 лм и вторым информационным входам анализатора проверочныхуравнений, первый и вторые выходы ко"торого подключены к вторым установоч.ным входам соответственно основногои маркерного сдвиговых регистров. 2. Аналоговый декодер по п.1,о тличающийся тем, чтоанализатор проверочных уравнений выполнен на селекторах числа единиц,формирователях сигналов установки,узлах переключения и элементах ИЛИ,первые входы формирователей сигналовустановки объединены с соответствующими входами одноименных селекторовчисла единиц и являются соответствующими первыми информационными входамиблока, вторые входы формирователейсигналов установки являются соответствующими вторыми информационнымивходами блока, выход каждого селектора числа единиц соединен с третьимвходом одноименного формирователясигналов установки, первый и второйвыходы которого подключены к соответствующим входам соответственно первого и второго элементов ИПИ, выходыкоторых соединены с управляющими входами одноименных узлов переключения,входы блокировки которых объединеныи являются входом блокировки блока,третьи и четвертые выходы каждогоформирователя сигналов установки соединены с соответствующими информационными входами соответственно первого и второго узлов переключения,выходы которых являются соответственно первыми и вторыми вых, дамиблока, 14016143. Аналоговый декодер по п,1,о т л и ч а ю щ и й с я тем; чтоблок дешифрации выполнен на г однотипных подблоках (г - число нетривиальных ортогональных проверок кода),каждый иэ которых включает в себяузлы сравнения, узлы мультиплексирования и узел дешифрации, первые и1 О вторые входы первого - ( в -)-го уз 2 лов сравнения, Я - число невоторяющихся символов в проверочном уравнении кода, объединены с соответствующими информационными входами одно 15 именных узлов мультиплексирования и являются соответственно первыми Б-ми входами подблока, соответствующие входы подблоков объединены и являются входами блока, выходы (21.-1)-го и (2)-го узлов мультиплексированияБ(1 6) соединены соответственно2Б с первыми и вторыми входами ( +2 25 + 1)-го узла сравнения, выходы (21- -1) -го и (21)-го узлов мультиплексисс МФ рования (Я .Е. 2 ((Я .с. 2(Я и 2 + )-го узла сравнения, выМ:ход каждого узла сравнения кроме по 35 следнего подключен к управляющему входу одноименного узла мультиплексирования и соответствующему входу узла дешифрации, выход последнего узла сравнения соединен с соответствую щим входом узла дешифрации, выходы узлов децифрации всех подблоков являются выходами блока. 4. Аналоговый декодер по п,1,отличающийся тем, что 45 блок выделения максимума выполнен на узлах сравнения, узлах мультиплексирования и узле дешифрации, первые иБвторые входы первого - (- - )-го уз2лов сравнения объединены с соответствующими информационными входами одноименных узлов мультиплексирования и являются соответственно первыми Я-ми входами блока, выходы (21.-1)-го и (2)-го узлов мультиплексированияБ(16 - -) соединены соответственно2 ф Б с первыми и вторыми входами ( +2 + д)-го узла сравнения выходы (21-1) - го и (2)-го узлов мультиплексировам+иии сй Й 2 с 1 с 22,2 сисивс 2)М:3 сисоединены соответственно с первыми и вторыми информационными входами (Б ф 2 + )-го узла сравнения, выГ - 11иходы (Б)-го узла мультиплексирования являются первыми выходми блока, выходы первого - (Б)-го узлов сравнения подключены к управляющим входам одноименных узлов мультиплексирования и соответствующим входам узла дешифрации, выходы которого являются вторыми выходами блока.5, Аналоговый декодер по п,1, о т л и ч а ю щ и й с я тем, что формирователь импульсов стирания выполнен на элементах И, элементах ИНЕ, элементе НЕ и узле сравнения, первые и вторые входы которого являются одноименными информационными входами Формирователя, выход узла сравнения соединен с первым входом первого элемента И и через элемент НЕ - с первыми входами всех элементов И-НЕ, вторые входы которых являются третьими информационными входами формирователя, выходы первого (Я - 1)-го элементов И-НЕ подключены к первым входам соответственно второго Б-го элементов И, вторые входы всех элементов И объединены и являются входом блокировки формирователя, третьи входы первого - (Б)-го элементов И-НЕ объединены с третьими входами соответственно второго - Я-го элементов И и являются управляющими входами формирователя, выходы элементов И являются выходами формирователя. 6. налоговый декодер по и.1, о т л и ч а ю щ и й с я тем, что блок управления выполнен на триггерах элементе И и элементе ИЛИ, счетный вход первого триггера является первым входом блока, входы обнуления первого и второго триггеров объединены и являются вторым входом блока, прямой выход первого триггера подключен к счетному входу второго триггера и первым входам элемента ИЛИ и элемента И, выходы которых являются соответственно первым и вторым выхо1401614 12 11 дами блока, инверсный выход второготриггера соединен с вторым входомэлемента И, прямой выход второго Ф О триггера подключен к второму входуэлемента ИЛИ и является третьим выходом блока.

СмотретьЗаявка

4100505, 07.08.1986

ЛЕНИНГРАДСКИЙ ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ СВЯЗИ ИМ. ПРОФ. М. А. БОНЧ-БРУЕВИЧА

ЗАХАРОВ АРИАН АРИАНОВИЧ, НАУМОВ АНАТОЛИЙ СЕРГЕЕВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: аналоговый, декодер, кода, ортогональными, проверками

Опубликовано: 07.06.1988

Код ссылки

<a href="https://patents.su/12-1401614-analogovyjj-dekoder-koda-s-ortogonalnymi-proverkami.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый декодер кода с ортогональными проверками</a>

Предыдущий патент: Кодек блочных кодов

Следующий патент: Устройство для распознавания импульсных сигналов с внутриимпульсной модуляцией

Случайный патент: Способ очистки воды от органических примесей