Логический процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

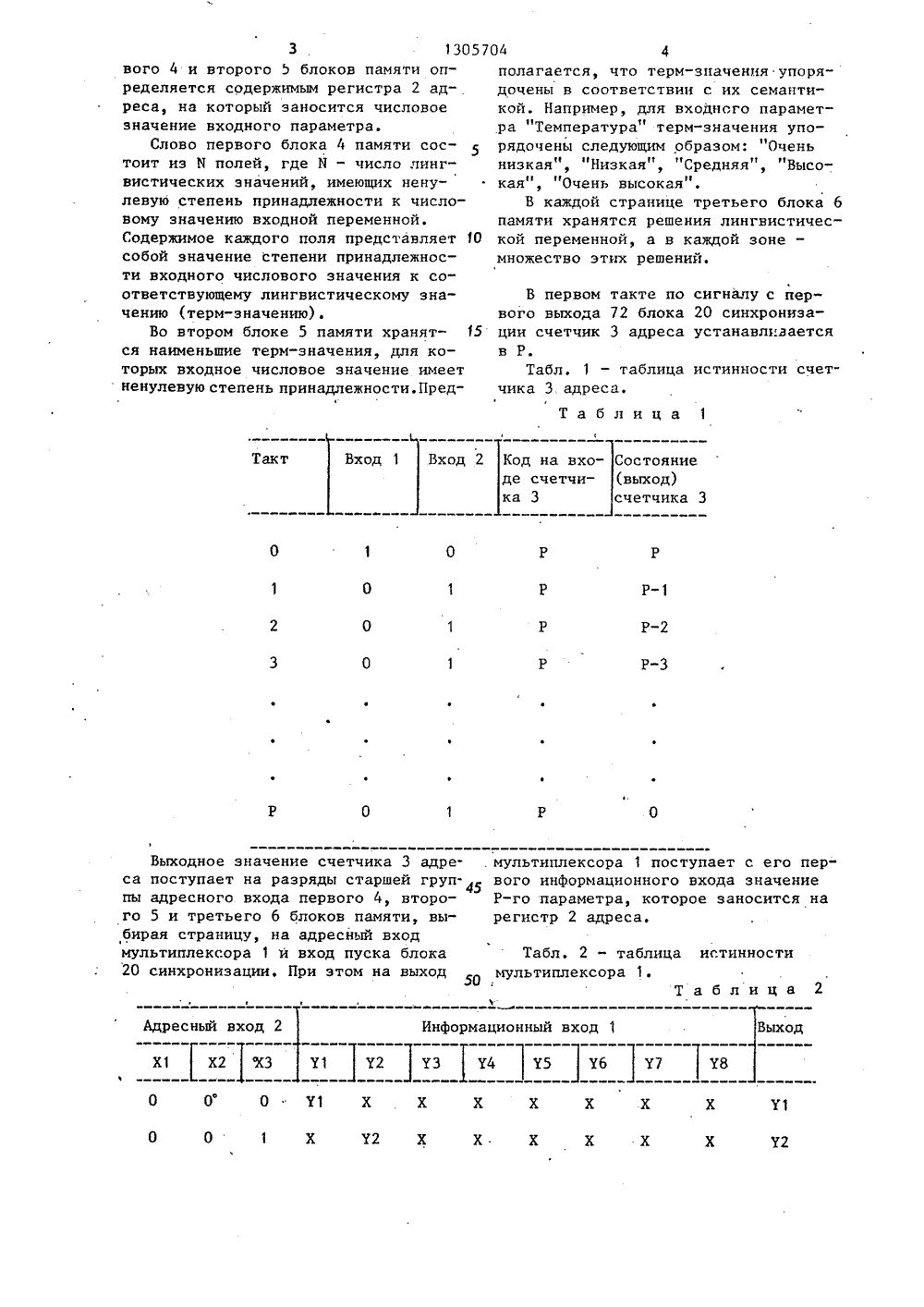

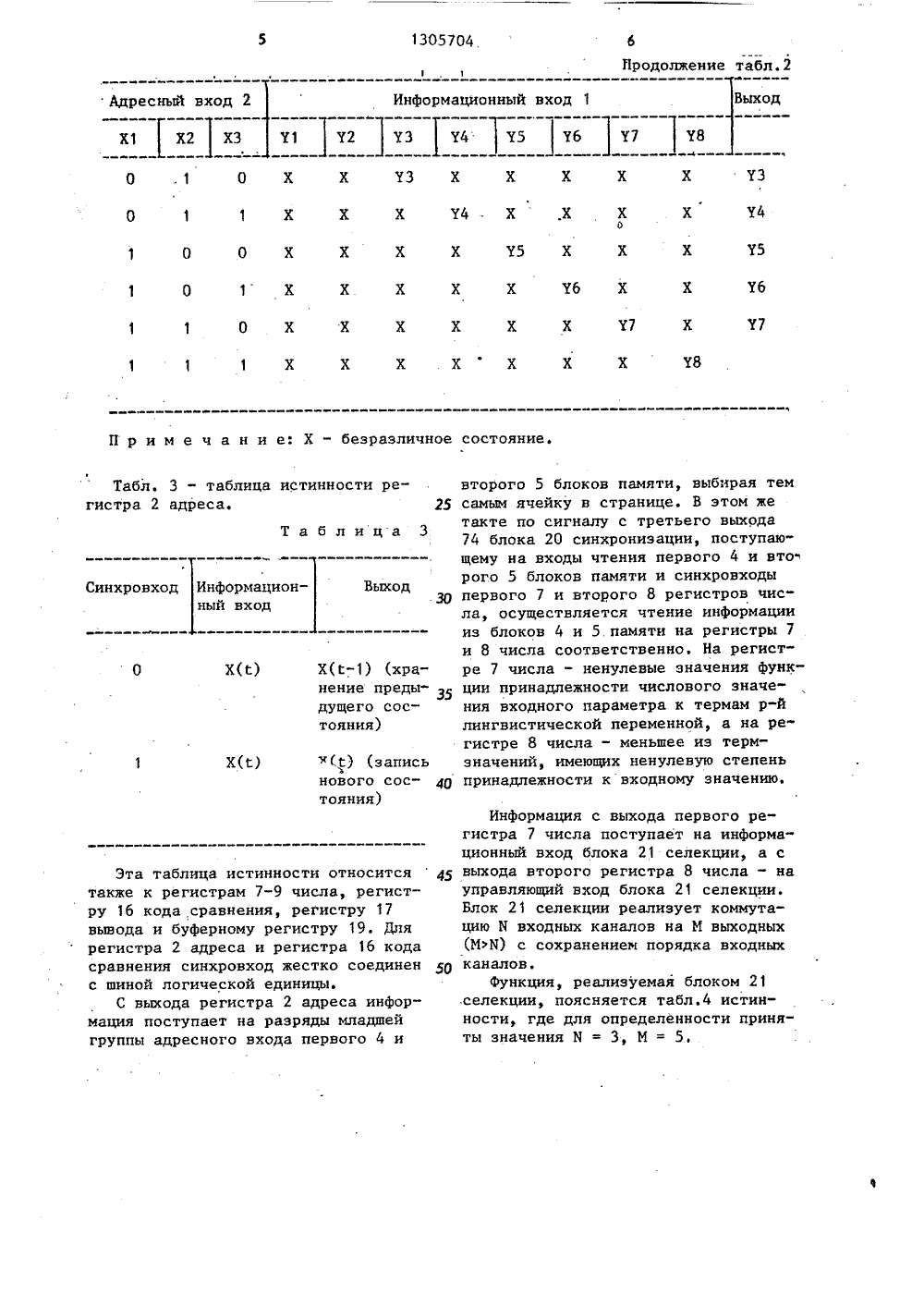

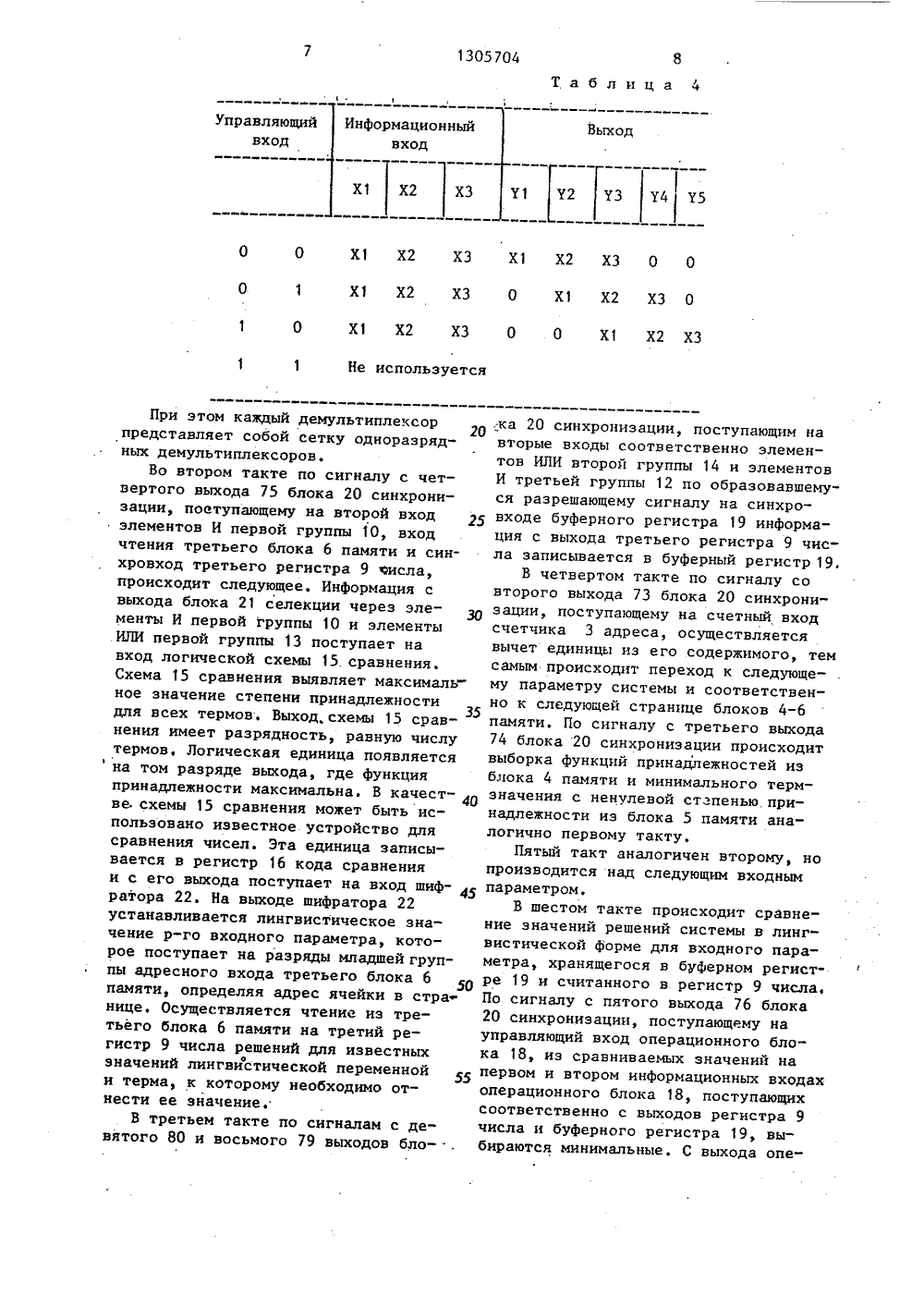

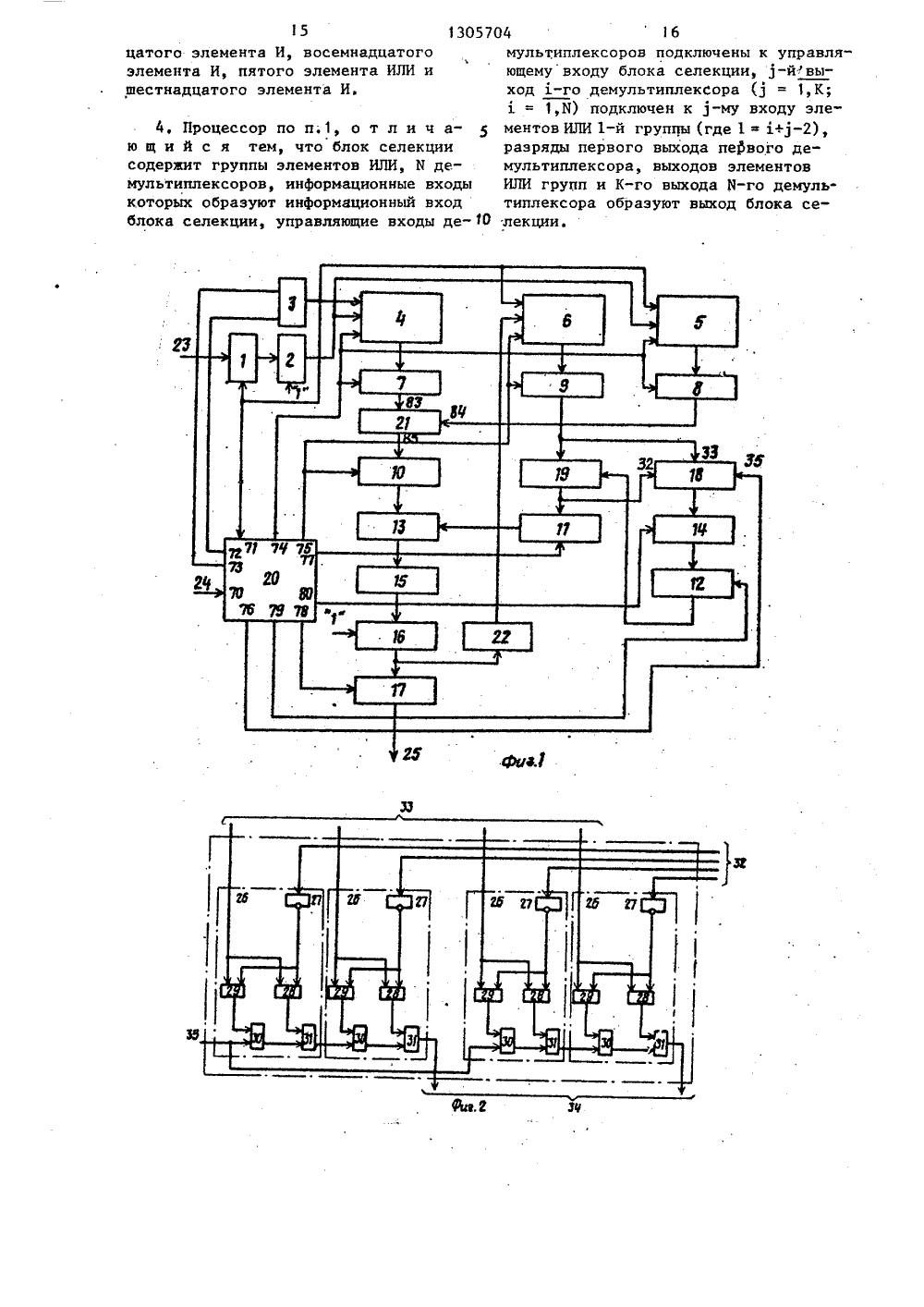

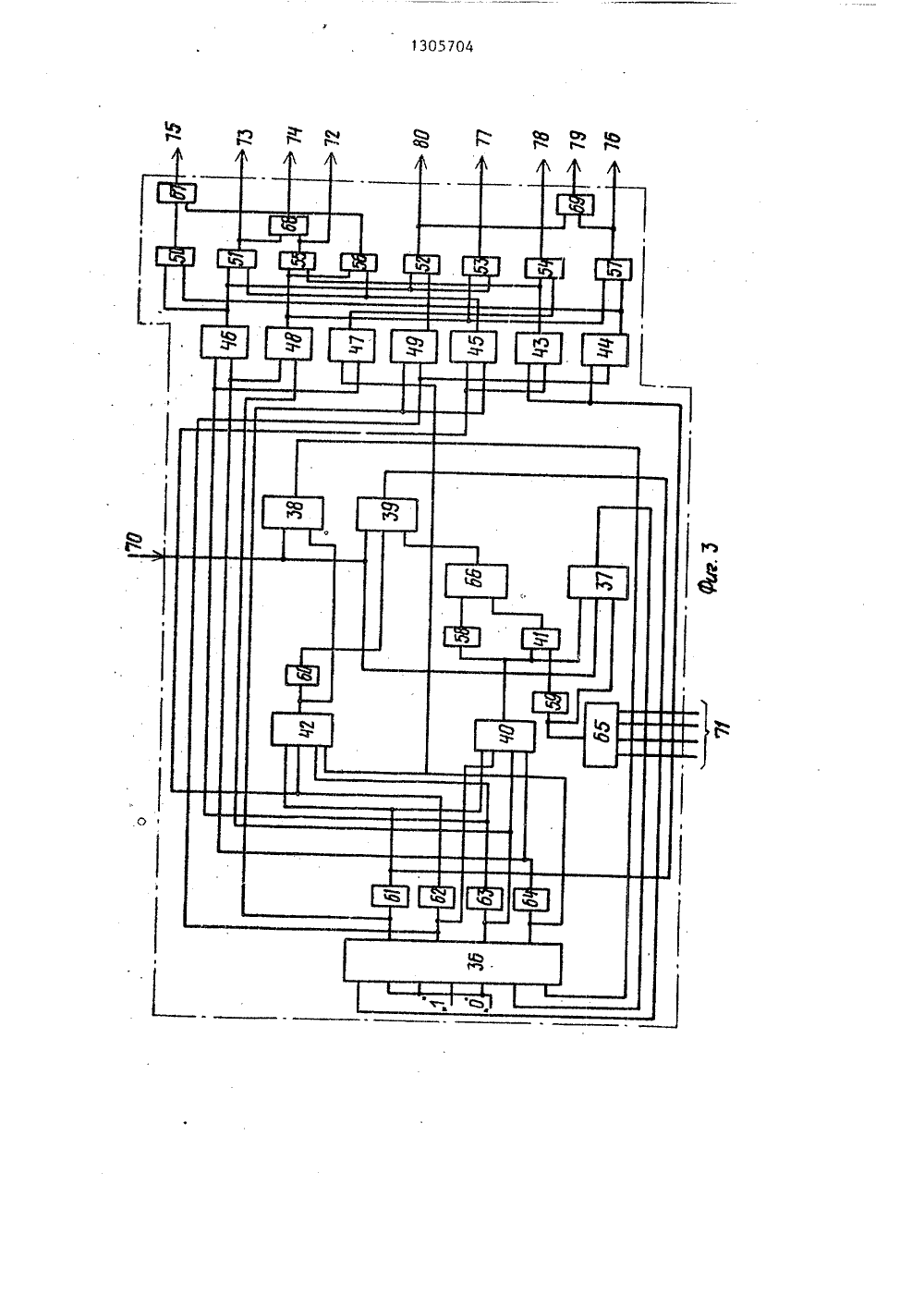

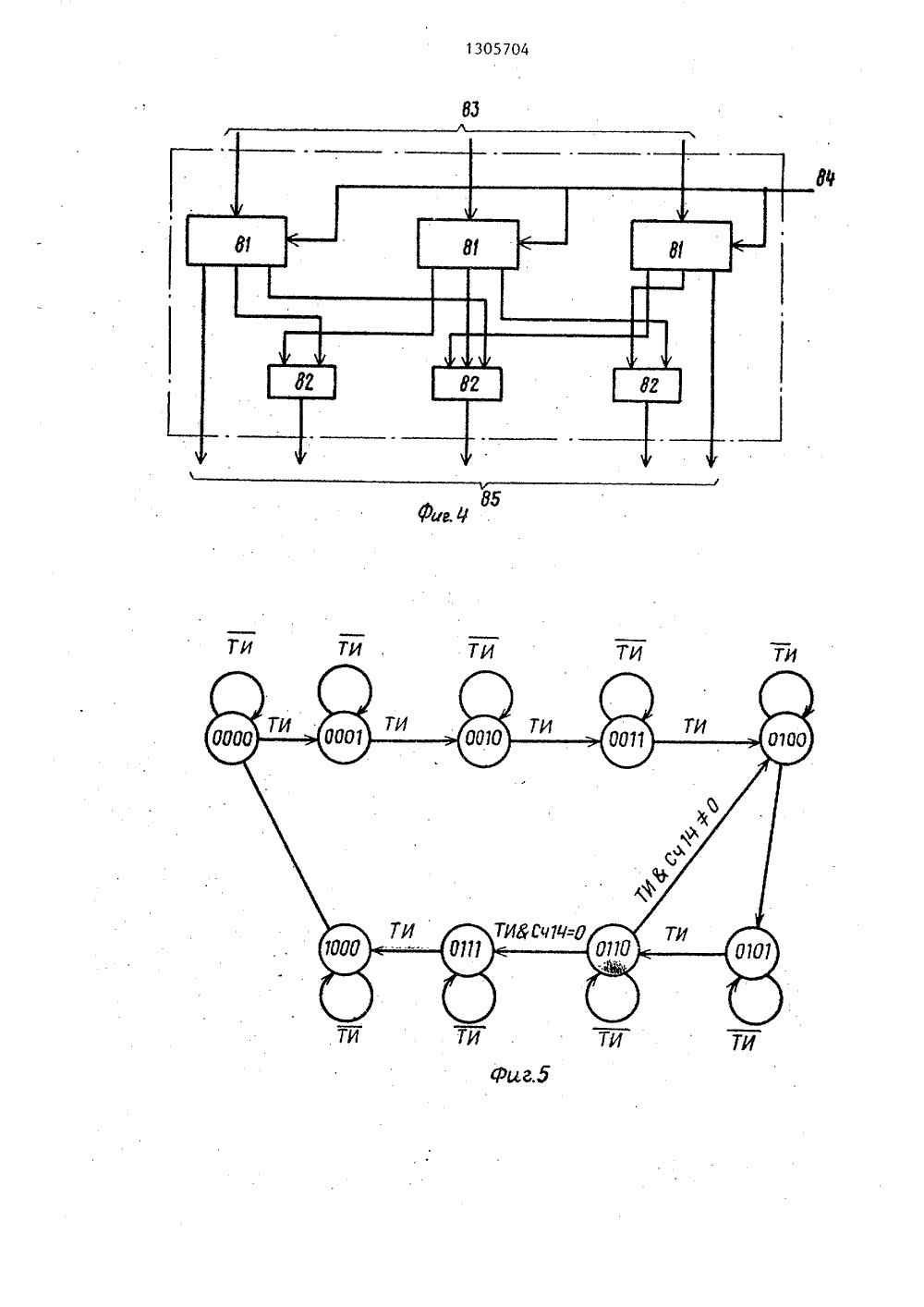

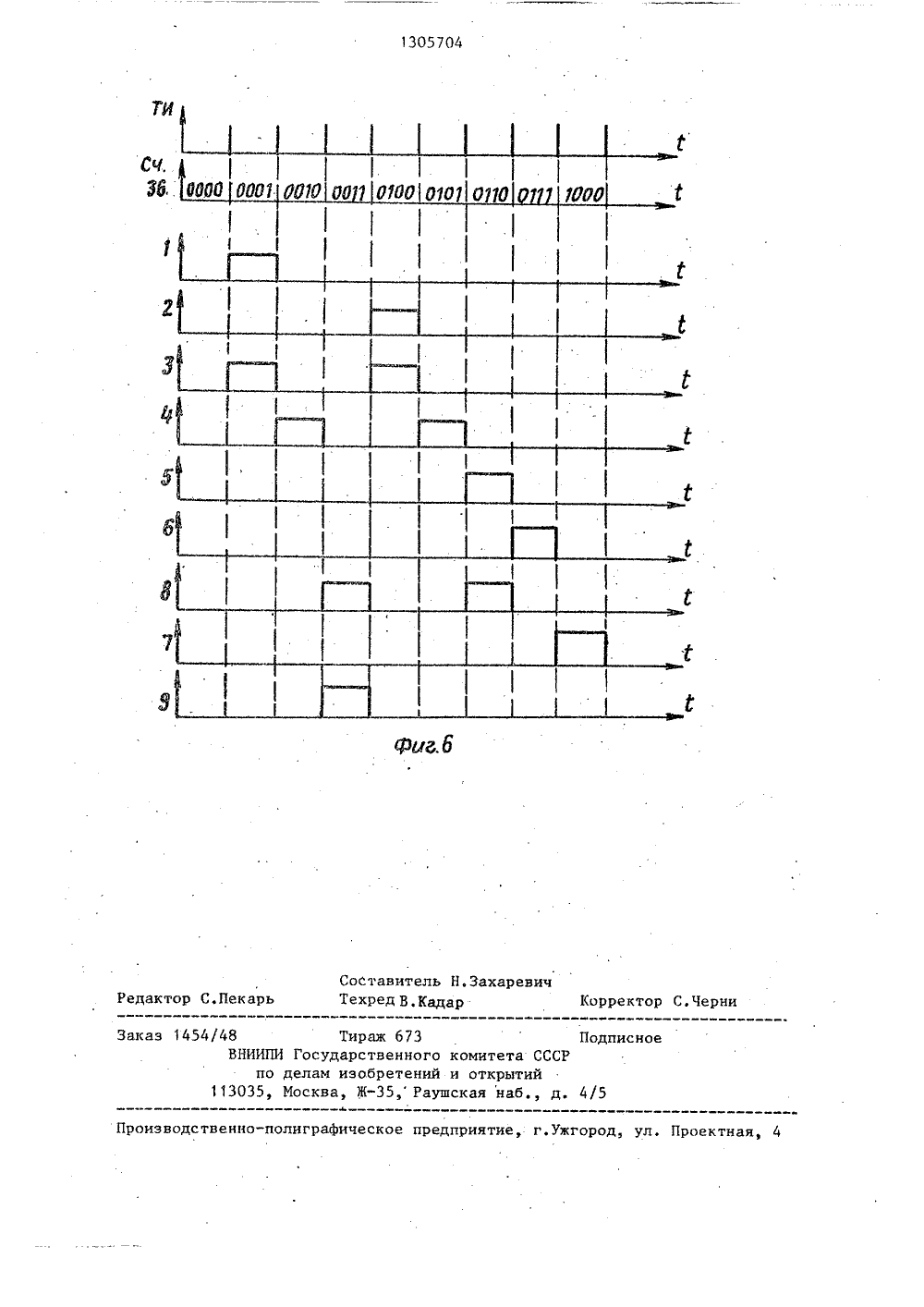

ЕЛЬСТВУ ВИДЕ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИИ(56) Авторское свидетельство СССР У 843592, кл. С 06 Р 15/20, 1981.Балашов Е,П. и др. Многофункциональные регулярные вычислительные структуры, - М.: Сов.радио, 1978.Авторское свидетельство СССР У 1108450, кл. С 06 Р 15/20, 1984.(57). Изобретение относится к вычислительной технике и может быть использовано в многопараметрических системах управления, для которых точная математическая модель функционирова" ния объекта управления неизвестна. Цель изобретения - сокращение аппаратных затрат путем снижения требуемой емкости памяти, С этой целью логический процессор содержит блок селекции и шифратор, с помощью которых осуществляются выявление максимального значения степени принадлежности входных параметров эталонному множеству и в дальнейшем шифрование а этого значения в код номера решения, . ф являющийся результатом работы процессора. 3 з.п. Ф-лы,6 ил. 4 табл.1305704 Составитель Н.Захаревичактор С.Пекарь Техред В, Кадар рректор С.Черн каз 14 дписное Производственно-полиграФическое предприятие, г.ужгород, ул. Проектна 4/48 Тираж 673 ВНИИПИ Государственног по делам изобретении 113035, Москва, Ж, Ракомитета и открыт ская наб СРд. 4/504 Использование вновь введенных блока селекции, шифратора и новых свя зей в сочетании со страничной организацией второго блока памяти, где в каждой ячейке хранятся имеющие из терм-значений, имеющих ненулевую степень принадлежности к входному значению, позволяет исключить хранение ненулевых степеней принадлежности, что , приводит к сокращению аппаратурных затрат. 1 , 13057Изобретение относится к цифровойвычислительной технике и может бытьиспользовано для классификации ситуаций в многопараметрических системах,для которых точная математическая модель функционирования объекта управления неизвестна.Целью изобретения является сокращение аппаратурных затрат путем сокращения требуемого объема памяти. 10В системах, неотъемлемым звеномкоторых является человек, оценивающийинформацию и принимающий решение, логический алгоритм управления задается в лингвистической форме. Например,если на вход системы поступают параметры объекта " интервалы временимежду сбоями в блоках некоторой системы, то на входе формируются термзначения лингвистической переменной"Редко", "Часто" и т.п.Логический алгоритм в лингвистической форме задается в этом случаеследующим образом. "если блок Б 1 сбоит часто, то, если блок Б 2 сбоит,очень редко, то, то заменитьблок Б 1".Для преобразования значения входного параметра в лингвистическую форму в известном устройстве необходимохранить степени принадлежности входного значения ко всем лингвистическимзначениям. Однако входное значениеимеет ненулевую степень принадлежности лишь к некоторым лингвистическимзначениям. Например, для интервалавремени 2,5 ч принадлежность к лингвистическим значениям может задаваться следующим образом: 0,4/"Очень ред"Часто", О/"Очень часто",Хранение всех, в том числе и нулевых, степеней принадлежности обус.лавливает большой объем требуемой памяти и приводит к значительным аппаратурным затратам в целом. На фиг.1 представлена структурнаясхема логического процессора; нафиг.2-4 - функциональные схемы операционного блока, блока синхронизации и блока селекции соответственно;на фиг,5 и 6 - диаграмма переходовсчетчика блока синхронизации и временная диаграмма логического процессора соответственно.Логический процессор содержит мультиплексор 1, регистр 2 адреса, счетчик 3 адреса, три блока 4-6 памяти,три регистра 7-9 числа, три группы10-12 элементов И, две группы 13 и 14элементов ИЛИ, логическую схему 15сравнения, регистр 16 кода сравнения,регистр 17 вывода, операционный блок18, буферный регистр 19, блок 20 синхронизации, блок 21 селекции и шифратор 22.Логический процессор имеет информационный вход 23, тактовый вход 24и выход 25 номера решения.Операционный блок 18 содержит Ргрупп по И операционных узлов 26, каждый из которых содержит элемент НЕ 27,входные элементы И 28 и ИЛИ 29 и выходные элементы И 30 и ИЛИ 31.Операционный блок 18 имеет первый32 и второй 33 информационные входы,информационный 34 выход и стробирующий 35 вход.Блок 20 синхронизации содержитсчетчик 36, двадцать один элемент)И 37-57, семь элементов НЕ 58-64 ипять элементов ИЛИ 65-69.Блок 20 синхронизации имеет тактовый вход 70,вход 71 пуска, выходы72-80 с первого по девятый,Блок 21 селекции содержит демультиплексоры 81 и группы 82 элементовИЛИ,Блок 21 селекции имеет информационный вход 83, управляющий вход 84 ивыход 85.Логический процессор работает следующим образом.Первый 4, второй 5 и третий 6 блоки памяти имеют страничную организацию. Для страничной организации блоков памяти их адресный вход условноразбит на две группы: старшие разряды адреса определяют ячейку в странице. Номер страницы первого 4, второго 5 и третьего 6 блоков памяти определяется содержимым счетчика 3 адреса, т.е. номером входного параметра, Номер ячейки в странице для перВход 1 Вход 2 Код на вхо- Состояниеде счетчи- (выход)ка 3 счетчика 3 Такт О О О РО РО Выходное значение счетчика 3 адреса поступает на разряды старшей груп.45 пы адресного входа первого 4, второго 5 и третьего 6 блоков памяти, выбирая страницу, на адресный вход мультиплексора 1 и вход пуска блока 20 синхронизации. При этом на выход мультиплексора 1 поступает с его пер"вого информационного входа значениеР-го параметра, которое заносится нарегистр 2 адреса. Табл. 2 - таблица истинностимультиплексора 1. Таблица 2 Информационный вход 1 УЗ У 4 75 76 У 7 ыход Адресный вход 2Х 1 Х 2 ХЗ 71 72 78 О О О " 71 Х Х Х Х Х Х О О 1 Х 72 Х Х Х Х Х Х 3 1305704 4 вого 4 и второго 5 блоков памяти оп- полагается, что терм-значения упоряределяется содержимым регистра 2 ад- дочены в соответствии с их семантиреса, на который заносится числовое кой. Например, для входного параметэначение входного параметра. ра Температура" терм-значения упоСлово первого блока 4 памяти сос рядочены следующим образом: "Очень тоит из И полей, где Б - число линг- низкая", "Низкая", "Средняя", "Высовистических значений, имеющих нену- кая", "Очень высокая". левую степень принадлежности к число- В каждой странице третьего блока 6 вому значению входной переменной. памяти хранятся решения лингвистичесСодержимое каждого поля представляет 10 кой переменной, а в каждой зоне - собой значение степени принадлежнос- множество этих решений. ти входного числового значения к соответствующему лингвистическому зна- В первом такте по сигналу с перчению (терм-значению). вого выхода 72 блока 20 синхронизаВо втором блоке 5 памяти хранят ции счетчик 3 адреса устанавлизается ся наименьшие терм-значения, для ко- в Р.торых входное числовое значение имеет Табл. 1 - таблица истинности счет- ненулевую степень принадлежности, Пред- чика 3 адреса.Таблица 1Выход Ъ. 78 0,1 0 Х Х УЗ Х Х Х Х О 1 1 Х Х Х У 4- Х.Х Х 1 0 0 Х Х Х Х У 5 Х Х 1 0 1 Х Х Х Х Х 76 Х Х Х 17 Х 0 Х Х Х Х Х 1 Х Х Х ХХ Х Х 78 П р и м е ч а н и е: Х - безразличное состояние. Таблица 3 Синхровход Информационный вход Выход Х(с) Х(с) (хранение предыдущего состояния) 0(записьнового состояния) Табл. 3 " таблица истинности ре"гистра. 2 адреса. Эта таблица истинности относится также к регистрам 7-9 числа, регист" ру 1 б кода сравнения, регистру 17 вывода и буферному регистру 19. Для регистра 2 адреса и регистра 1 б кода сравнения синхровход жестко соединен с шиной логической единицы.С выхода регистра 2 адреса информация поступает на разряды младшей группы адресного входа первого 4 и второго 5 блоков памяти, выбирая тем 25 самым ячейку в странице. В этом жетакте по сигналу с третьего выхода 74 блока 20 синхронизации, поступаю" щему на входы чтения первого 4 и вто рого 5 блоков памяти и синхровходы .30 первого 7 и второго 8 регистров числа, осуществляется чтение информации из блоков 4 и 5.памяти на регистры 7 и 8 числа соответственно. На регистре 7 числа - ненулевые значения функ ции принадлежности числового значения входного параметра к термам р-Й лингвистической переменной, а на регистре 8 числа - меньшее иэ терм- значений, имеющих ненулевую степень ,1 О принадлежности к входному значению. Информация с выхода первого регистра 7 числа поступает на информационный вход блока 21 селекции, а с А 5 выхода второго регистра 8 числа - науправляющий вход блока 21 селекции.Блок 21 селекции реализует коммутацию Б входных каналов на М выходных(МИ) с сохранением порядка входных 50 каналовФункция, реализуемая блоком 21селекции, поясняется табл.4 истинности, где для определенности приняты значения И = 3, М = 5,Х 1 Х 2 ХЗ У 72 УЗ У 4 75 О 0 Х Х 2 ХЗ Х 1 Х 2 ХЗ 0 0 0 1 Х 1 Х 2 ХЗ 0 Х Х 2 ХЗ О 1 0 Х 1 Х 2 ХЗ 0 0 Х 1 Х 2 ХЗ 1 Не используется При этом каждый демультиплексор представляет собой сетку одноразрядных демультиплексоров.Во втором такте по сигналу с четвертого выхода 75 блока 20 синхронизации, поатупающему на второй вход элементов И первой группы 10, вход чтения третьего блока 6 памяти и синхровход третьего регистра 9 висла, происходит следующее. Информация с выхода блока 21 селекции через эле менты И первой группы 10 и элементы ИЛИ первой группы 13 поступает на вход логической схемы 15. сравнения. Схема 15 сравнения выявляет максимальное значение степени принадлежности для всех термов. Выход. схемы 15 срав 35 нения имеет разрядность, равную числу термов. Логическая единица появляетсяна том разряде выхода, где функция принадлежности максимальна. В качест ве, схемы 15 сравнения может быть использовано известное устройство для сравнения чисел. Эта единица записывается в регистр 16 кода сравнения и с его выхода поступает на вход шиф ратора 22. На выходе шифратора 22 устанавливается лингвистическое значение р-го входного параметра, которое поступает на разряды младшей группы адресного входа третьего блока 6 памяти, определяя адрес ячейки в стра нице. Осуществляется чтение из третьего блока 6 памяти на третий регистр 9 числа решений для известных значений лингвистической переменной и терма, к которому необходимо отнести ее значение.В третьем такте по сигналам с девятого 80 и восьмого 79 выходов бло- ,ка 20 синхронизации, поступающим навторые входы соответственно элементов ИЛИ второй группы 14 и элементовИ третьей группы 12 по образовавшемуся разрешающему сигналу на синхровходе буферного регистра 19 информация с выхода третьего регистра 9 числа записывается в буферный регистр 19.В четвертом такте по сигналу совторого выхода 73 блока 20 синхронизации, поступающему на счетный входсчетчика 3 адреса, осуществляетсявычет единицы из его содержимого, темсамым происходит переход к следующему параметру системы и соответственно к следующей странице блоков 4-6памяти, По сигналу с третьего выхода74 блока 20 синхронизации происходитвыборка функций принадлежностей изблока 4 памяти и минимального термзначения с ненулевой стпенью принадлежности из блока 5 памяти аналогично первому такту.Пятый такт аналогичен второму, нопроизводится над следующим входнымпараметром,В шестом такте происходит сравнение значений решений системы в лингвистической форме для входного параметра, хранящегося в буферном регистре 19 и считанного в регистр 9 числа,По сигналу с пятого выхода 76 блока20 синхронизации, поступающему науправляющий вход операционного блока 18, из сравниваемых значений напервом и втором информационных входахоперационного блока 18, поступающихсоответственно с выходов регистра 9числа и буферного регистра 19, выбираются минимальные, С выхода опеРК= , 1Р 1о 55 Ч, КМ 1 (бит),9 , 13057рационного блока 18 единичные значения, соответствующие минимальным решениям через элементы ИЛИ второйгруппы 14 и элементы И третьей. груп"пы 12 поступают на синхровход буферного регистра 19; обеспечивая записьна него минимальных решений. Содержимое счетчика 3 адреса поступает навход пуска блока 20 синхронизации, вшестом такте осуществляется анализ 10его на нуль. При неравенстве содержимого счетчика 3 адреса нулю управление передается четвертому такту,т.е. происходит ввод и анализ значе"ния следующего параметра, Если содержимое счетчика 3 адреса равно нулю, т.е. анализ всех параметров системы произведен, то управление передается седьмому такту.В седьмом такте осуществляется выбор решения для системы. По сигналус шестого выхода 77 блока 20 синхронизации, поступающем на второй входэлементов И второй группы 11, с выхода буферного 19 регистра минимальные решения системы в лингвистическойформе через элементы И второй группы 11 и элементы ИЛИ первой группы 13поступают на вход логической схемы15 сравнения, В регистре 16 кода срав-ЗОнения единица записывается в тот разряд, который соответствует максимальному значению решения системы из минимальных.В восьмом такте производится запись окончательного решения в регистр17 вывода по сигналу с восьмого выхода 79 блока 20 синхронизации.Логический процессор может использоваться в системах управления, для 40которых точная математическая модельфункционирования неизвестна. Например, в системах управления восстановлением работоспособности вычислительной системы при отсутствии досто-45верной статистической информации, всистемах управления технологическимипроцессами и т.д.По сравнению с известным предлагаемое устройство позволяет сократить 50аппаратные затраты за счет сокращенияобъема требуемой памяти,Для известного устройства объемтребуемой памяти равен где К - число ячеек первого и второго блоков памяти, равное сум 04 10ме мощности базовых множестввходных переменных;М - максимальное число лингвистических значений среди всехвходных параметров;1 - число бит, необходимых длякодирования степени принад"лежности с заданной точностью.В предлагаемой устройстве объем требуемой памяти равен Ч = К (Я 1 + 3) (бит),где И - число лингвистических значе"ний, имеющих ненулевую степень принадлежности к входному значению.Значение К определяется по формуле где Р - число параметров, характеризующих объект;1 - мощность терм-множества р-йлингвистической переменной.Для значений Р = 5, 1,= 1 = = 1 = 40, М = 7, М = 3, 1 = б имеем Ч, .= 5 40 7 6 = 8400 (бит); Ч = 5 40 (3 б + 3) = 4200 (бит). Таким образом, сокращение емкости требуемой памяти составляет для данного примера 503, что приводит к значительному сокращению аппаратных затрат. Необходимо отметить, что с возрастанием числа параметров и числа их базовых значений пропорционально воз" растает выигрыш в объеме требуемой памяти и оборудования в целом. Формула и з о б р т е н и я 1. Логический процессор, содержащий мультиплексор,.регистр адреса, счетчик адреса, три блока памяти, три регистра числа, три группы элементов И, две группы элементов ИЛИ, логическую схему сравнения, регистр кода сравнения, регистр вывода, операци" онный блок, буферный регистр и блок синхронизации, причем информационный вход мультиплексора является информационным входом процессора, выход мультиплексора подключен к информа 11 1 ЗО ИОД 12 ционному входу регистра адреса, син- ментов ИЛИ второй группы подключены к хровход которого подключен к шиневторым входам соответствующих элеменлогической единицы процессора, раз- тов И третьей группы, выходы которых ряды выхода которого подключены к подключены к синхровходу буферного соответствующим разрядам младшей груп регистра, тактовый вход блока синхропы адресного входа первого блока па- низации является тактовым входом промяти, разряды старшей группы адресных цессора, выход регистра вывода явля- входов с первого по третий блоков па- ется выходом номера решения процессомяти подключены к соответствующим ра, о т л и ч а ю щ и й с я тем, разрядам выхода счетчика адреса, ад О .что, с целью сокращения аппаратныхе ресного входа мультиплексора и входа затрат за счет снижения емкости памяпуска блока синхронизации, первый и ти, процессор содержит блок селекции второй выходы которого подключены и шифратор, причем вход шифраторасоответственно к установочному и счет- подключен к выходу регистра кода сравному входам счетчика адреса, третий 15 нения, разряды выхода шифратора подвыход - к входам чтения первого и ключены к соответствующим разрядам второго блоков памяти и синхровходам младшей группы адресного входа трепервого и второго регистров числа, тьего блока памяти, разряды младшей вход чтения третьего блока памяти группы адресного входа второго блока подключен к синхровходу третьего ре О памяти подключены к соответствующим гистра числа, к первым входам эле- разрядам выхода регистра адреса, инментов И первой группы и к четверто- формационный вход блока селекции подму выходу блока синхронизации, пятый ключен к выходу первого регистра чисвыход которого подключен к стробирую- ла, управляющий вход блока селекции щему входу операционного блока, а 25 подключен к выходу второго регистра шестой - к первым входам элементов И числа, разряды выхода блока селекции второй группы, вторые входы которых подключены к вторым входам соответстподключены к соответствующим разря- вующих элементов И первой группы. дам выхода буферного регистра и пер еПроцессор по п.1, о т л и ч авого информационного входа операцион ю щ и й с я тем, что операционный ного блока, второй информационный блок содержит Р групп (где Р - число вход которого подключен к информаци- эталонных ситуаций) по М операционных онному входу буферного регистра и к узлов (где И - разрядность значения выходу третьего регистра числа, ин- переменной), каждый из которых соформационные входы с первого по тре- З 5 держит элемент НЕ, входные элементы тий регистров числа подключены к ин- И и ИЛИ и выходные элементы И и ИЛИ, формационным выходам с первого по тре- причем вход элемента НЕ .-го операцитий блоков памяти соответственно, вы- онного узла 1-и группы ( = 1, ходы элементов И второй группы под- - 1, Р) является 1. - м разрядом 1-й ключены к первым входам соответствую группы первого информационного входа щих элементов ИЛИ первой группы, вто- , операционного блока, выход элемента рые входы которых подключены к выхо- НЕ каждого операционного узла поддам соответствующих элементов И пер- ключен к первым входам входных элевой группы, выходы элементов ИЛИ пер- ментов И и ИЛИ того же операционного вой группы подключены к соответствую узла, вторые входы входных элементов щим разрядам входа логической схемы И и ИЛИ -го операционного узла 1-й сравнения, выход которой подключен группы подключены к д-му разряду к информационному входу регистра ко-й группы второго информационного да сравнения, выход которого подклю- входа операционного блока, выходы чен к информационному входу регистра 50 входных элементов И и ИЛИ каждого вывода, синхровход которого подключен операционного узла подключены к перк седьмому выходу блока синхрониза- вым входам соответственно выходных ции, восьмой и девятый выходы которо- элементов ИЛИ и И того же операционго поцключены к первым входам соот- ного узла, второй вход выходного эле" ветственно элементов И третьей группы 55 мента ИЛИ каждого операционного узла и элементов ИЛИ второй группы, вторые подключен к выходу выходного элеменвходы которых подключены к соответ- та И того же операционного узла, выствующим разрядам информационного вы- ход выходного элемента ИЛИ д-го ( хода операционного блока, находи зле- = 1, - 1 г операционного узла 1-й груп13 13057 пы подключен к второму входу выходного элемента И ( + 1)-го операционного узла той же группы, выход выходного элемента ИЛИ И-го операционного узла 1-й группы является -м разрядом информационного выхода операционного блока, вторые входы выходных элементов И первых операционных узлов всех групп подключены к стробирующему входу операционного Ю блока.ф3. Процессор по п.1, о т л и ч аю щ и й с я тем, что блок синхронизации содержит счетчик, двадцать один 15 элемент И, семь элементов НЕ и пять элементов ИЛИ, причем первый, второй и четвертый разряды информационного входа счетчика подключены к входу логического нуля блока, третий разряд информационного входа счетчика подключен к входу логической единицы блока, синхровход, вход начальной установки и тактовый вход счетчика подключены соответственно к выходам 25 первого, второго и третьего элементов И, первые входы которых подключены к тактовому входу блока синхронизации, второй вход первого элемента И подключен к выходу четвертого З 0 элемента И, входу первого элемента НЕ и первому входу пятого элемента И, второй вход которого подключен к выходу второго элемента НЕ, вход которого подключен к третьему входу первого элемента И и к выходу первого элемента ИЛИ, входы которого являются соответствующими разрядами входа пуска блока синхронизации, выходы первого элемента НЕ и пятого элемента И подключены соответственно к первому и рторому входам второго элемента ИЛИ, выход которого подключен к второму входу третьего элемента И, третий вход которого подключен к вы ходу третьего элемента НЕ, вход которого подключен к второму входу второго элемента И и к выходу шестого элемента И, первый вход которого под" ключен к выходу четвертого элемента НЕ, первым входам четвертого, седьмого и восьмого элементов И, второй вход шестого элемента И подключен к выходу пятого элемента НЕ, к первому входу девятого элемента И и к второму входу седьмого элемента И, третий вход шестого элемента И подключен к выходу шестого элемента НЕ и к первым входам десятого и одиннадцатого 04 14элементов И, второй вход одиннадцатого элемента И подключен к четвертому входу шестого элемента И и к входу седьмого элемента НЕ, выход которого подключен к вторым входам четвертого и десятого элементов И и к первому входу двенадцатого элемента И, второй вход которого подключен к входу шестого элемента НЕ и к третьему входу четвертого элемента И, четвертый вход которого подключен к входу пятого элемента НЕ, к второму входу восьмого элемента И и к первому входу тринадцатого элемента И, второй вход которого подключен к второму входу девятого элемента И и к входу четвертого элемента НЕ, входы четвер. того, пятого, шестого и седьмого элементов НЕ подключены соответственно к первому, второму, третьему и четвертому разрядам выхода счетчика, вы" ход десятого элемента И подключен к первым входам элементов И с четырнадцатого по семнадцатый, выход одиннадцатого элемента И подключен к первому входу восемнадцатого элемента И, второй вход которого подключен к выходу седьмого элемента И и к первому входу девятнаццатого элемента И, второй вход которого подключен к выходу двенадцатого элемента И, к первым входам двадцатого и двадцать первого элементов И и к второму входу семнадцатого элемента И, вторые входы четырнадцатого и двадцать первого элементов И 1подключены к выходу восьмого элемента И, вторые входы пятнадцатого и двадцатого элементов И подключены к выходу девятого элемента И, второй вход шестнадцатого элемента И подключен к выходу тринадцатого элемента И, выходы четырнадцатого и двадцатого элементов И подключены соответственно к первому и второму входам третьего элемента ИЛИ, выходы пятнадцатого и девятнадцатого элементов И подключены соответственно к первому и второму входам четвертого элемента ИЛИ, выходы шестнадцатого и двадцать первого элементов И подключены соответственно к первому и второму входам пятого элемента ИЛИ, выходы с первого по девятый блока синхронизации подключены соответственно к выходам девятнадцатого элемента И, пятнадцатого элемента И, четвертого элемента ИЛИ, третьего элемента ИЛИ, двадцать первого элемента И, семнад 15 1305704 6 цатого элемента И восемнадцатого мультиплексоров подключены к управля 1Ъч элемента И, пятого элемента ИЛИ и ющему входу блока селекции, 1-и вышестнадцатого элемента И. ход -го демультиплексора Ц = 1, К;1,М) подключен к 1-му входу эле 4. Процессор по п.1, о т л и ч а ментов ИЛИ 1-й группы (где 1+-2), ю щ и й с я тем, что блок селекции разряды первого выхода первого десодержит группы элементов ИЛИ, Б де- мультиплексора, выходов элементов мультиплексоров, информационные входы ИЛИ групп и К-го выхода В-го демулькоторых образуют информационный вход типлексора образуют выход блока себлока селекции, управляющие входы де лекции.

СмотретьЗаявка

3941764, 08.08.1985

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

БАЛАШОВ ЕВГЕНИЙ ПАВЛОВИЧ, КУПРИЯНОВ МИХАИЛ СТЕПАНОВИЧ, ПАНТЕЛЕЕВ МИХАИЛ ГЕОРГИЕВИЧ

МПК / Метки

МПК: G06F 17/21

Метки: логический, процессор

Опубликовано: 23.04.1987

Код ссылки

<a href="https://patents.su/12-1305704-logicheskijj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Логический процессор</a>

Предыдущий патент: Устройство для разбиения графа на подграф

Следующий патент: Устройство для решения транспортных задач

Случайный патент: Щуп-натекатель