Устройство для последовательного программного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

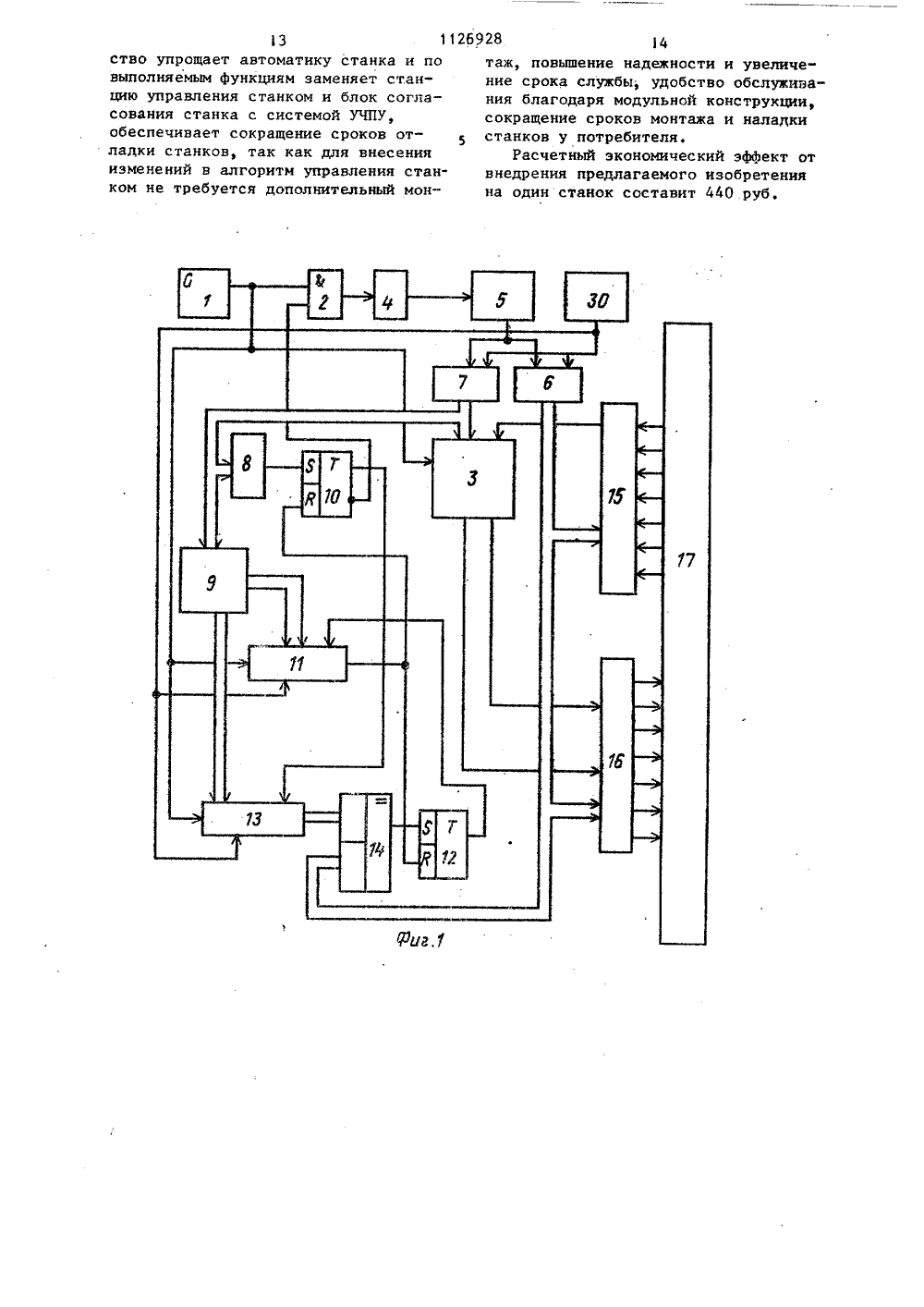

(9) ( 26928 А 19/18 ОПИСАНИЕ ИЗОБРЕТЕНИЯ,:И АВТОРСКОМУ СВИДЕТЕЛЬСТВУ знака коррекции, две группы тов И и инвертор, информаци входы коммутаторов соединен ходами программных иереключ выходы коммутаторов ио коли разрядов подключены к первы еменонные1 с выеству входам ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССГ 10 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРИТИ(71) Особое конструкторское бюро станкостроения(54)(57) 1. УСТРОЙСТВО ДЛЯ ПОСЛЕДОВАТЕЛЬНОГО ПРОГРАМИНОГО УПРАВЛЕНИЯ,содержащее генератор тактовых импульсов, выход которого соединен.с первым входом вычислительного блока,первый счетчик команд через блокпамяти соединен с первыми входамипервого и второго регистров, подключенных .вторыми входами к выходу блоканачальной установки, выходы второгорегистра подключены к первым входамвычислительного блока, выходы первого регистра соединены с адреснымивходами входных и выходных преобразователей, выходы входных преобразователей подключены к второму входу вычислительного блока информационные выходы которого соединены с информационными входами выходных преобразователей, о т л и ч а ю щ е е - .с я тем, что, с целью упрощения устройства, в него введены блок за"держек, элемент И, ьторой счетчикимпульсов и последовательно соединенные дешифратор, первйй КБ-триггер,третий счетчик импульсов, блок сравнения кодов и второй КБ-триггер, прямой выход которого соединен с управляющим входом второго счетчика импульсов, подключенного выходом к К"входам первого и второго КБ-триггеров, а входами предварительной установки - к первым выходам блока задер жек, вторые выходы которого соединены с входами предварительной установки третьего счетчика импульсов, счетный вход которого соединен с выходом генератора тактовых импульсов, со счетным входом второго счетчика импульсов и с первым входом элемента И, второй вход которого подключен к инверсному выходу первого КБ-триггера, а вы- Щ ход - к информационному входу первого счетчика импульсов, установочный вход которого соединен с выходом блока начальной установки, вторые входы блока сравнения кодов подключены к выходам первого регистра, Б-вход перрого КБ-триггера через дешифратор соединен с адресными выходами второго регистра и с входами блока задержек, входы обнуления второго и третьего счетчиков импульсов соединень" с выходом блока начальной установки2. Устройство по п. 1, о т л ич .а ю щ е е с я тем, что блок задержек содержит программные переключатели по числу корректируемых задержек, коммутаторы ио числу разрядов первого регистра, коммутатор1126928 элементов И.первой и второй групп,вторые входы первой группы элементов И через инвертор и вторые входывторой группы элементов И непосредственно подключены к выходу коммутаИзобретение относится к областиавтоматики и вычислительной техникии может быть использовано для управления металлорежущим станком.Известно устройство для последовательного программного управления,содержащее последовательно соединенные генератор тактовых импульсов,счетчик команд, запоминающий блок,регистр команд и блок задания команд.Выход блока задания команд подключенк второму входу счетчика команд,Второй вход блока задания соединенс выходом логического операционногоблока и с первым входом выходногоблока согласования и нормированиясигнала. Второй вход этого блока через выходной коммутатор соединен свторым выходом регистра команд ис первым входом входного коммутатора. 20Второй вход этого коммутатораподключен к выходу входного блокасогласования и нормирования сигналов, Третий выход регистра командподключен кпервому входу логического операционного блока, Повышениебыстродействия устройства достигается за счет введения блокасвертки информации, первый вход которого подключен к выходу входного ЗОкоммутатора, выход - к второмувходу логического операционного блока, а второй и третий входы - к четвертому и пятому выходам регистракоманд, а также за счет того, что З 5блок свертки информации выполнен, на логических элементах ИЛИ -ИСКЛЮЧАЮЩЕЕ, ИЛИ и И 1,Недостатком этого устройстваявляется узкая область применения; 40не позволяет формировать корректируемые временные команды (задержки).Наиболее близким по техническойсущности к предлагаемому являетсяРустройство, содержащее входные тора знака коррекции, выходы элемен-. тов И являются выходами блока, входы которого подключены к адресным входам коммутаторов по числу разрядов первого регистра. 1и выходные преобразователи информации, связанные с вычислительным блоком, генератор тактовых импульсов, выход которого подключен к входу вычислительного блока и к входу счетчика команд, кодовые выходы которого подключены к.входам блока памяти, выходы последнего соединены с вычислительным блоком. В процессе работы устройства с помощью вычислительного блока из блока памяти последовательно считываются и обрабатываются команды программы 2 "1Однако последовательность обработки команды, поступающей с входных и выходных преобразователей, обусловлена алгоритмом управления и в случае формирования программируемых временных команд (задержек) требует усложнения вычислительного блока и блока памяти. Так как при наладке станка возникает необходимость оперативногс изменения параметров временных команд, то это приводит к увеличению времени предварительной наладки и переналадки станка в процессе эксплуатации. Цель изобретения - упрощение устройства за счет сокращения объема памяти при использовании временных команд (задержек), параметры которых необходимо сКорректировать во время наладки станка.Поставленная цель достигается тем, что в устройство для последовательного программного управления, содержащее генератор тактовых импульсов, выход которого соединен с первым входом вычислительного блока, первый счетчик импульсов через блок памяти соединен с первыми входами первого и второго регистров, подключенных вторыми входами к выходу блока начальной установки, выходы второго регистра подключенык первым входам вычислительного блока, выходы первого регистра соединены с адресными входами входных и выходных преобразователей, выходы входных преобразователей подключены к второмувходу вычислительного блока, информационные выходы которого соединены с информационными входами выходных преобразователей, введены блок за" держек, элемент И, второй счетчик импульсов и последовательно соединенные дешифратор, первый КБ- триггер, третий счетчик импульсов, блок сравнения кодов и второй КЯ- .триггер, прямой выход которого сое динен с управляющим входом второго счетчика импульсо, подключенного выходом к К-входам первого и второго КЯ-триггеров, а входами предварительной установки к первым выходам 2 О блока задержек, вторые выходы которого соединены с входами предварительной установки третьего счетчика импульсов, счетный вход которого соединен с выходом генератора такто вых импульсов, со счетным входом второго счетчика импульсов, и с первым входом элемента И, второй вход которого подключен к инверсному выходу первого КБ-триггера, а вы ход - к информационному входу первого счетчика импульсов, установочный вход которого соединен с выходом блока начальной установки, вторые входы блока сравнения кодов подключены к выходам первого регистра, Б-вход первого КБ-триггера через дешифратор соединен с адресными выходами второго регистра и с входами блока задержек, входы обнуления второго и третьего 40 счетчиков, импульсов соединены с выходами блока начальной установки.Блок задержек содержит программные переключатели по числу корректируемых задержек, коммутаторы по числу раэ рядов первого регистра, коммутатор знака коррекции, две группы элементов И и инвертор, информационные входы коммутаторов соединены с выходами программных переключателей, 50 выходы коммутаторов по количеству разрядов подключены к первым входам элементов И первого и второй групп, вторые входы первой группы элементов И через инвертор и вторые входы вто рой группы элементов И непосредственно подключены к выходу коммутатора знака коррекции, выходы элементов И являются выходами блока, входыкоторого подключены к адресным входамкоммутаторов по числу разрядов первого регистра,Блок задержек содержит программныепереключатели по числу корректируемыхзадержек, коммутаторы по числу разрядов первого регистра, коммутаторзнака коррекции, две группы схем И,причем количество элементов И в каждой группе определено количествомкоммутаторов, а также инверторов.Адресные входы коммутаторов, соединенные параллельно в соответствии с номером разрядов, образуют входыблока, информационные входы коммутаторов соединены с выходами программных переключателей. Выходы коммутаторов соединены с первыми входами всех элементов И, Вторые входыпервой группы элементов И через иивертор подключены к выходу коммутатора знака коррекции. Вторые входывторой группы элементов И непосредственно подключены к выходу этого коммутатора. Входы элементов И образуютвыходы блокаКоммутатор знака коррекции по своему выполнению конструктивно не отличается от всех остальных коммутаторов.Включение в устройство блока задержек, двух триггеров, элементов И,блока сравнения, дешифратора и двухсчетчиков позволяет уменьшить объемблока памяти, необходимый для программирования величин задержек,На фиг.1 приведена структурнаясхема устройства; на Фиг.2 - схемаблока задержек, на Фиг.З - принципиальная схема вычислительного блока;на фиг.4 - принципиальная схема дешифратора, на Фиг.5 впринципиальнаясхема начальной установки.1Устройство содержит генератортактовых импульсов 1, элемент И 2и вычислительный блок 3. Выход элемента И 2 соединен со счетным входомпервого счетчика 4, который является счетчиком команд, кодовые выходысчетчика. команд 4 соединены с входамиадреса блока 5 памяти, информационные выходы которого соединены с входами первого регистра 6 и второго7, а также дешифратор 8, блок 9задержек, первый КБ-триггер 10,счетчик импульсов 11, второй КБтриггер 12, третий счетчик 13 импульсов, блок сравнения 14, нхолные1126преобразователи 15, выходные преобразователи 16, абъекг управления 17.Первый регистр 6 предназначендля запоминания кода адреса входаили выхода соответствующего данному 5шагу программы, второй регистр 7предназначен для запоминания кодаоперации, которую нужно выполнитьна данном шаге программы.ДешиФратор 8 предназначен для 1 Овыявления кода операции с выдержкойвремени и поэтому только один вьгкод,Счетчик 11 импульсов представляетсобой двоичный счетчик с предварительной установкой начального састбяния и установкой в "0" и осуществляетсчет на вычитание. Ега разрядностьопределяется величиной необходимойкоррекции величины выдержки време"ни в сторону ее увеличения, 2 ОСчетчик импульсов 13 представляет собой двоичный счетчик, имеющийвход обнуления, а также входы предварительной установки начального состояния, соединенные с первыми выходами блока 9 задержек.ИнФармационные выходы входныхпреобразователей 15 соединены с третьим инФормационным входом вычислительного блока 3, первый выход кото- ЗОрого подключен к управляющему входу,а второй выход - к инФормационномувходу выходных преобразователей 16,Блок задержек 9 (Фиг,2) содержитпрограммные переключатели 18 па чис- З;лу разрядов регистра 6, выход которых соединен с инФармационными входами соответствующих коммутаторов 19и коммутатора знака коррекции 20,адресные входы которых соединены 0,с выходами соответствующих разрядоврегистра 7, Выход коммутатора 20 соединен через инвертор 21 с вторымивходами элементов И 22 и непосредст"венно с вторыми входами элементов 45И 23, выходы которых соединены свходами предварительной установкисчетчика 11, выходы элементов И 22соединены с входами предварительнойустановки счетчика 13. Первые входы уэлементов И 22 и 23 соединены свыходами коммутаторов 19,На Фиг.3 представлена принципиальная схема вычислительного блока 3состоящего из элемента 24 постоянной памяти и регистра 25, входсинхронизации которого образуетпервый вход блока 3,928 ЬАдресный вход А элемента 24постоянной памяти образует третийвход вычислительного блока 3, который соединен с выходом преобразователя 15.Адресные входы элемента 24 постоянной памяти Ао- А, образуют вторые входы блока 3, причем числоэтих входов равно числу, гдеЙ -количество разрядов регистра 7.Адресный вход А 1элемента 24 соединен с выходам регистра 25. Кроме того, выход регистра 25 образуетвторой, или инФармационный, выходблока 3. ИнФормацианный вход регистра 25 соединен с первым выходомэлемента 24 постоянной памяти. Второй выход элемента 24 образует первый, или управляющий выход блока 3.Элемент 24 постоянной памяти предназначен для хранения всех возможных результатов логических операцийвыполняемых блоком 3, и имеети+яооъем памяти 2 слов по два разряда в каждом. Если число И+2 непревосходит. десяти, элемент 24мажет быть выполнен на одной микро"схеме К 573 РФ 1,Регистр 25 предназначен для хранения результата очередной логической операции и имеет для данногопримера реализации только один разряд, Регистр 25 может быть выполненна одном триггере Р -типа из микросхемы К 155 ТИ 2,На Фиг.4 представлена принципиальная схема дешиФратора 8. ДешиФратор 8 включает в себя мнаговходавой элемент И"НЕ 26, выход которого соединен с входом элемента НЕ 27, 5 - входам триггера 28 и первым входом элемента И-ИЕ 29. Выход элемента. НЕ 27 соединен с Р -входом триггера 28, прямой выход которого соединен с вторым входом элемента И-НЕ 29, Входы элемента И-НЕ 26 образуют входы дешиФратора 8 и соединены с выходами регистра 7 и с входами, блока 9. Число входов элемента И-НЕ 26 равно числу разрядов регистра 7. Выход элемента И"НЕ 29 образует вы" ход дешиФратара 8, который соединен с Б-входом триггера 10.Элементы 26.27,29, а также триггер 28 могут быть реализованы на соответствующих элементах серии микросхем К 155.7 1126Входы обнуления счетчиков импульсов 4,11, 13 и регистров 6 и ), соединены между собой и подключеиы к выходу блока начальной установки 30. В блок начальной установки 30 входитРС-цепь, состоящая из веэистора 31 и конденсатора 32 (фиг.5) . Блок начальной установки 30 служит для формирования импульса сброса в нулевое состояние счетчиков импульсов 4, 11, 1 О 13 и регистров 6,7 в первый момент времени после включения питания устройства.Разрядность регистра 6, блока сравнения 14, счетчика 13, счетчика 15 11, а также количество элементов И 22, элементов И 23 и количество коммутаторов 19 определяются в конечном итоге числом входов-выходов всего устройства. Разрядность ре гистра 7 определяется количеством команд, необходимых для работы вычислительного блока 3, и числом корректируемых задержек, Количество информационных разрядов блока 5 25 памяти определяется как сумма разрядов регистров 6,7,Программирование операций с выдержкой времени осуществляется при помощи двух командных слов: пер- З 0 вое слово - обычное, состоящее из кода операции с признаком выдержки времени и адреса входа, воздействие которого необходимо задержать; второе слово состоит иэ номера задержки определяемого количеством разрядов регистра 7, и величины выдержки времени срабатывания, определяемой количеством разрядов регистра 6.Устройство работает следуюпрм 40 образом.В первый момент времеви после включения питания устройства с выхода блока начальной установки 30 поступает короткий импульс, который уста навливает в ноль счетчики 4, 11,13 и регистры 6 и 7.В результате на первых и вторых входах блока сравнения 14 устанавливают одинаковые нулевые коды. Сиг налы с выхода блока сравнения 14 устанавливают триггер 12 в единичное состояние, что приводит к снятию запрета на счет счетчику импульсов 11. Так как счетчик 11 предва рительно установлен в нулевое сос" тояние и является счетчиком на вычитание, то по первому же импульсу 928 8с генератора 1 тактовых импульсов, поступающих на счетный вход счетчика 11, происходит ого переполнение, В результате на его выходе переполнения появляется сигнал, который устанавливает в "0" триггеры 10 и 12.Нулевое состояние Рс-триггера 10 разрешает прохождение .тактовых импульсов с генератора 1 через элемент И 2 на счетный вход счетчика 4. Нулевое состояние триггера 12 снова запрещает счет счетчику 11, переводя его в режим предварительной установки. После. этого устройство гртово к работе.Длительность импульса с выхода блока начальной установки 30 задается элементами РС 31,32 и выбирается таким образом, чтобы его окончание произошло позже того момента, когда сработает триггер 12.С выхода генератора 1 тактовых импульсов импульсы постоянной частоты поступают на тактовый вход вычислительного блока 3, на счетные входы счетчиков импульсов 11 и 13 и через элемент И 2 на счетный вход счетчика 4 команд. Счетчик 4 команд состоянием своих разрядов определяет адрес очередного командного слованаходящегося в блоке 5 памяти, Командное слово состоит из двух полей: поля адреса, разряды которого записываются в регистр б, и поле кода операции, разряды которого записываются в регистр 7.Устройство может работать в двух режимах: выполнение операции без выдержки времени и выполнение операции с выдержкой времени.В первом режиме РС-триггеры 10 и 12 находятся в нулевом состоянии. Сигнал с инверсного выхода триггера 10 разрешает прохождение 1счетных импульсов через элементИ 2 на счетный вход счетчика 4 команд. Код операции с регистра .7, поступая на второй вход вычислительного блока 3, определяет вид операции над входными данными, поступающими с входных преобразователей 15 на третий вход вычислительного блока 3. Результат операции с информационного выхода блока 3 выдается по адресу, определяемому состоянием регистра 6, на информационный вход выходных преобразователей 16. Сигна.лы с прямых выходов РС-триггеров112610 и 12 удерживают соответственносчетчики 13 и 11 в режиме предварительной установки, запрещая имсчет.Во втором режиме работы устройства при наличии в коде операции,находящемся в регистре 7, признаказажержки через дешифратор 8 происходит установка триггера 10 в единичное состояние. Тем самым запре Ощается прохождение тактовых импульсов с генератора 1 через элемент И 2на счетный вход счетчика 4 команд.Счетчик 4 команд останавливается,фиксируя в регистрах 6 и 7 следующее 5командное слово, в котором программируется комер и величина выдержкивремени. Одновременно с этим управляющий сигнал с прямого выхода триггера10 переводит счетчик импульсов 2013 из режима предварительной установки в режим счета. На программных переключателях18,число которых определяется коли 25чеством корректируемых задержек,задается знак и величина необходимойкоррекции. Сигналы с переключателей18 поразрядно подаются на информационные входы коммутаторов 19 величи-оны коррекции временной задержки иинформационный вход коммутатора 20знака этой коррекции. Адресные входыкоммутаторов 19 и 20 соединены с выходами соответствующих разрядов 35регистра 7, которые определяют номер выбранной задержки, коммутируявеличину ее коррекции на первыевходы элементов И 22 И 23.Выходы элементов И 22 соединены 40поразрядно с входами предварительнойустановки счетчика 13. Это позволяет задавать начальное состояние счетчика 13 и тем самым корректировать величину необходимойзадержки в сторону уменьшения,оКод с выхода счетчика 13 поразрядно поступает на вторые входы блокасравнения 14, на первые входы которого поразрядно поступает двоичный 5 Окод заданной по программе величинызадержки из регистра 6. В моментсовпадения кодов по сигналу с выкода блока сравнения 14 триггер12 устанавливается в единичное состояние, в результате на управляющийвход счетчика 11 поступает разрешение на смет. Исходное состояние 928 10счетчика 11 определяется кодом,выставленным на выходах элементаИ 23. Это позволяет реализоватькоррекцию величины выдержки временив сторону увеличения за счет дополнительного времени, необходимогодля уменьшения содержимого счетчикаимпульсов 11 от исходного состояния до нуля, т,е. до выработки навыходе счетчика импульсов 11 сигналапереполнения по нулевому состоянию.Импульс переполнения счетчика импульсов 11 устанавливает триггер 10 и12 снова в нулевое состояние, разрешая счет счетчику 4 команд и определяя тем самым момент окончания выдержки времени,Если дальше в программе запрограммирована команда выдачи сигналауправления на соответствующий выход,что обычно имеет место, то эта выдача происходит только через время,величина которого задана в предыдущемкомандном слове и скорректированав сторону уменьшения или увеличенияв зависимости от положения програм -мных переключателей 18.Вычислительный блок 3 работаетследующим образом.Адрес ячеики памяти элемента 24постоянной памяти образован разрядами регистра 7, в котором хранитсякод очередной логической операции, а также состоянием входа устройства, поступающего с выхода преобразователя 15, адресуемого при,помощи регистра б.Результат предыдущей логической операции, хранящийся в регистре 25 и поступающий на ОЙ+2)-й адресный вход элемента 24, также участвует в адресации результата следующей логической операции.Таким образом, информация, записанная в ячейках памяти элемента 24, зависит от результата предыдущейоперации, состояния соответствующего входа устройства и вида логической операции, которую нужно выполнить над этими двумя операндами. Эта информация и является результатом очередной логической операции, Этот результат при помощи тактового импульса, поступающего с выхода генератора 1, записывается в регист 25 и поступая на (И+2)-й адресный вход элемента 24, участвует в формирования адреса результа 11 11269 та следующей, новой операции, также записанного в элементе 24.Очередное командное слово, выбранное счетчиком 4 команд из блока 5 памятй и состоящее из двух частей, своей операционной частью, записанной в регистре 7, определяет вид очередной логической операции, выполняемой блоком 3, т.е. состояние адресных входов от А, до А 11 элемен та 24 постоянной памяти.Адресная часть командного слова из блока 5 переписывается в регистр 6, который определяет, с какого ,входа устройства поступает информация 15 на (8+1)-й адресный вход элемента 24. На (8+2)-м адреснсм входе элемента 24 в этот момент присутствует результат предыдущей операции с выхода регистра 25, Сформированный таким образом адрес из К+2 разрядов определяет адрес ячейки памяти элемента 24, где хранится результат заданной логической операции.Результат очередной операции хра нится в регистре 25. Если следующая операция не является командой вывода результата, то на втором выходе элемента 24 постоянной памяти отсутствует управляющий сигнал, а содержимое регистра 25 участвует в Формировании адреса результата следующей операции.Если очередная, выбранная из блока 5, команда является командой вывода результата, на втором выходе элемента 24 появляется управляющий сигнал, поступающий на управляющий вход выходного преобразователя 16. Этот сигнал разрешает выдачу результата из регистра 25 через преобразователь 16 на соответствующий вы 40 ход устройства. Адрес этого выхода задается в адресной части того же командного слова, в операционной части которого записан код операции45 вывода.Этот адрес с выходов регистра 6 поступает на адресные входы выходного преобразователя 16 и определяет номер выхода устройства, на который нужно вывести сигнал включения или выключения соответствующего исполнительного элемента объекта управле ".,ния 17.Лешифратор 8 работает следующим образом, 55В первом слове команды выдержки времени содержится код этой команды (в данном примере все единицы), Этотав 28 12код с выходов регистра 7 поступаетна входы элемента И-НЕ 26. На выходе элемента 26 в этом случае будет "О" ,поступающий на первый входэлемента И-НЕ 29 и блокирующий темсамым прохождение сигнала на выходдешифратора 8. Одновременно с этим"0" поступающий с выхода элементаУ26, идет на 5 -вход триггера 28,устанавливая триггер 28 в единичное состояние.Таким образом, после приема первого слова, содержащего код команды с выдержкой времени, на выходедешифратора 8 не вырабатываетсясигнал для установки триггера 10.После приема второго слова командывыдержки времени в регистре 7 содержится номер задержки. Код номеразадержки отличается от признакакоманды с выдержкой времени (достаточно, чтобы хотя бы один из разрядов регистра 7 стал нулевым). В этомслучае на выходе элемента 26 устанавливается " 1", которая разрешаетпрохождение сигнала на выход элемента И-НЕ 29.Этот сигнал устанавливает триггер 10 в единичное состояние,запрещая тем самым прохождение тактовых импульсов с генератора 1 через элемент И 2 на вход счетчика 4.Одновременно с этим "1" с выходаэлемента И-НЕ 26 поступает через элемент НЕ 27 на Р-вход триггера 28,Триггер 28 устанавливается в нулевоесостояние, которое опять запрещаетпрохождение сигналов через элементИ-НЕ 29 на вход триггера 10 и уставливает дешифратор 8 в исходное состояние, подготовив его для приеманового признака команды с выдержкойвремени.Введение в устройство относителыпростого блока задержек, двух триггеров, элементов И, блока сравнения,дешифратора и двух счетчиков позволяет сократить объем блока памяти,необходимого для программированияяоманд с выдержкой времени и расширяет функциональные возможности,позволяя проводить оперативную корректировку величин выдержек временипри отладке, эксплуатации и ремонтестанков,По сравнению с базовым объектом(серийно применяемый релейныйблок управления, например на станке 2 А 622 Ф 2-1) предлагаемое устрой 1 г 6928ство упрощает автоматику станка и повыполняемым функциям заменяет станцию управления станком и блок согласования станка с системой УЧПУ,обеспечивает сокращение сроков отладки станков, так как для внесенияизменений в алгоритм управления станком не требуется дополнительный монтаж, повышение надежности и увеличение срока службы, удобство обслуживания благодаря модульной конструкции,сокращение сроков монтажа и наладкистанков у потребителя,Расчетный экономический эффект отвнедрения предлагаемого изобретенияна один станок составит 440 руб.

СмотретьЗаявка

3632139, 10.08.1983

ОСОБОЕ КОНСТРУКТОРСКОЕ БЮРО СТАНКОСТРОЕНИЯ

БЕЛОВ БОРИС ВАСИЛЬЕВИЧ, ГОЛЬДИН ЯКОВ ГЕЛЕЕВИЧ, МАЛЬЧИК АНАТОЛИЙ ЯКОВЛЕВИЧ, ПАЛК КОНСТАНТИН ИЛЬИЧ, СПЕКТОР ЛЕОНИД БЕНЦИАНОВИЧ, ФАЙНШТЕЙН ЛЕВ НАУМОВИЧ, ЦЫБУЛЬСКИЙ ГРИГОРИЙ ДАВИДОВИЧ

МПК / Метки

МПК: G05B 19/18

Метки: последовательного, программного

Опубликовано: 30.11.1984

Код ссылки

<a href="https://patents.su/11-1126928-ustrojjstvo-dlya-posledovatelnogo-programmnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для последовательного программного управления</a>

Предыдущий патент: Система управления с координатно-параметрической обратной связью

Следующий патент: Привод периодической подачи металлорежущих станков

Случайный патент: Иокровой источник возбуждения спектра для спектрального анализа