Устройство различения сигналов на фоне произвольной помехи

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

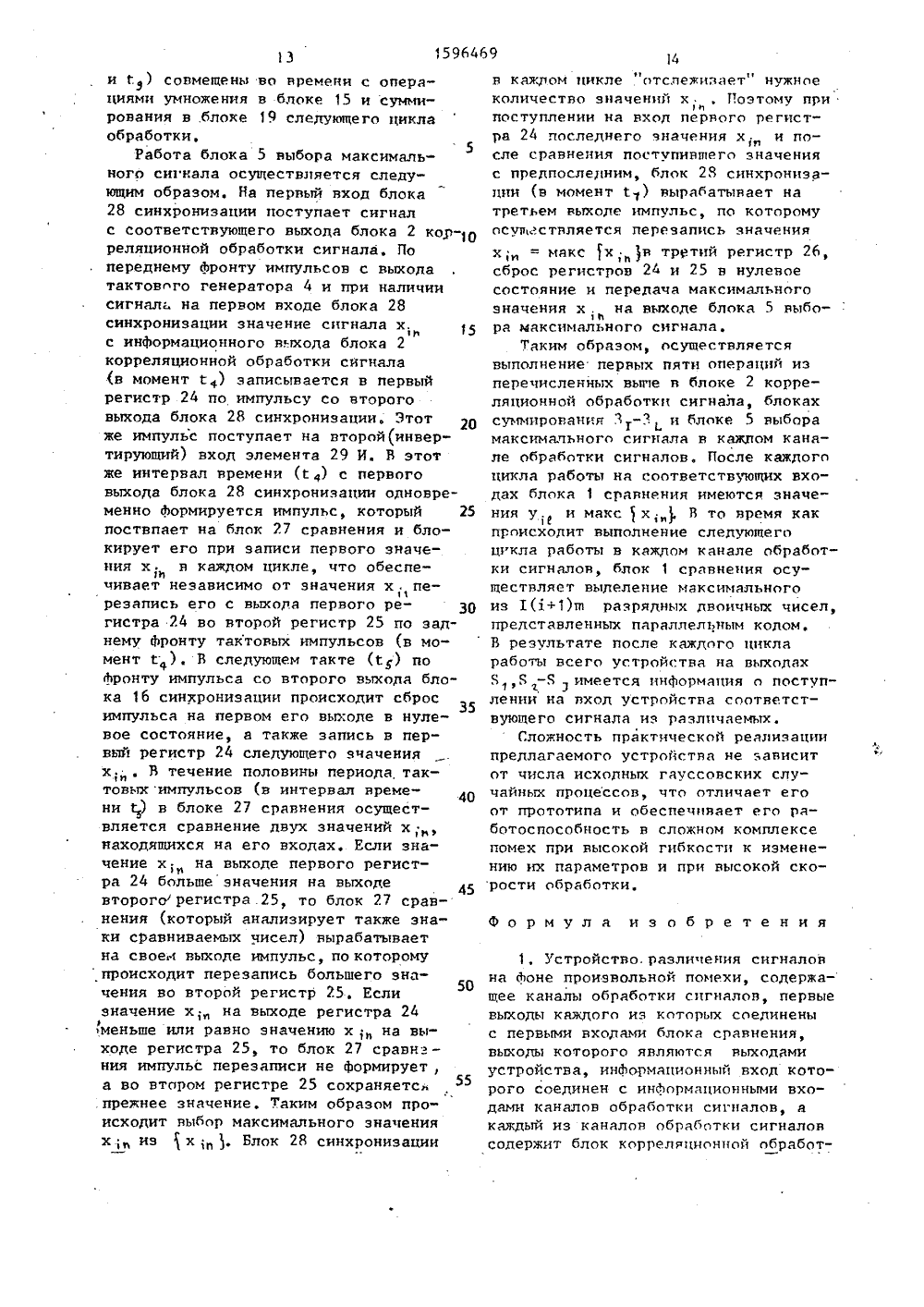

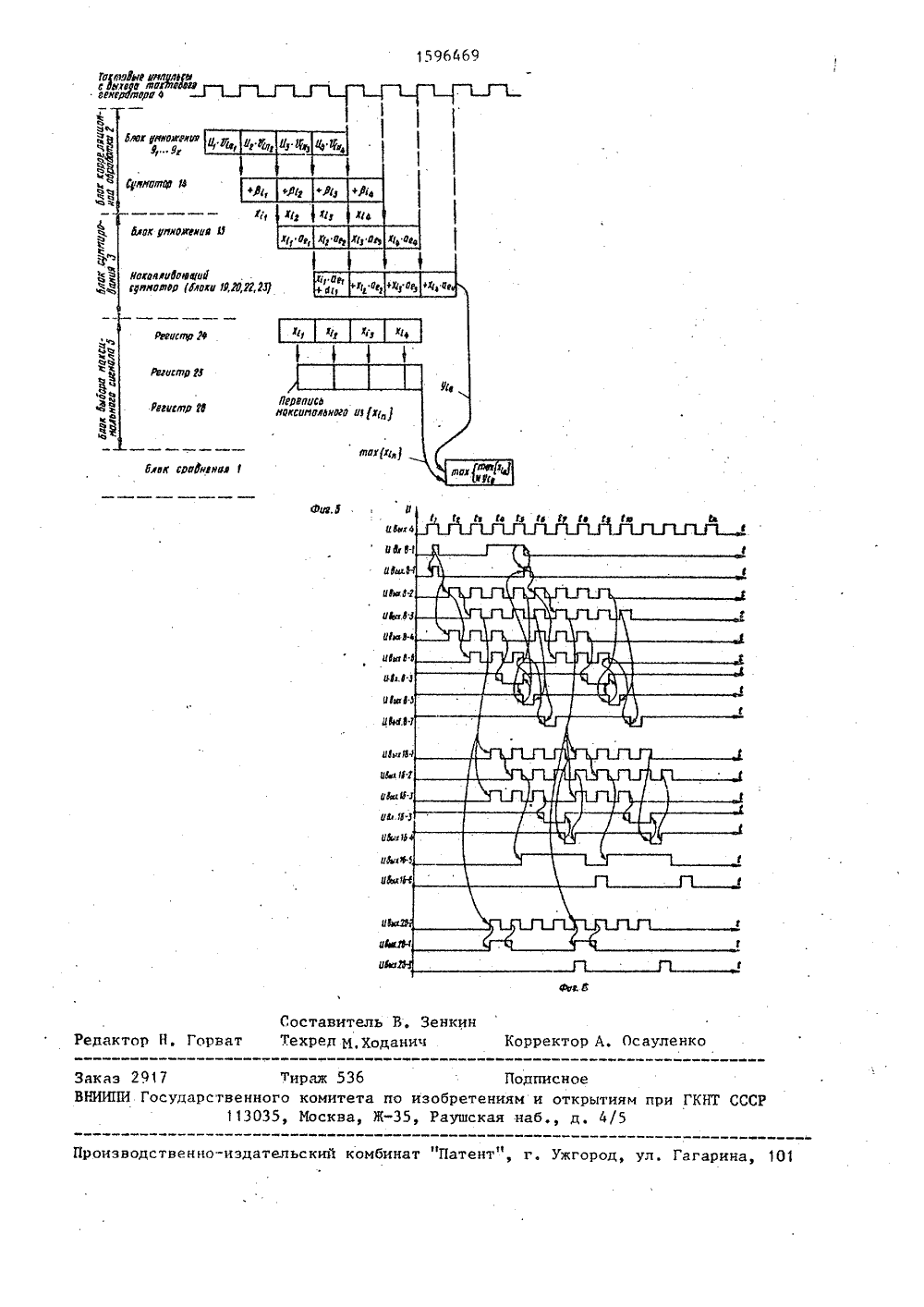

окал,еиймФи уевлр Фю гиюр 0 Составитель В. ЗенкТехред М,Ходанич Редак Горна Осаул оррек 536 сударственного комитета 113035, Москва, Ж ственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 101 аказ 29НИИПИ Г Подпи изобретениям и Раушская набноеткрытиям при ГКНТ СССд. 4/51596469 товый генератор 4, в каждый каналобработки сигналов введен блок 5выбора максимального сигнала, а блок3 корреляционной обработки сигнала,5выполнен в виде блока регистров,блока синхронной записи, блокаспнхройизации, блоков умножителей,первого запоминающего блока, первого Изобретение относится к электросвязи и может использоваться в приемниках сш налов радиоуправления и радиолокационьых станций.Цель изобретения - повьппение верности приема в условиях действия по Омех с изменяющимися параметрами.На Фиг. 1 приведена структурнаяэлектрическая схема устройства различения сигналов на Фоне произвольной помехи; на Фиг, 2 - структурная, 25электрическая схема блоков корреляционной обработки сигнала, входящихв его состав; на Фиг. 3 и 4 - примеры выполнения соответственно блокасуммирования и блока выбора макси- .мального сигнала; на Фиг. 5 и 6;временные диаграммы, поясняющие работу устройства,Устройство различения сигналовна Фоне произвольной помехи содержитканалы (А) обработки сигналов иблок 1 сравнения, а каждый каналобработки сигналов содержит блок 2корреляционной обработки сигнала иблоки 3, суммирования, а также,содержит тактовый генератор 4, а каждыйканал обработки сигналов - блок 5выбора максимального сигнала,Блок 2 корреляционной обработкисигнала, входящий в состав каждого 45канала обработки сигналов, изображешпй на Фиг. 2, содержит блок6 1-к регистров, блок 7 асинхроннойзаписи, блок 8 синхронизации, блок 91-к умножителей, первый запоминающийблок 10, первый и второй счетчики11 и 12, второй запоминающий блок 13и сумматор 14.Блок 3 суммирования, входящийв состав каждого канала обработкисигналов, изображенный на Фиг. 3,содержит блок 15 умножения, блок 16синхронизации, первый блок 17 памяти, счетчик 18 адреса, сумматор 19,и второго счетчиков, второго запоминающего блока и сумматора. В устройстве реализован параллельно-конвейерный метод обработки поступающегосигнала, что обеспечивает его некритичность к параметрам помех и высокую скорость обработки сигналов., 1 з.п.ф-лы, 6 ип. коммутатор 20, второй блок 21 памятии первый и второй регистры 22 и 23,Блок 5 выбора максимального сигнала, входящий в состав каждого канала обработки сигналов, изображенный на Фиг. 4, содержит первый, второй и третий регистры 24-26, блок 27сравнения, блок 28 синхронизации иэлемент 29 И.Устройство различения сигналов надюне произвольной помехи работаетследующим образом,Входной сигнап, представляющийсобой сумму полезного сигнала и помехи в виде к отсчетов Ь = Г,Ю,поступает на инФормационные входыблоков 2 корреляционной обработкисигнала всех. каналов обработки сигналов. Каждый отсчет входного сигналар ./Б представляет собой ш разрядныйдвоичный код и поступает на вход устройства одновременно с сигналом стробирования О, . Таким образом, имеемБ 1, - входной сигнал, Е = 1,К,Х -число базовых различаемых сигналовЯ; х = 1,Х, а Функционал плотностираспределения произвольной помехипредставлен в виде где Б - число гауссовских случайных ,процессов как с одинаковыми, так и различными корреляционными матрицами 0 Р, 1 и различными средними в.Блок 2 корреляционной обработки сигналов каждого канала обработки сигналов после приема входного сигнала У Формирует на выходе сигнал, пропорциональный смещенному коэфФициенту корреляции:получая тем самым значения х по (1); умножение значения х; на весовой коэффициент а получение суммы вида и й5 , а 1 , ах,. и сложение полученПф 1ного значения с коэФФициентом смещения 1 получая тем самым значения1 С1; по (4); нахождение максимума изх ; нахождение максимального1 Изначения иэ всех у; и макс хири д =. 1,Т, 1. = 1,Е,На диаграмме (Фиг.5) показан циклработы устройства, причем в каждомтакте диаграммы условно показановыполнение перечисленных операций,Первая операция осуществляетсяв блоках умножителей 9 -9 блока 2ккорреляционной обработки сигналакаждого канала обработки сигналовпоследовательно для каждой гауссовской компоненты полигауссового представления произвольной помехи, ВтоМрая операция ,Е а,7;,1,+ р; рсущестГ 1вляется в сумматоре 14 также последовательно для каждой гауссовской 30 компоненты полигауссового представления произвольной помехи, но со сдвигом на один такт синхронизации йо отношению к началу выполнения первой операции. Третья операции осуществляется в блоках 3 -3 суммиро вания,Четвертая - в накапливающем сумматоре каждого 1-го блока 3 суммирования, образованном сумматором 19, 4 О .коммутатором 20 и регистрами 22 и 23 со сдвигом на три такта относительно первой операции, Пятая операция осуществляется в блоке 5 выбора максимального сигнала со сдвигом на два 45 такта синхронизации относительно первой операции. Р 1 естая операция осуществляется блоком 1, сравнения по окончании четвертой и пятой операций. Операции 1-5 выполняются соответст 50 вующими блоками устройства последовательно Дпя каждой гауссовской компоненты, при этом выполнение различных операций совмещено во времени (со сдвигом каждой на один такт синхро- . низации) и результаты операций пере 55 даются из блока в блок, что обеспечивает конвейерный режим. При этом перечисленные операции во всех 1 каналах обработки и 1, блоках суммирования 3 -3 каждого канала осуществля 1 Ьются йараллельно. Таким образом, устройство в целом работает в параллельно-конвейерном режиме,Работа блоков синхронизации 8, 16и 28 поясняется с помощью временнойдиаграммы, представленной на Фиг. 6,Указанные блоки 8, 16 и 28 засинхрониэированы от тактового генератора 4и формируют управляющие и синхронизирующие импульсы, посредством которых организуется работа блока корреляционной обработки 2, блоков суммирования Зди блока 5 выборамаксимального сигнала в параллельно-конвейерном режиме, показанномна фиг, 5,Временные диаграммы по фиг, 6 показывают последовательности импульсов, Формируемых на соответствующихвыходах блоков синхронизации 8, 16и 28, а стрелками показана инициацияработы одного блока синхронизациидругим, а также порядок формирования и выдачи управляющих импульсовв соответствующих блоках синхронизацииеРассмотрим динамику работы устройства в целом с момента его включения,Работу устройства будем рассматривать по временным диаграммам, приведенным на Фиг. 6. Цифры на этих диаграммах соответствуют номерам выходов рассматриваемых блоков синхронизации 8, 16, 28,Отсчеты входного сигнала Пк, поступающие на информационные входыблоков 2 корреляционной обработкикаждого канала обработки сигналовс помощью блока 7 асинхронной запи-си, записываются в блок 6 -6 регистров по стробирующим импульсам, Блок 7асинхронной записи на выходах 1,2 - 1Формирует импульсы, которые последовательно поступают на .синхровходыблока 6.д-б к регистров, При записипоследнего Е-го отсчета первый входблока 7 асинхронной записи блокируется высоким уровнем импульса на 1-мвыходе, по которому также инициируется работа блока 8 синхронизации, Такая организация записи отсчетов вход"ного сигнала П к позволяет совместить ее во времени с дальнейшей обработкой и производить ее асинхроннопо отношению к тактовым импульсампо мере поступления отсчетов, На рре1596469 9менной диаграмме по фиг. 6 показаны два цикла работы устройства.После приема отсчетов входного сигнала Р в интервале й,на 1-ом выходе блока 7 асинхронной записи5 . появляется сигнал инициализации, который поступает на первый вход блока 8 асинхронизации и проходит на его первый выход. По этому сигналу происходит перезапись отсчетов вход. ного сигнала 11, иэ блока 6 -6 рех к гистров в блок 9 -9 к умножителей. С началом тактового интервала С . импульсы тактового гейератора 4 проходят на второй и четвертый выходы блока 8 синхронизации, По переднему фронту импульса со второго его выхода происходит запись значений отсчетов опорного сигнала Ч;1, первой гауссовской комйоненты полигауссового представления произвольной помехи, по" ступающих из первого запоминающего блока 10 на .вторые входы блока 9 -9т к умножителей, По заднему фронту им пульсов на четвертом выходе блока 8 синхронизации происходит увеличение на единицу содержимого первого счетчика 11, что обеспечивает выдачу отсчетов опорного сигнала 711,из первого запоминающего блока 10 для следующей гауссовской компоненты.В следующем тактовом интервале й импульсы тактового генератора 4 проходят на третий и шестой вьглоды блока 8 синхронизации, По переднему фронту импульсов с третьего выхода происходит выдача произведений 111 11;, полученных в течение предыдущего тактового интервала из блока 9-9 к умножителей в сумматор 14, Кроме того, на к+1 вход сумматора 14 по" ступает значение коэффициента смещения р; из второго запоминающего блока 13. В течение половины тактового периода осуществляется суммирование значений 1111;1, и р, по (1) и выдача результата х 1 на вьход блока 2 корреляционной обработки сигнала, С выдачей значений Ч;1, для последней гауссовской компоненты из первого запоминающего блока 10 последний разряд выходной шины этого блока устанавливается в нулевое состояние, что запрещает прохождение тактовых импульсов на четвертый выход блока 8 синхронизации. По переднему фронту импульса на втором его выходе происходит умно- жение вектора отсчетов входного сигнала 11 ня вектор отсчетов Ч;1, последней гауссовской компоненты в полигауссовом представлении произвольной помехи, после чего прохождениеимпульсов тактового, генератора 4 навторой выход блока 8 синхронизации(при условии отсутствия инициализирующего импульса на первом входеблока 7 асинхронной записи) запрещается, При наличии ннициирующего импульса на первом входе блока 7 асинхронной записи начинается цикл обработки следующего вектора отсчетов0 .,непосредственно за прошедшимциклом и прохождение импульса навторой выход блока 8 синхронизациине запрещается, По заднему фронтуэтого импульса и при нулевом уровнесигнала на третьем входе блока 8синхронизации в интервале времени Сначинается формирование сигнала напятом выходе блока 8 синхронизации,по которому первый счетчик 11 сбрасывается в исходное состояние, при котором на выходе первого запоминающего блока 10 вновь формируется вектор отсчетов Ч;1, для первой гауссовской компоненты. При этом сигнал натретьем входе возвращается в единичное состояние. По высокому уровнюимпульса на третьем выходе в моментвремени с импульс на пятом выходеблока 8 синхронизации заканчивается,При наличии на первом входе блока Ясинхронизации инициирующего импульсапроисходит перезапуск блока 2 корреляционной обработки сигнала для обработки следующего вектора отсчетоввходного сигнала И, При этом пофронту импульса на пятом выходе блока 8 синхронизации происходит выдача импульсов с его первого выхода,Следующии цикл обработки входногосигнала 111, в блоке 2 корреляционнойобработки сигнала аналогичен описанному циклу,Работа блоков 3 -3суммированияпроисходит следующйм образом.На первый вход блока 16. синхронизации поступает импульс с соответствующего выхода блока 2 корреляционной обработки сигнала. Этот импульсразрешает прохождение импульсов тактового генератора 4 (с момента С )на первый и третий выходы блока 16синхронизации. По импульсам с первого выхода этого блока осуществляетсяперепись значений х, с выхода бло 1596469 12ка 2 корреляционной обработки сигнала на первый вход блока 15 умножения и одновременно с этим запись коэффициента а с выхода первоГоирблока 17 памяти на второй вход блока 15 умножения, который осуществляет операцию перемножения полученных значений. По заднему фронту импульсов с третьего выхода блока 16 синхронизации прорсходит увеличение на единицу содержимого счетчика 18 адреса, что обеспечивает выдачу из первого блока 17 памяти следующего значения коэффициента ар. В следующем тактовом интервале (С ) импульсы тактового генератора 4 проходят на второй выход блока 16 синхронизации, 11 о этому сигналу происходит выдача результата перемножения х. а нае вход сумматора 19. На другом его входе в этот момент времени действуег нулевой сигнал с регистра 22, который в момент включения устройства автоматически был установлен в это. состояние, В течение половины периода тактовых импульсов И ) сумматор 19 осуществляет операцию суммирования и передает результат на вход второго регистра 23 и на первый вход коммутатора 20, Сигнал на пятом выходе блока 16 синхронизации при включении устройства имеет нулевое значение до окончания импульса на втором выходе блока 16 синхронизации при умножении значения х;, соответству.- ющего первой гауссовской компоненте н полигауссовом представлении произвольной помехи, По этому сигналу . коммутатор 20 передает на вход первого регистра 22 значение о,из второго блока 21 памяти. По заднему фронту импульса со второго выхода блока 16 синхронизации сигнал на его пятом выходе устанавливается в единичное состояние, чем обеспечивается передача результата суммирования в первый регистр 22 через коммутатор 20, С выдачей значения последнего коэффициента а 1 из первого блока 17 памяти запрещается прохождение тактовых импульсов на третий выход блока 16 синхронизации. По переднему Фронту импульса на первом его выходе и момент С, происходит умножение последнего значения сигнала на послед нее значение коэффициента а, после чего прохождение импульсов тактового генератора 4 на первый выход блока 16 синхронизации (при отсутствии сигнала на его первом управляющем входе)запрещается, При наличии сигнала напервом управляющем входе блока син хронизации (с момента 1 ) начинаетсяследующий цикл обработкй непосредственно за предыдущим и прохождениетактовых импульсов с первого и третьего выходов блока 16 синхронизацииразрешается. По заднему фронту импульса с его первого входа и при нулевомуровне сигнала на третьем выходе, (в интервал времени 1) начинаетсяФормирование импульса на четвертомвыходе блока 16 синхронизации, по которому счетчик 18 адреса сбрасывается в исходное состояние и обеспечивает получение на выходе первого блока 17 памяти значения первого коэффициента ар, При этом сигнал на третьем входе блока 16 синхронизации воз"вращается в единичное состояние, Повысокому уровню сигнала на его втором выходе (в момент С ) импульс сброса заканчивается и начинается следующий цикл работы каждого блока 3 суммирования. По заднему фронту импульсана втором выходе и низком уровне начетвертом выходе блока 16 синхронизации (в интервал времени й ) происходит перепад сигнала на его пятомвыходе в нулевое состояние, по которому коммутатор 20 переходит в режим.передачи информации со своего второго входа, В результате значение коэффициента смещения (, иэ второгоблока 21 памяти передается на входпервого регистра 22 (в момент й) и 40по импульсу со второго выхода блока16 синхронизации это значение записывается в первый регистр 22 и соответственно поступает с его выхода навторой вход сумматора 19 В сумматоре 19 (в течение половины периода у)осуществляется суммирование пе.ремноженных значении х;со значе-нием коэффициента смещения д,., С началом этого же тактового интервала(момент й) на шестом выходе блока16 синхронизации формируется импульс,по которому осуществляется сброс первого регистра 22 и перезапись результата суммирования (значение у по(4) во второй регистр 23 с передачейего на выход блока суммирования 3,Как видно из временной диаграммы,последние операции в блоках 3 -3суммирования (моменты времени й1159646 1 Зи г. ) совмещены во времени с операциями умножения в блоке 15 и суммирования в .блоке 19 следующего циклаобработки,Работа блока 5 выбора максимального сигнала осуществляется следующим образом. На первый вход блока28 синхронизации поступает сигналс соответствующего выхода блока 2 кор реляционной обработки сигнала. Лопереднему фронту импульсов с выходатактового генератора 4 и при наличиисигнал на первом входе блока 28синхронизации значение сигнала х. 15Ьс информационного вттхода блока 2корреляционной обработки сигнала(в момент ) записывается в первыйрегистр 24 по импульсу со второговыхода блока 28 синхронизации. Этотже импульс поступает на второй(инвертирующий) вход элемента 29 И. В этотже интервал времени (,т) с первоговыхода блока 28 синхронизации одновременно формируется импульс, который 25поствпает на блок 27 сравнения и блокирует его при записи первого значения х . в каждом цикле, что обеспе 1 йчивает независимо от значения х, пе 1резались его с выхода первого ре- угистра 24 во второй регистр 25 по заднему фронту тактовых импульсов (в момент с; ), В следующем такте И) пофронту импульса со второго выхода блока 16 синхронизации происходит сбросимпульса на первом его выходе в нулевое состояние, а также запись в первь 1 й регистр 24 следующего зчачениях. , В течение половины периода, так 1 Птовых импульсов (в интервал време 4 йни й) в блоке 27 сравнения осуществляется сравнение двух значений х;,находящихся на его входах. Если значение х на выходе первого регистанра 24 больше значения на выходевторого регистра.25, то блок 27 сравнения (который анализирует также знаки сравниваемых чисел) вырабатываетна своем выходе импульс, по которомупроисходит перезапись большего значения во второй регистр 25. Если50значение х; на выходе регистра 24меньше или равно значению х; на выходе регистра 25, то блок 27 сравнз -ния импульс перезаписи не формирует,а во втором регистре 25 сохраняетспрежнее значение. Таким образом происходит выбор максимального значениях; из х; ). Блок 28 синхронизации 914в каждом цикле отслеживает" нужноеколичество значений х . Поэтому припоступлении на вход первого регистра 24 последнего значения х, н после сравнения поступившего значенияс предпоследним, блок 28 синхронизации (в момент Ст) вырабатывает натретьем выходе импульс, по которомуосуществляется перезапись значениях; = макс 1 х )в третий регистр 26,сброс регистров 24 и 25 в нулевоесостояние и передача максимальногозначения х . на выходе блока 5 выбо 1 Ьра максимального сигнала,Таким образом, осуществляетсявыполнение первых пяти операций иэперечисленных вьге в блоке 2 корреляционной обработки сигнала, блокахсуммирования 3 - и блоке 5 выбораТмаксимального сигнала в кажпом канале обработки сигналов, После каждогоцикла работы на соответствующих входах блока 1 сравнения имеются значения у. и макс х, В то время какпроисходит выполнение следующегоцикла работы в каждом канале обработки сигналов, блок 1 сравнения осуществляет выделение максимальногоиз 1(т+1)ттт разрядных двоичных чисел,ттредставленных параллельным кодом.В результате после каждого циклаработы всего устройства на выходахВ,Б -8имеется информация о поступлений на вход устройства соответствующего сигнала из различаемых.Гложность практической реализациипредлагаемого устройства не зависитот числа исходных гауссовских случайных процессов, что отличает егоот прототипа и обеспечивает его работоспособность в сложном комплексепомех при высокой гибкости к изменению их параметров и при высокой скорости обработки. Формула изобретения 1, Устройство. различения сигналов на фоне произвольной помехи, содержащее каналы обработки сигналов, первые выходы каждого иэ которых соединены с первыми входами блока сравнения, выхопы которого являются выходами устройства, информационный вход которого соединен с информационными входами каналов обработки сигналов, а каждый из каналов обработки сигналов содержит блок корреляционной обработ 15 15 ки сигнала и блоки суммирования выФ ходы которых являются первыми выходами канала обработки сигналов, информационным входом которого является инФормационный вход блока корреляционной обработки сигнала, первый и второй выходы которого подключены к входам блоков суммирования, о т л ич а ю щ е е с я тем, что, с целью повыщения верн сти приема в условиях действия помех с изменяющимися параме грами, введен тактовый генератор, выход которого соединен с тактовыми входами каналов обработки сигналов, вторые выходы которых подключены к вторым входам блока сравнения, причем управляющие входы каналов обработки сигналов соединены с управляющим входом устройства, а в каждый канал обработки сигналов введен блок выбора максимального сигнала, выход которого является вторым выходом канала обработки сигналов, тактовый вход которого соепннен с тактовыми входами блоков суммирования, блока корреляционной обработки сигнала и блока выбора максимального сигнала, сигнальные входы которого подключены к выходам блока корреляционной обработки сигнала.2. Устройство по п. 1, о т л ич а ю щ е е с я тем, что блок корреляционной обработки сигнала содержит блок регистров, блок асинхронной9 б 469 1 Ь записи, блок синхронизации, блок умножителей, первый запоминающий блок, первый и второй счетчики, второй запоминающий блок и сумматор, первые входы которого соединены с выходами блока умножителей, первый, вторые и третий входы которого подключены соответственно к выходу первого запоминающего блока, первым выходом блока синхронизации и выходом блока регистров, первые входы которого соединен с соответствующими выходами блокаасинхронной записи, первый вход которого является управляющим входом 15блока корреляционной обработки сигнала, информационным входом, первым и вторым выходами и тактовым входом которого являются соответственно второй вход блока регистров, выход сумматора, второй выход блока синхронизации и первый вход блока синхронизации, третьи и четвертые выходы которого подключены к входам соответственно первого и второго счетчиков, выходы которых подключены к входам первого и второго запоминающих блоков соответственно, причем выход второго запоминающего блока подключен к второму входу блока синхронизации, третий вход которого соединен с соответствующими выходами блока асинхронной записи, второй вход которого подключен к соответствующему выходу блока синхронизации.

СмотретьЗаявка

4620166, 14.12.1988

КАЗАНСКИЙ АВИАЦИОННЫЙ ИНСТИТУТ ИМ. А. Н. ТУПОЛЕВА

ЧАБДАРОВ ШАМИЛЬ МИДХАТОВИЧ, ФАЙЗУЛЛИН РАШИД РОБЕРТОВИЧ, ВОЛКОВ АНДРЕЙ НИКОЛАЕВИЧ, НАДЕЕВ АДЕЛЬ ФИРАДОВИЧ

МПК / Метки

МПК: H04B 15/00

Метки: помехи, произвольной, различения, сигналов, фоне

Опубликовано: 30.09.1990

Код ссылки

<a href="https://patents.su/10-1596469-ustrojjstvo-razlicheniya-signalov-na-fone-proizvolnojj-pomekhi.html" target="_blank" rel="follow" title="База патентов СССР">Устройство различения сигналов на фоне произвольной помехи</a>

Предыдущий патент: Способ радиосвязи с подвижными объектами

Следующий патент: Устройство для контроля чувствительности радиоприемника

Случайный патент: Устройство для регулирования скорости электродвигателя