Однобитовый процессор программируемого контроллера

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1476464

Авторы: Витковский, Склема

Текст

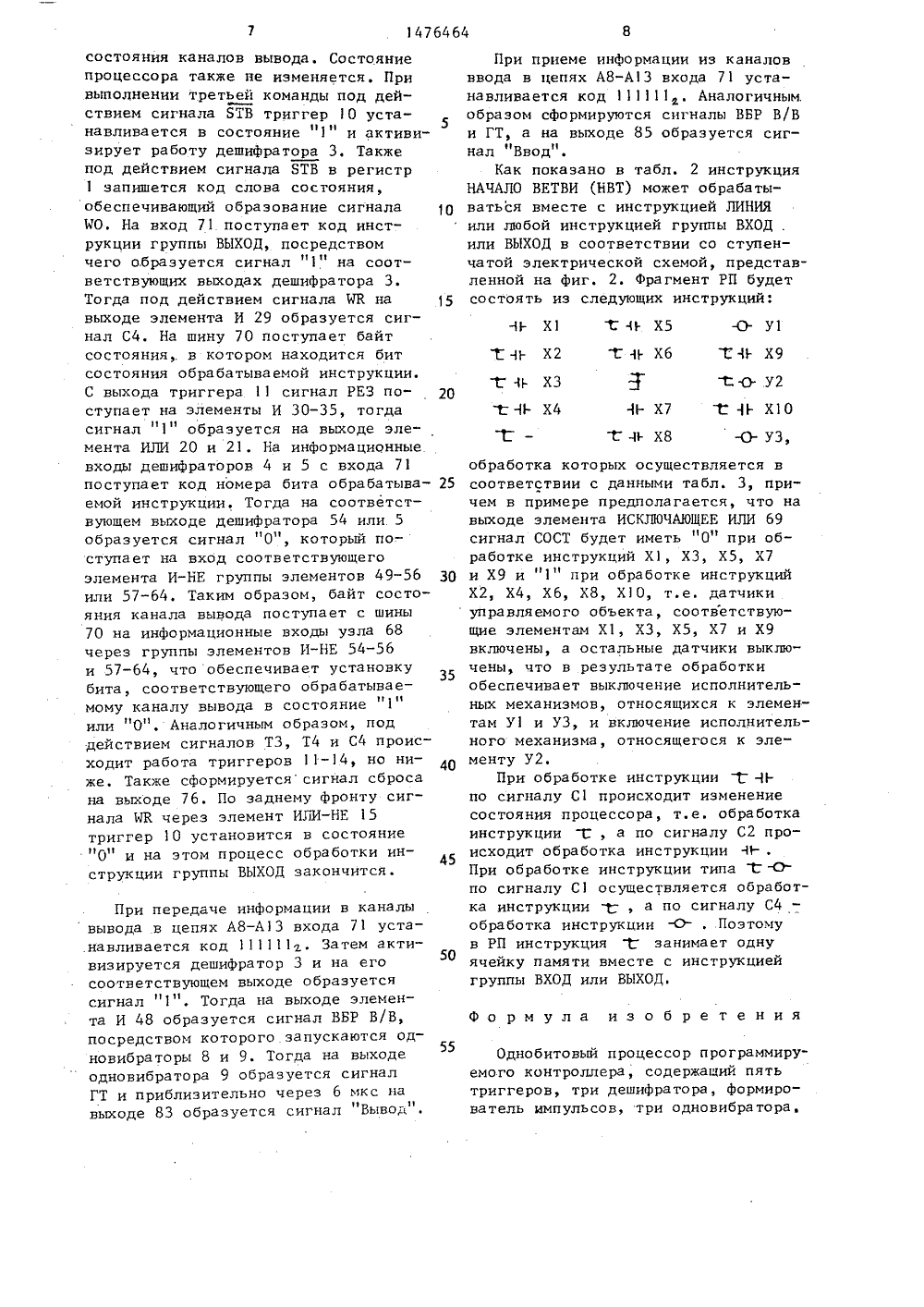

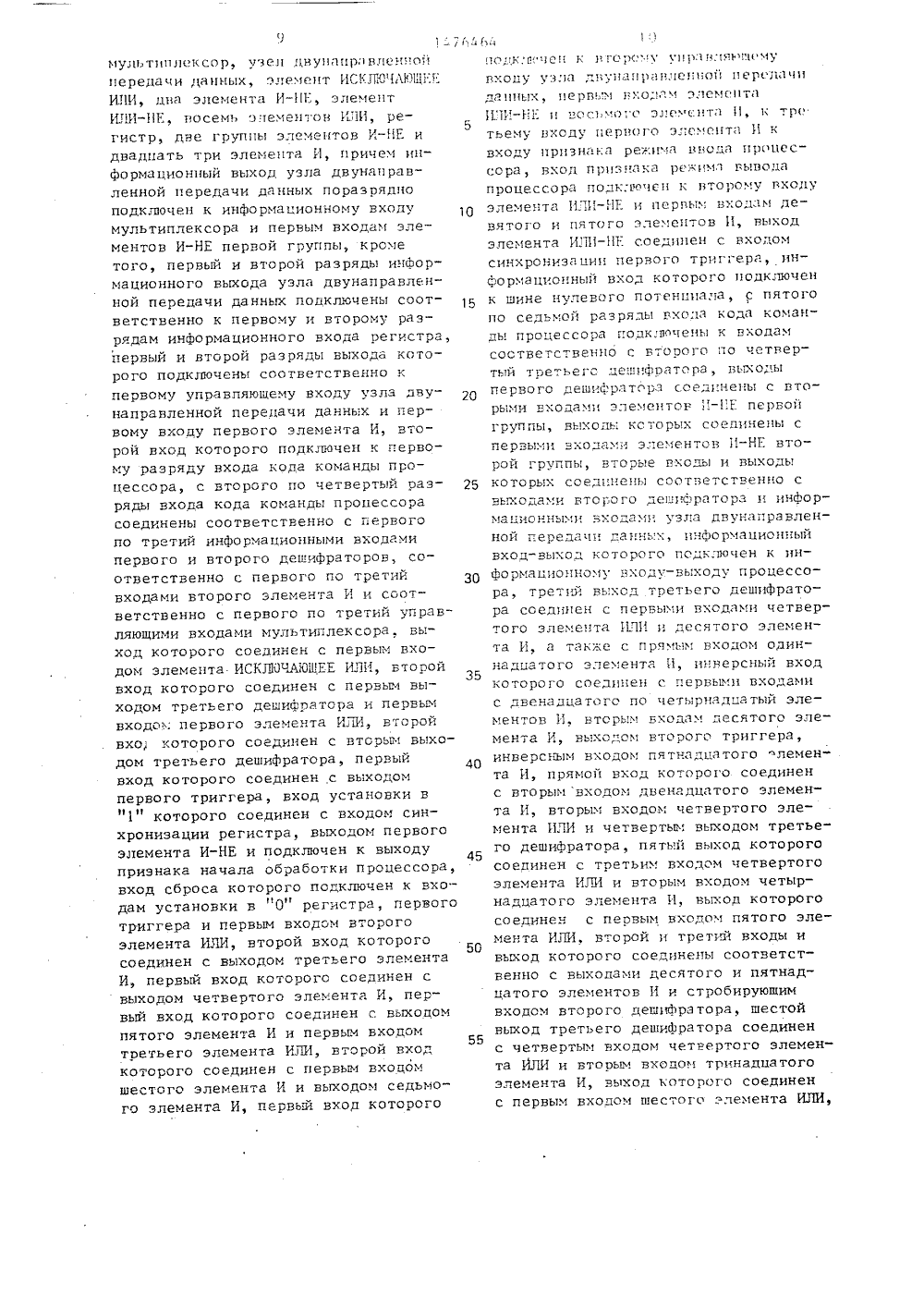

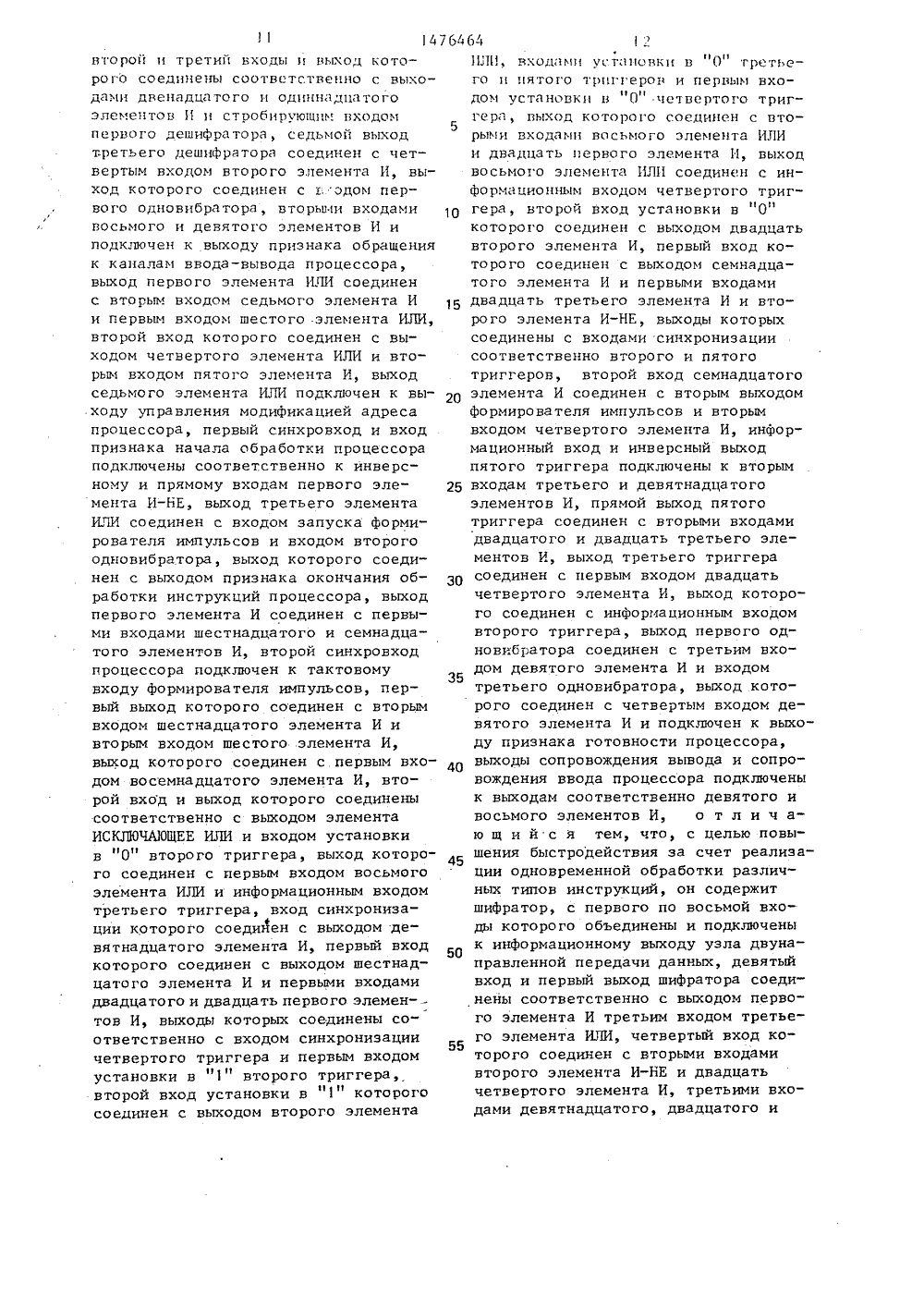

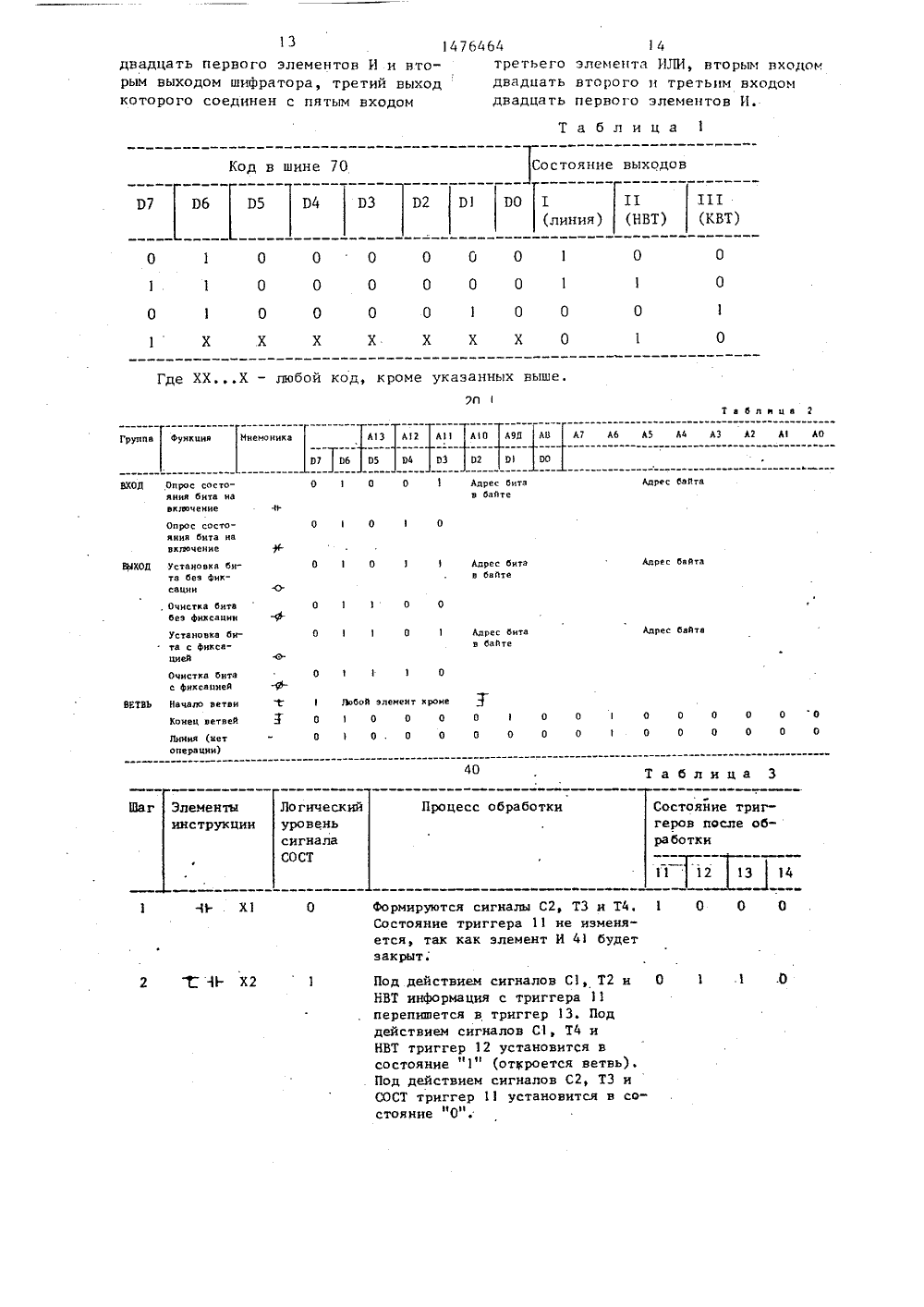

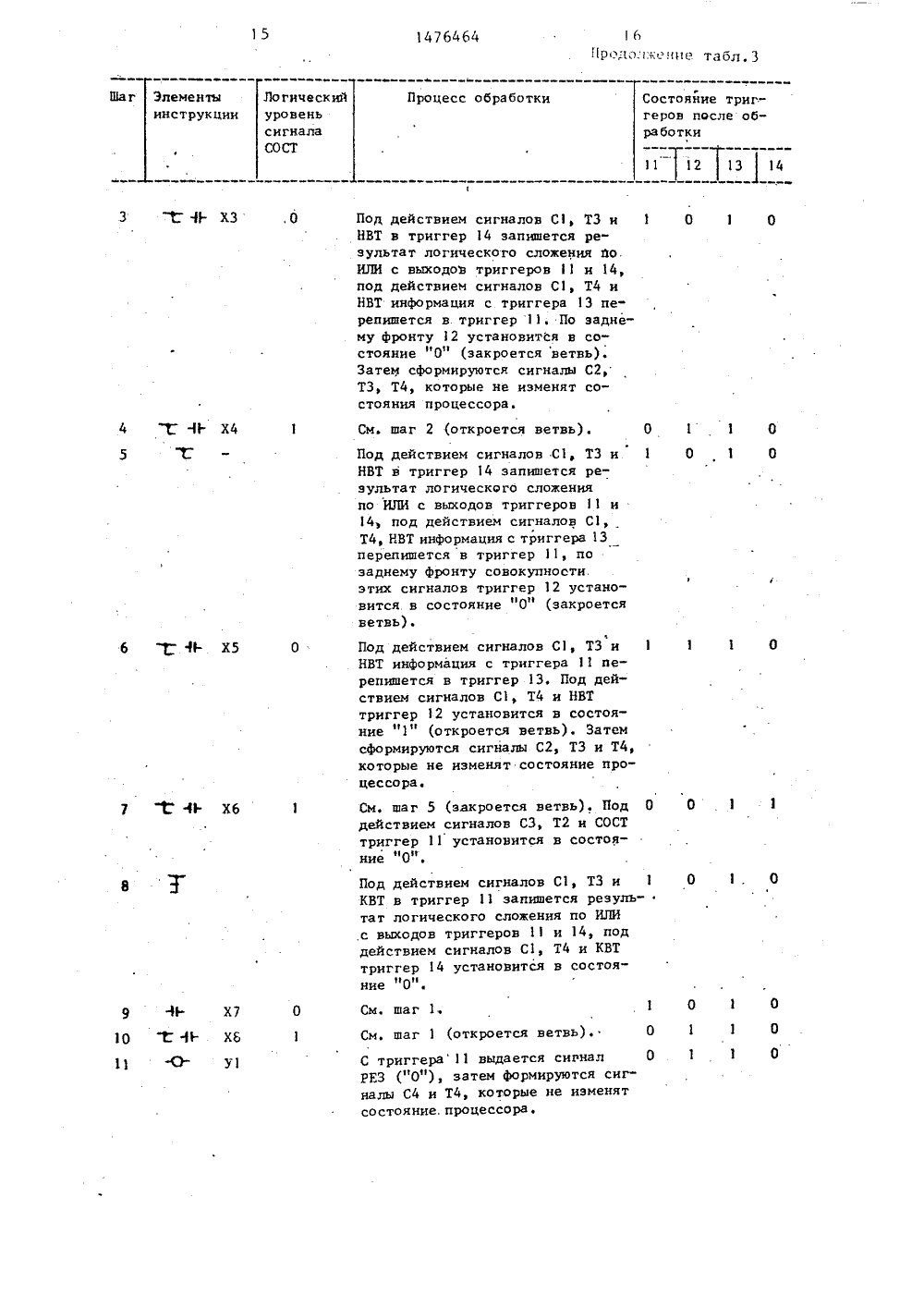

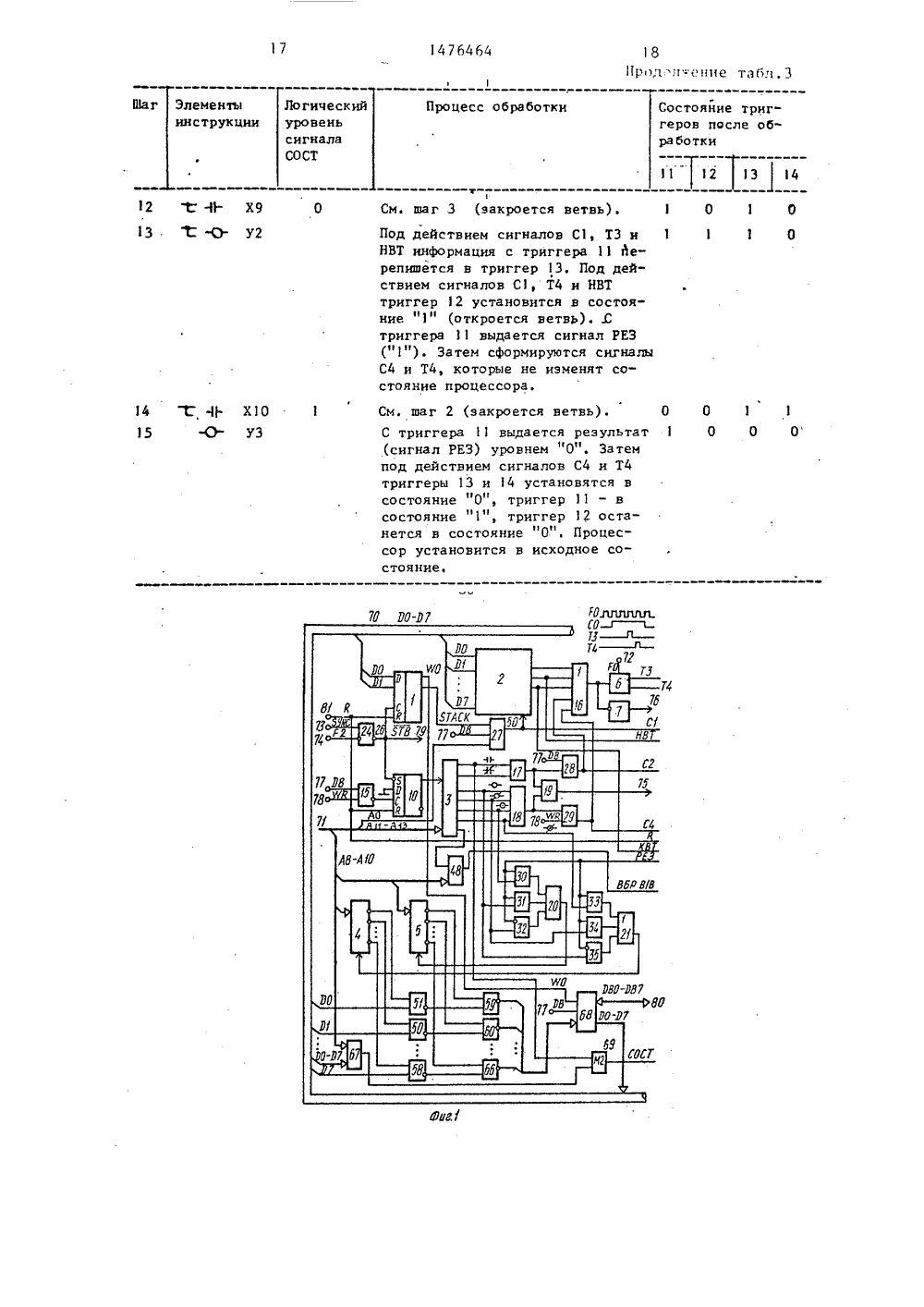

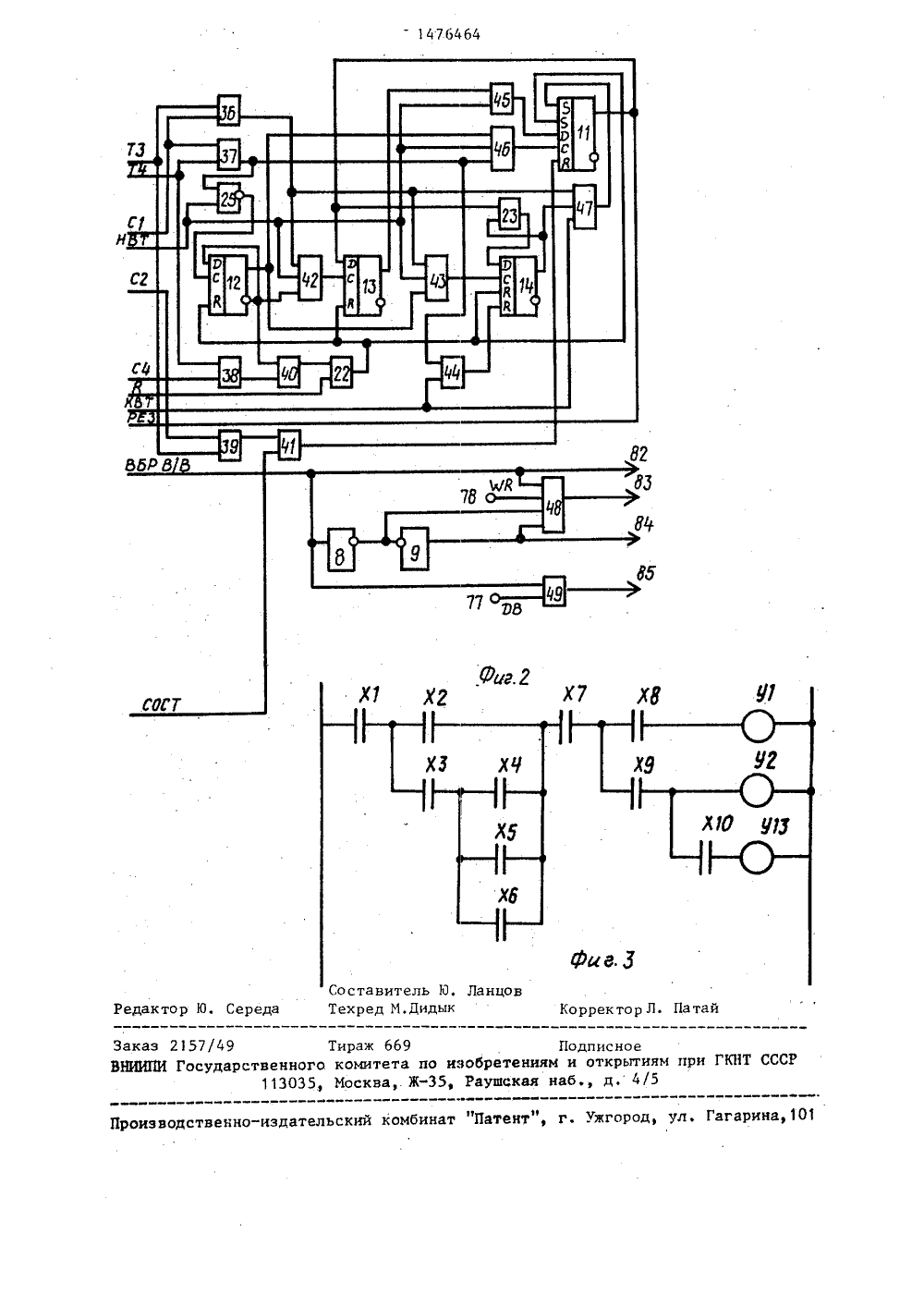

0)ОЗ СОВЕТСКИХ ОЦИАЛИСТИЧЕСКИРЕСПУБЛИК 9) (И) А 5) 4 С 06 Р 9/00, С 05 В ПИСАНИЕ ИЗОБРЕТЕНИЯ АВТОРСКОМУ СВ ЕЛЬСТВ овск 2 ПРОГРАММИк вычис чено дл 2 1и их групп в упенчатои элект есИзобрете ельной техе относится к вычи ке и предназначено ограммируемых контр ретения - повышениеа счет реализации одработки различных тип о строенияов (ПК) .В ПК пр лема работы управляемо- ется в виде инструкющих последователь- водящую ступенчатую хему управляемого вном ступенчатая элекстроится из элеменВЕТВЬ (1 АЧАЛО ВЕТВИ, которые .образуют опреукции. К элементам гра зад авл го объект ций, пред ность, во электрическую объекта: В осн трическая схем тов ВХОД, ВЫХО КОНЕЦ ВЕТВЕ 11), д ленные конст е Х ормально разомкнутыемкнутые контакты,В ОД относятсяили нормально з соответствующие нопке, пХОД - оации и да тчику, клементам В реключателю, к э мотка реле, ламп т.п., элементы В зовывать дизъюнк очка индикЕТВЬ позво)ии злемен а)яют о тов ВХ ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(57) Изобретение относитсятельной технике и предназн построения программируемых контроллеров, Целью изобретения являетсяповышение быстродействия. Устройствосодержит регистр, шифратор, дешифраторы, Формирователь импульсов, одновибраторы, триггеры, элемент ИЛИ-НЕ,элементы ИЛИ, элементы И-НЕ, элементы И, две группы элементов И-НЕ,мультиплексор, узел двунаправленнойпередачи данных, элемент ИСКЛЮЧАЮ 1 ЦЕЕ ИЛИ. Цель изобретения достигается за счет реализации одновременнойобработки различных инструкций (например, "Начало ветви 1 и Вход или"Выход" ). 3 ил., 3 табл. кои схеме.Цель изоб быстродеиствия з новременной об овинстр.укций,На фиг. 1 и 2 представлена функциональная схема предлагаемого процессора; на Фиг. 3 - ступенчатаяэлектрическая схема, которую можетобрабатывать данный процессор.Процессор содержит регистр 1,шифратор 2, дешифратор 3-5, Формирователь 6 импульсов, одновибраторы7-9, триггеры 10-14, элемент ИЛИ-НЕ15, элементы ИЛИ 16-23, элементыИ-НЕ 24 и 25, выход 26 элемента И-НЕ24, элементы И 27-49, выход 50 элемента И 27, две группы элементовИ-НЕ 51-58 и 59-66, мультиплексор67, узел 68 двунаправленной передачи1 47 6464 Составитель Ю. Ланцоведактор Ю. Сер Техред М,Дидык Корректор Л. Патай еда аз 2157/49 Тираж 669 ПодписноеГосударственного. комитета по изобретениям и открьггиям при ГКНТ СССР113035, Москва,. Ж, Раушская наб., д. 4/5 НИИПИ роизводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагаринаданных, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 69,шину 70 данных (ПО-П 7), вход 71 кодакоманды (АО, А 8-А 13), второй синхровход 72 (РО), вход 73 признака начала обработки (БУМС), первый синхровход 74 (Г 2), выход 75 управлениямодификацией адреса, выход 76 признака окончания обработки инструкций, вход 77 признака режима ввода(РВ), вход 78 признака режима вывода(1 К), выход 79 признака начала обработки, информационный вход-выход 80,вход 81 сброса, выход 82 признакаобращения с каналом ввода-вывода,выход 83 сопровождения вывода, выход84 готовности и выход 85 сопровождения ввода,Регистр 1 представляет собой микросхему типа К 155 ТМ 8. Формирователь6 импульсов состоит из пересчетнойсхемы (счетчика) и элементов И, чтообеспечивает выделение, например;третьего и четвертого импульсов изпоследовательности импульсов ГО поддействием запускающего сигнала СО(см. временные диаграммы работы фор-мирователя, изображенные над ним).Узел 68 двунаправленной передачиданных представляет собой переключатель шин с тремя состояниями навыходах и может быть выполнен надвух микросхемах типа К 589 АП 16. Мультиплексор 67 обеспечивает выборкуодного бита из байта, передаваемогопо шине 70 РО-Р 7, по адресу, указанному кодом в шине А 8-А 10. Одновибраторы 8 и 9 обеспечивают формированиеимпульсов длительностью примерно 6и 8 мкс соответственно. Шифратор 2может быть выполнен на микросхеметипа К 556 РТ 4. В табл. 1 приведенпример кодирования шифратора 2, позволяющий реализовать одновременнуюобработку инструкции НАЧАЛО ВЕТВИи ВХОД или ВЫХОД,Входы и выходы элементов процессора имеют следующее назначение, Сигнал ЕО на входе 72 обеспечивает образование на выходе формирователя 6 двух импульсов ТЗ и Т 4 длительностью по 100 нс. Синхроимпульс Р 2 на входе 74 и сигнал БУМС (сигнал начала цикла обработки) на входе 73 обеспечивают образование 1 а выходе элемента И-НЕ 24 импульса ЯТВ, необходимого для 5 О 15 20 25 30 35 40 45 50 55 стробирования работы элементов процессора,Сигнал на входе 77 формируетсяпри появлении информации в шине 70ПО-П 7 в цикле считывания.Сигнал ЫК на вход 78 поступаетпри появлении информации в шине 70в цикле записи.Сигнал К на вход 81 поступаетпри включении питания ПК и обеспечивает установку элементов процессорав исходное состояние.Сигнал сброса на выходе 76 образуется по завершении обработки инструкции группы ВХОД, ВЫХОД или инструкции КОНЕЦ ВЕТВЕЙ, линия.Сигнал управления модификациейадреса на,выходе 75 образуется, когда на входе 71 устанавливается кодкоманды, соответствующий обрабатываемой инструкции группы ВХОД или ВЫХОД.Сигнал ГТ на выходе 84 готовностиобразуется при передаче информациис шины 70 ПО-Р 7 на вход-выход 80ПВО-ПВ 7 и при передаче информациис входа-выхода 80 на шину 70 в циклеобмена информацией ПК с каналамиввода-вывода.Сигнал ВБР В/В на выходе 82 формируется при обращении ПК к каналамввода-вывода и активизирует их работу.Сигнал вывод на выходе 83 формируется при выдаче информации с ПК в каналы вывода и обеспечивает записьинформации, например, в регистры модулей вывода.Сигнал "Ввод" на выходе 85 формируется при приеме информации с каналов ввода и обеспечивает синхронизацию их работы,Сигнал ЧО с соответствующего разряда выхода регистра 1 активизируетработу узла 68 по передаче информации с его информационных входов навход-выход 80.Сигнал БТАСК с соответствующегоразряда выхода регистра 1 обеспечивает формирование управляющего сигнала в шифратор 2 в цикле поступления кода инструкции РП в шину 70.Сигнал С 1 с выхода элемента И 27обеспечивает работу элементов процессора при обработке инструкциигруппы ВЕТВЬ,Сигнал С 2 с выхода элемента И 28обеспечивает работу элементов про 5/цессора нри обработке инструкциигруппы ВХОД.Сигнал С 4 с выхода элемента И 29обеспечивает работу элементов процессора при обработке инструкциигруппы ВЫХОД.Импульсы ТЗ и Т 4 с выходов формирователя 6 импульсов обеспечиваютпоследовательность срабатывания элементов процессора.Сигнал РЕЗ с выхода триггера 11обуславливает результат обработкипоследовательности инструкций РП,образующих одну логическую цепь.Сигнал СОСТ с выхода элементаИСКЛЮЧАЮЩЕЕ ИЛИ 69 обуславливаетрезультат обработки инструкции группы ВХОД.Сигнал СОСТ с выхода элементаИСКЛЮЧАЮЩЕЕ ИЛИ 69 обуславливает результат обработки инструкции группыВХОД.Сигнал, образующийся на выходемультиплексора 67, соответствует состоянию канала ввода и называетсябитом состояния канала,Сигнал, образующийся на выходеэлемента ИЛИ 20, обеспечивает установку в состояние "1" бита обрлбаты -ваемого канала вывода, а сигнал,образующийся на выходе элемента ИЛИ21, обеспечивает установку бита обрабатываемого качала вывода в состояние н 0.Процессор работает следующим образом.После включения питания на вход81 поступает импульс К, обеспечивающий установку в состояние нОп регистра 1, триггеров 10, 12-14 и установку в состояние "1" триггера 11.Обработка инструкций РП занимаетразное время в зависимости от группыинструкции. В табл. 2 представленыинструкции, обрабатываемые процессором, При этом инструкции НАЧАЛО ВЕТВИ (НВТ) может обрабатываться вместес инструкцией ЛИНИЯ или любой инструкцией группы ВХОД или ВЫХОД,Обработка инструкции КОНЕЦ ВЕТВЕЙосуществляется за одну команду ПК.Под действием сигнала БТВ с выходаэлемента И-НЕ 24 в регистр 1 записывается код слова состояния обеспечивающий образование сигнала 5 ТАСК.Когда на шину 70 поступает старшийбайт кода инструкции КОНЕЦ ВЕТВЕЙ,то в цепи АО на входе 71 будет "1". 76464ад действием сигнала ПВ по цепи 77на выходе элемента И 27 формируетсясигнал С 1, активизирующий работушифрлторл 2. Нл третьем выходе шифрлторл 2 образуется спгнлл КВТ, Посредством сигнала КВТ нл выходе элемента ИЛИ 1 б образуется сигнал СО,запускающий Формирователь б. Тогдапосредствам импульсов ТЗ, Т 4 и сигналов КВТ и С срлблтывлют триггеры11 - 14. По . заднему фронту сигнлллСО сработает адновибратор 7, навыходе 76 которого формируется сиг нал сброса . Нл этом процесс обработЭки данной инструкции заканчивается.Обработка инструкции ЛИ 1 ИЯ происходит аналогична.Обработка инструкции группы ВХОДасушествляется на две команды ПК,При выпалении первой команды кадинструкции считывается из памятиПК, при этом состояние процессоране изменяется. Прн выполнении второй 25 команды под действием сигнлла ВТВтриггер 10 устанавливается в состояние1 и активизирует работу дешифратарл 3. На вход 71 поступает кадинструкции группы ВХОД, посредством ЗО чего на соответствующем выходе дешифратора 3 образуется сигнал ч-.-) . Тогда под действием сигнала ЭБ на выходеэлемента И 28 образуется сигнал С 2.На шину 70 поступает байт состояния,в котором находится бпт состояния 35обрабатываемой инструкции. На управ -ляющие входы мультиплексора 67 поступает кад намерл бита обрабатываемой инструкции, тогда нл выходе муль типлексара 67 образуется бит состояния канала ввода, л на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 69 - сигнал СОСТ.Аналогичным образом сформируютсяимпульсы ТЗ и Т 4, Посредством сигна лов ТЗ, Т 4, СОСТ и С 2 обеспечиваетсяработа триггера 11, Также сформируется сигнал сброса нл выходе 76. Позаднему фронту сигнала ПВ через элемент ИЛИ-НЕ 15 триггер 1 О установится в состояние 0. На этом процессобработки данной инструкции закон.читсяОбработка инструкции группы ВЫХОДосуществляется на три команды ПК.При выполнении первой камлнды код 55инструкции считывается из памяти ПК,при этом состояние процессора не изменяется, При выполнении второй команды из памяти ПК считывается байтсостояния каналов вывода, Состояние процессора также не изменяется. При выполнении третьей команды под действием сигнала БТВ триггер 1 О устанавливается в состояние "1" и активизирует работу дешифратора 3. Также под действием сигнала БТВ в регистр 1 запишется код слова состояния, обеспечивающий образование сигнала 1110. На вход 71 поступает код инструкции группы ВЫХОД, посредством чего образуется сигнал "1" на соответствующих выходах дешифратора 3. Тогда под действием сигнала АЖ на выходе элемента И 29 образуется сигнал С 4. На шину 70 поступает байт состояния, в котором находится бит состояния обрабатываемой инструкции, С выхода триггера 11 сигнал РЕЗ поступает на элементы И 30-35, тогда сигнал "1" образуется на выходе элемента ИЛИ 20 и 21. На информационные входы дешифраторов 4 и 5 с входа 71 поступает код номера бита обрабатываемой инструкции. Тогда на соответствующем выходе дешифратора 54 или 5 образуется сигнал "0", который поступает на вход соответствующего элемента И-НЕ группы элементов 49-56 или 57-64, Таким образом, байт состояния канала вывода поступает с шины 70 на информационные входы узла 68 через группы элементов И-НЕ 54-56 и 57-64, что обеспечивает установку бита, соответствующего обрабатывае 11 11 мому каналу вывода в состояние 1 или "0", Аналогичным образом, под действием сигналов Т 3, Т 4 и С 4 происходит работа триггеров 1 1 - 1 4 , но ниже . Также сформируетсясигнал сброса на выходе 7 6 . По заднему фронту сигнала 1 Ж через элемент ИЛ 4-НЕ 1 5 триггер 1 0 установится в состояние " 0" и на этом процесс обработки инс трук ции группы ВЫХОД закончится . При передаче информации в каналы вывода в цепях А 8-А 13 входа 71 уста.навливается код 1111111, Затем активизируется дешифратор 3 и на его соответствующем выходе образуется сигнал "1". Тогда на выходе элемента И 48 образуется сигнал ВБР В/В 1 посредством которого. запускаются одновибраторы 8 и 9. Тогда на выходе одновибратора 9 образуется сигнал ГТ и приблизительно через 6 мкс на11выходе 83 образуется сигнал Вывод". При приеме инФормации из каналовввода в цепях А 8-А 13 входа 71 устанавливается код 111111. Аналогичным.образом сформируются сигналы ВБР В/Ви ГТ, а на выходе 85 образуется сигнал 11 ВводКак показано в табл, 2 инструкцияНАЧАЛО ВЕТВИ (НВТ) может обрабатываться вместе с инструкцией ЛИНИЯили любой инструкцией группы ВХОД .или ВЫХОД в соответствии со ступенчатой электрической схемой, представленной на фиг. 2. Фрагмент РП будет 15 состоять из следующих инструкций:.1- Х 2 Е + Х 6 Е -Н- Х 9С 1 Ь ХЗ :О- У 220 1:-1 Ь Х 4 -11- Х 7 й Ь Х 10С - СФ Х 8 -О- УЗ,обработка которых осуществляется в 25 соответствии с данными табл. 3, причем в примере предполагается, что навыходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 69сигнал СОСТ будет иметь "0" при обработке инструкций Х 1, ХЗ, Х 5, Х 7 30 и Х 9 и "1" при обработке инструкцийХ 2, Х 4, Х 6, Х 8, Х 10, т.е. датчикиуправляемого объекта, соответствующие элементам Х 1, ХЗ, Х 5, Х 7 и Х 9включены, а остальные датчики выключены, что в результате обработкиобеспечивает выключение исполнительных механизмов, относящихся к элементам У 1 и УЗ, и включение исполнительного механизма, относящегося к эле менту У 2.При обработке инструкциипо сигналу С 1 происходит изменениесостояния процессора, т.е. обработкаинструкции -1:-, а по сигналу С 2 про исходит обработка инструкции 11- .При обработке инструкции типа С-Опо сигналу С 1 осуществляется обработка инструкции , а по сигналу С 4обработка инструкции 3-, Поэтомув РП инструкция - занимает однуячейку памяти вместе с инструкциейгруппы ВХОД или ВЫХОД.Формула изобретенияОднобитовый процессор и рограммируемого контроллера, содержащий пять триггеров, три дешифратора, формирователь импульсов, три одновибратора, мультиплексор, узел двунаправленной передачи данных, элемет ИСКЛЮИЮЦ 1.1. ИЛИ, цна элемента ИЕ, элемент ИЛИ-НЕ, восемь эементав 1 ПИ, регистр, цве группы элементов ИЕ и двадцать три элемента И, причем информационный выход узла двунаправленной передачи данных поразрядно подключен к информационному входу мультиплексора и первым входам элементов И-НЕ первой группы, кроме того, первый и второй разряды информационного выхода узла двунаправленной передачи данных подключены соответственно к первому и второму разрядам информационного входа регистра, первый и второй разряды выхода которого подключены соответственно кпервому управляющему входу узла двунаправленной передачи данньх и первому входу первого элемента И, второй вход которого подключен к первому разряду входа кода команды процессора, с второго по четвертый разряды входа кода команды процессора соединены соответственно с первого по третий информационными входами первого и второго дешифратаров, соответственно с первого по третий входами второго элемента И и соответственно с первого по третий управляющими входами мультиплексора, выход которого соединен с первым входом элемента ИСЕЛЮЧАЮШЕЕ ИЛИ, второй вход которого соединен с первым выходом третьего дешифратара и первым входс.; первого элемента ИЛИ, второй вхо которого соединен с вторым выходом третьего дешифратора, первый вход которого соединен с выходом первого триггера, вход установки в "1" которого соединен с входом синхронизации регистра, выходом первого элемента И-НЕ и подключен к выходу признака начала обработки процессора, вход сброса которого подключен к входам установки в "0регистра, первого триггера и первым входам второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И, первый вход которого соединен с выходом четвертого элемента И, первый вход которого соединен с выхоцом пятого элемента И и первым вхацам третьего элемента ИЛИ, второй вход которого соединен с первым вхоцом шестого элемента И и выхацом седьмого элемента И, первый вход которого7610 синхронизации первого триггера, информационный вход которого подключенк шине нулевого потенциала, с пятогопо седьмой разряды вхапа кода команды процессора подключены к входамсоответственно с второго а четвертый тпетьегс ешифратара, ыходьпервого дешфратара саед.неы с вторыми входами элементе г И:1. первойгруппы, выходы котарьх соединены спервыми входами элементов И-НЕ второй группы, вторые входы и выходыкоторых саелпнены соответственно свыходами второго дешфратора и информационными вхо-ами узта двунаправленной передачи даьх, инфармациан,ыйвход-вьход которого подключен к информационному входу-выходу процессора, третий выход третьего дешпфратора соедиен с первыми входами четвертого элемента 1 ПИ и десятого элемента И, а также с прямым входам одиннадцатого элемента И, инверсный входкоторого саеднен с первыми входамис двенадцатага по четырнад"атый эле -ментов И, вторым входам десятога элемента И, выха ам второго триггера,инверсным входом пятнадцатого лемента И, прямой вход которого соединенс вторым входом двенадцатого элемента И, вторым входам четвертого элемента ИЛИ и четвертым выходом третьего дешифратора, пятый выход которогосоепинен с третьим входам четвертогоэлемента ИЛИ и вторым входом четырнадцатого элемента И, выход которогосоединен с первым входам пятого элемента ИЛИ, второй и третий входы ивыход которого соединены соответственно с выходами цесятога и пятнадцатого элементов И и стробируюшимвходом второго деш 1 ратора, шестойвыход третьего дешифратора соединенс четвертым вхацом четвертого элемента ИЛИ и вторым входом тринадцатогоэлемента И, выход которого соединенс первым входом шестога элемента ИЛИ,25 15 20 30 35 40 45 50 55 адкшса 1 а" у у в:яюнмувходу уз;а дунаправлепо ер ланиданных, первьм входам э:еетИ 1 Ивамаа элемь ;И тртьему халу первого элемата И квходу признака режи а аца процессора, вход прзака режьгывадапроцессора подключен к второму входуэлемента ИЛИ-НЕ и перым входал девятога и пятого элементов И, ввходэлемента И 1 ИЕ соединен с входамвторой и третий входы и выход которого соединены соответственна с выходами двенадцатого и одиннадцатого элементов 11 и стробирующим входом первого дешифратора, седьмой выход третьего дещифратора соединен с чет - вертым входом второго элемента И, выход которого соединен с т, одом первого одновибратара, вторыми входами восьмого и девятого элементов И и подключен к выходу признака обращения к каналам ввода-вывода процессора, выход первого элемента ИЛИ соединен с вторым входом седьмого элемента И и первым входом шестого элемента ИЛИ второй вход которого соединен с выходом четвертого элемента ИЛИ и вторым входом пятого элемента И, выход седьмого элемента ИЛИ подключен к выходу управления модификацией адреса процессора, первый синхровход и вход признака начала обработки процессора подключены соответственно к инверсному и прямому входам первого элемента И-НЕ, выход третьего элемента ИЛИ соединен с входом запуска формирователя импульсов и входом второго однавибратора, выход которого соединен с выходом признака окончания обработки инструкций процессора, выход первого элемента И соединен с первыми входами шестнадцатого и семнадцатого элементов И, второй синхровход процессора подключен к тактовому входу формирователя импульсов, первый выход которого соединен с вторым входом шестнадцатого элемента И и вторым входом шестого элемента И, выход которого соединен с первым входом восемнадцатого элемента И, второй вход и выход которого соединены соответственно с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и входом установки в "0" второго триггера, выход которого соединен с первым входом восьмого элемента ИЛИ и информационным входом третьего триггера, вход синхронизации которого соедийен с выходом девятнадцатого элемента И, первый вход которого соединен с выходом шестнадцатого элемента И и первыми входами двадцатого и двадцать первого элемен-. - тов И, выходы которых соединены соответственно с входом синхронизации четвертого триггера и первым входом установки в "1" второго триггера, второй вход установки в 1 которого11 1 соединен с выходом второго элемента 76464)11 ЛИ, входамп установки в 0 третьего и пятого триггеров и первым входам установки в 10 четвсртога триггера, выход которого соединен с вторыми входами восьмого элемента ИЛИи двадцать первого элемента И, выходвосьмого элемента ИЛ 11 соединен с информационныл 1 входом четвертого триггера, второй вход установки в 10"которого соединен с выходом двадцатьвторого элемента И, первый вход которого соединен с выходом семнадцатого элемента И и первыми входами 15 двадцать третьего элемента И и второго элемента И-НЕ, выходы которыхсоединены с входами синхронизациисоответственно второго и пятоготриггеров, второй вход семнадцатого 20 элемента И соединен с вторым выходомформирователя импульсов и вторымвходом четвертого элемента И, информационный вход и инверсный выходпятого триггера подключены к вторым 25 входам третьего и девятнадцатогоэлементов И, прямой выход пятоготриггера соединен с вторыми входамидвадцатого и двадцать третьего элементов И, выход третьего триггерасоединен с первым входом двадцатьчетвертого элемента И, выход которого соединен с информационным входомвторого триггера, выход первого одновибратора соединен с третьим входом девятого элемента И и входомтретьего одновибратора, выход которого соединен с четвертым входом девятого элемента И и подключен к выходу признака готовности процессора,выходы сопровождения вывода и сопровождения ввода процессора подключенык выходам соответственно девятого ивосьмого элементов И, о т л и ч аю щ и й с я тем, что, с целью повыщения быстродействия за счет реализации одновременной обработки различных типов инструкций, он содержитшифратор, с первого по восьмой входы которого объединены и подключены 50к информационному выходу узла двунаправленной передачи данных, девятыйвход и первый выход шифратора соединены соответственно с выходом первого элемента И третьим входом третьего элемента ИЛИ, четвертый вход которого соединен с вторыми входамивторого элемента И-НЕ и двадцатьчетвертого элемента И, третьими входами девятнадцатого, двадцатого из 47 б 464 двадцать первого элементов И и вто- третьего Рым выходом шифратора, третий выход двадцать которого соединен с пятым входом двадцать 4элемента ИЛИ, вторым входомвторого и третьим входомпервого элементов И. Таблица 1 Код в шине 70 Состояние выходов П 7 П 6 Р 5 Р 4 РЗ Р 2 1) ПО 1 11 111(линия) (НВТ) (КВТ) О О 1 О О 1 О 1 О ОО О О О 1 0 О О О 1 О О 1 О О 1. 1 О О О 1 О О 1 Х Х Х Х Х Х Х О 1 О Где ХХХ - любой код, кроме указанных выше. Таблица 2 Группа функция А 13 А 2 А 11 А 10 А 9 Д АВ А 7 Аб А 5 А 4 АЗ А 2 А АОО 7 О 6 Р 5 ОА ОЗ О 2 О ОО НнемоникаАдрес битав байте Адрес байта ОО О ВХОД Опрос состояния битв на включение ООО Опрос состояния бита на вк 7 точение Аарес байта О 1 О 1 1 Адрес битав байте ВЫХОД Устаиовка бита бев фиксации О. О 1 1 О О Очистка битв бев фиксации -Ф Адрес байта О 1 1 О 1 Адрес битав байте Установка бита с фиксацией 9" О 1 1 1 О.ФОчистка битас фиксацией 1 Лабой элемент кроме Я О 1 О О О О О 1 О . О О О ВЕТВЪ Начало ветви конец ветвейО О О О О О О О О О 1 О 1 О 1 О О О О О Линия (нетоперации) 40 Таблица 3 Состояйие триггеров восле обработки Шаг Элементыинструкции Ло гическийуровеньсигналаСОСТ Процесс обработки 1112 13 14 1 11- . Х 1 Формируются сигналы С 2, ТЗ и Т 41 Состояние триггера 11 не изменяется, так как элемент И 41 будет закрыт; О О О О 2 С (1- Х 2 Под действием сигналов С 1, Т 2 и ОНВТ информация с триггера 11перепишется в триггер 13. Поддействием сигналов С 1, Т 4 иНВТ триггер 12 установится всостояние "1" (откроется ветвь).Под действием сигналов С 2, ТЗ иСОСТ триггер 11 установится в состояние "О". 1 1 .О1476464 Ша г Элементыинструкции Состояние триггеров после обработки Процесс обработки ЛогическийуровеньсигналаСОСТ 12 13 1 114,О Э-И- ХЗ ОО 4 С -П" Х 45 С 1О О 1 О 1 1 1 О О 17 3 И Хб О 1. О 1 О 1 О См, шаг 1,О 9 -Ь. Х 7 10 Й 1. ХЬ 11 -О У 1 1 1 О 1 1 О 6 "1 Н- Х 5 О 16ПР 14 О ; ШО тЧОЛ 3 Под действием сигналов С 1, ТЭ и 1НВТ в триггер 14 запишется результат логического сложения по.ИЦИ с выходов триггеров 11 и 14,под действием сигналов С 1, Т 4 иНВТ информация с триггера 1 Э перепишется в триггер 11. По заднему фронту 12 установится в состояние "О" (закроется ветвь).Затем сформируются сигналы С 2,ТЗ, Т 4, которые не изменят состояния процессора. См. шаг 2 (откроется ветвь). О Под действием сигналов С 1ТЗ иНВТ в триггер 14 запишется результат логического сложенияпо ИЛИ с выходов триггеров 11 и14 под действием сигналов С 1,Т 4, НВТ информация с триггера 13перепишется в триггер 11, позаднему фронту совокупности.этих сигналов триггер 12 установится в состояние О (закроетсяветвь).Под действием сигналов С 1, ТЗ иНВТ информация с триггера 11 перепишется в триггер 13, Под действием сигналов С 1, Т 4 и НВТтриггер 12 установится в состояние "1" (откроется ветвь). Затемсформируются сигналы С 2, ТЗ и Т 4,которые не изменят состояние процессора. См. шаг 5 (закроется ветвь). Под О действием сигналов СЭ, Т 2 и СОСТ триггер 11 установится в состояние "О",Под действием сигналов С 1, ТЗ и 1КВТ в триггер 11 запишется результат логического сложения по ИЦИс выходов триггеров 11 и 14, поддействием сигналов С 1, Т 4 и КВТтриггер 14 установится в состояние "О. См. шаг 1 (откроется ветвь). О С триггера 11 выдается сигнал О РЕЗ ("О"), затем формируются сигналы С 4 и Т 4, которые не изменят состояние. процессора,1476464 1 1 Состояние триггеров после обработки Наг Элементыинструкции ЛогическийуровеньсигналаСОСТ Процесс обработки 12 й. -И- Х 9 13 : О- У 2 О 1 О 1 1 О О 1 1 О О О Юллллпл. 7 Р РО-Р 7 14 С -П- Х 10 115 -О- У 3 18Прод и-"сппе табл,3 11 123 14 т См. шаг 3 (закроется ветвь). 1 Под действием сигналов С 1, ТЗ и 1НВТ информация с триггера 11 йерепишется в триггер 13. Под дей"ствием сигналов С 1, Т 4 и НВТтриггер 12 установится в состояние "1" (откроется ветвь). Хтриггера 11 выдается сигнал РЕЗ("1"). Затем сформируются сигналыС 4 и Т 4, которые не изменят состояние процессора,См. шаг 2 (закроется ветвь). ОС триггера 11 выдается результат 1(сигнал РЕЗ) уровнем "О". Затемпод действием сигналов С 4 и Т 4триггеры 13 и 4 установятся всостояние "О", триггер 11 - всостояние "1", триггер 12 останется в состояние О", Процессор установится в исходное состояние,

СмотретьЗаявка

4103860, 04.08.1986

ПРЕДПРИЯТИЕ ПЯ А-7070

СКЛЕМА МИХАИЛ ВАСИЛЬЕВИЧ, ВИТКОВСКИЙ ИГОРЬ АЛЕКСАНДРОВИЧ

МПК / Метки

МПК: G05B 19/18, G06F 9/00

Метки: контроллера, однобитовый, программируемого, процессор

Опубликовано: 30.04.1989

Код ссылки

<a href="https://patents.su/10-1476464-odnobitovyjj-processor-programmiruemogo-kontrollera.html" target="_blank" rel="follow" title="База патентов СССР">Однобитовый процессор программируемого контроллера</a>

Предыдущий патент: Оптический модуль для сложения и вычитания в системе остаточных классов

Следующий патент: Микропрограммное устройство управления

Случайный патент: Способ возведения бетонной плотины