Декодер палсекам (его варианты)

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1109958

Автор: Хохлов

Текст

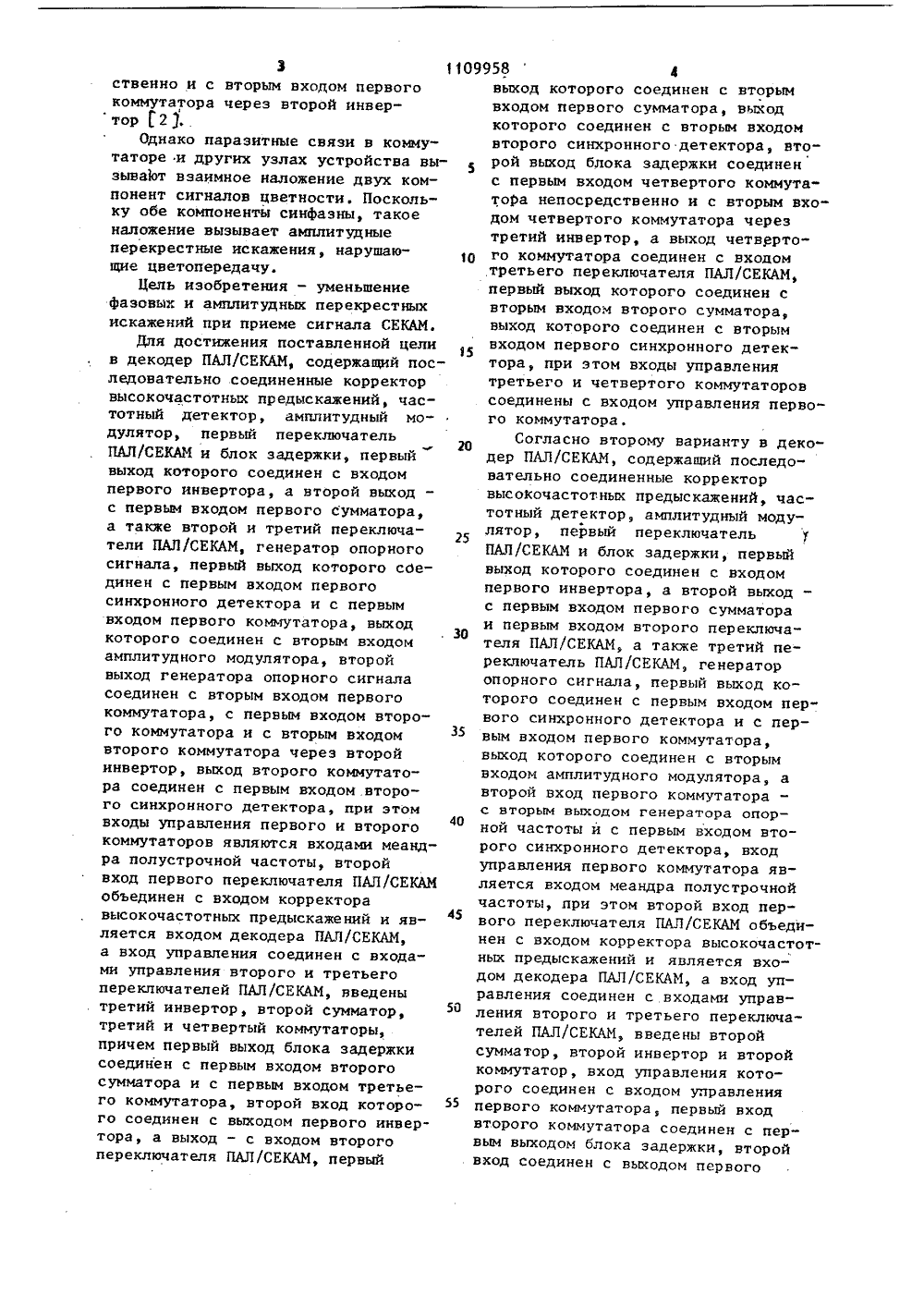

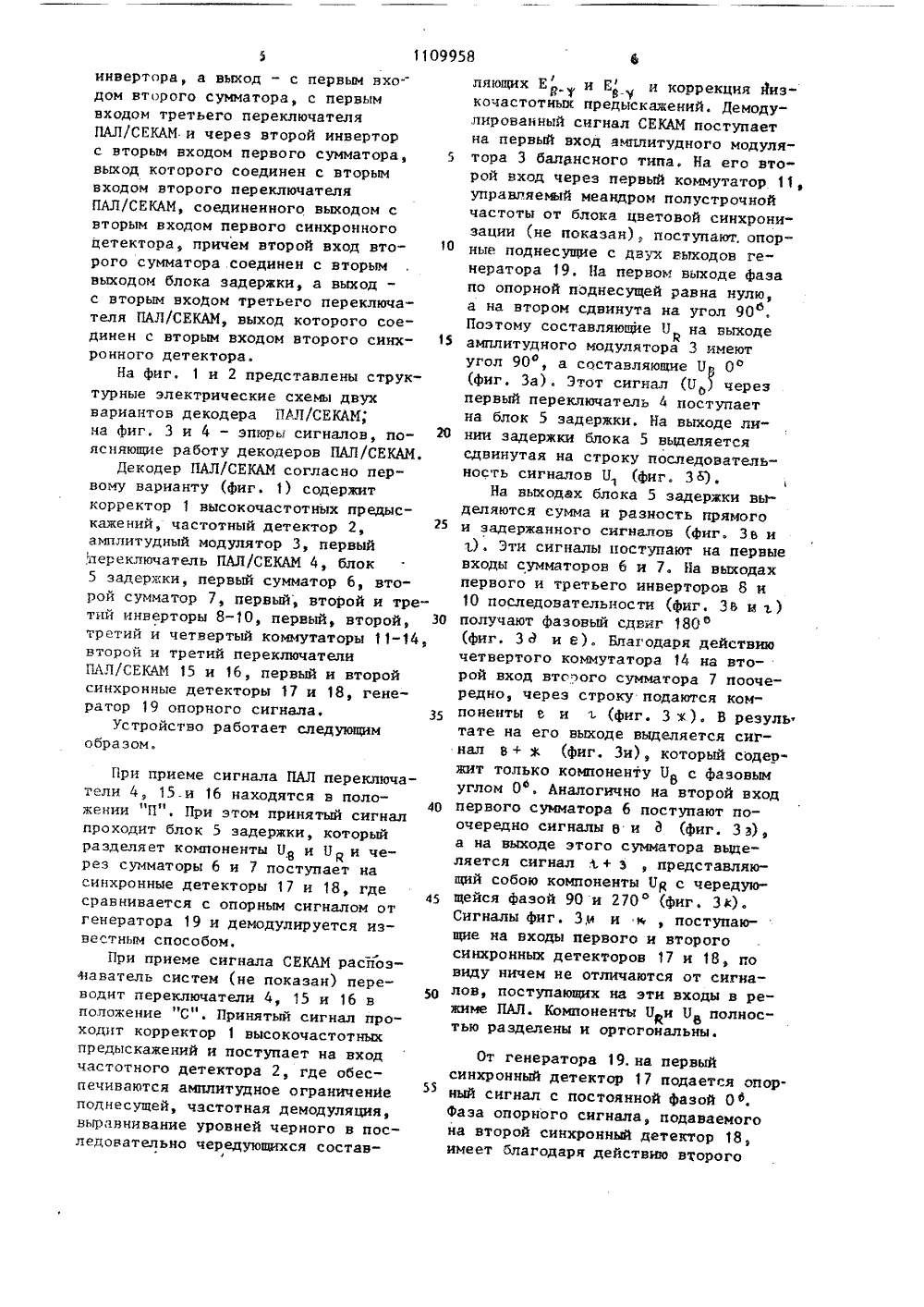

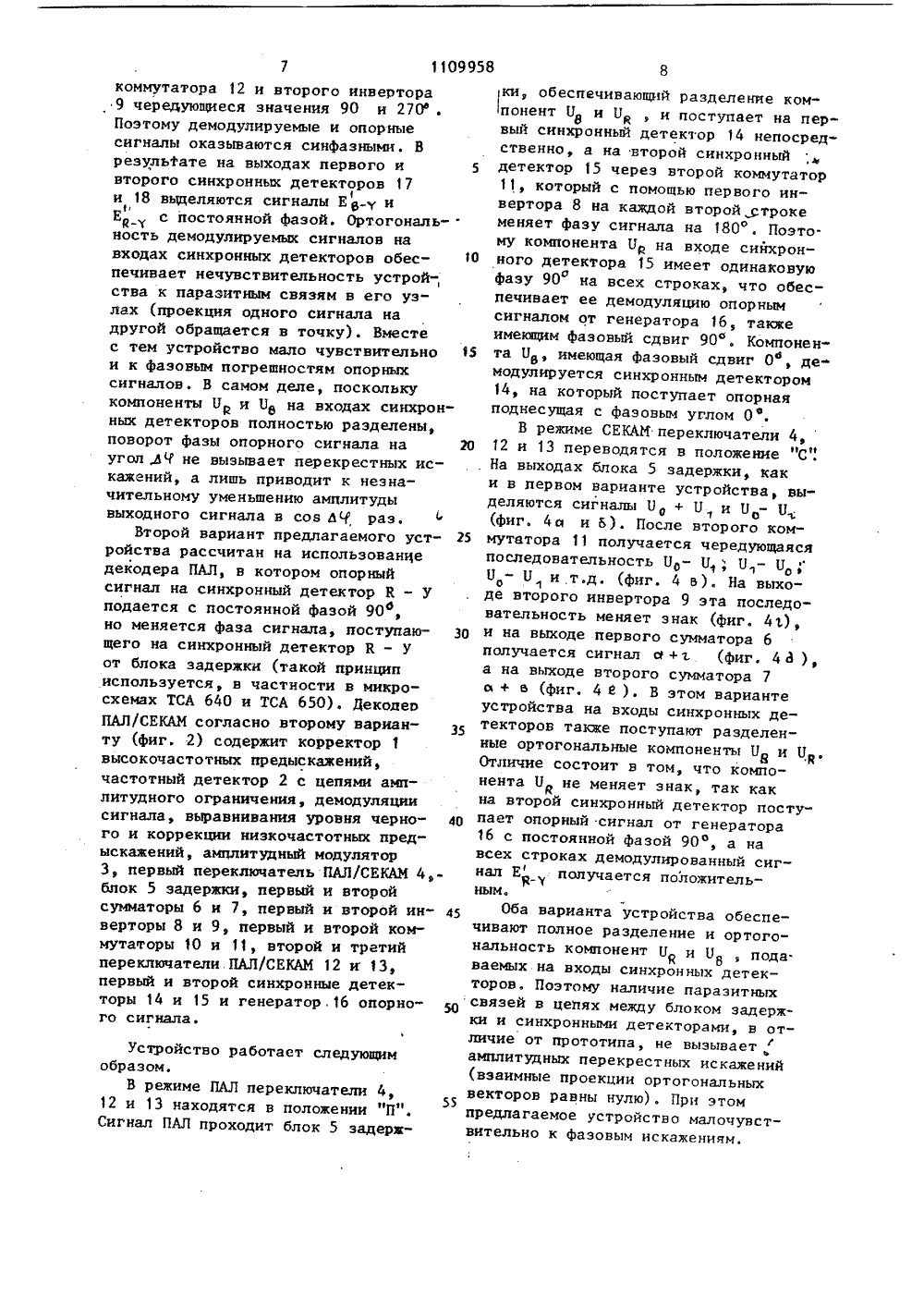

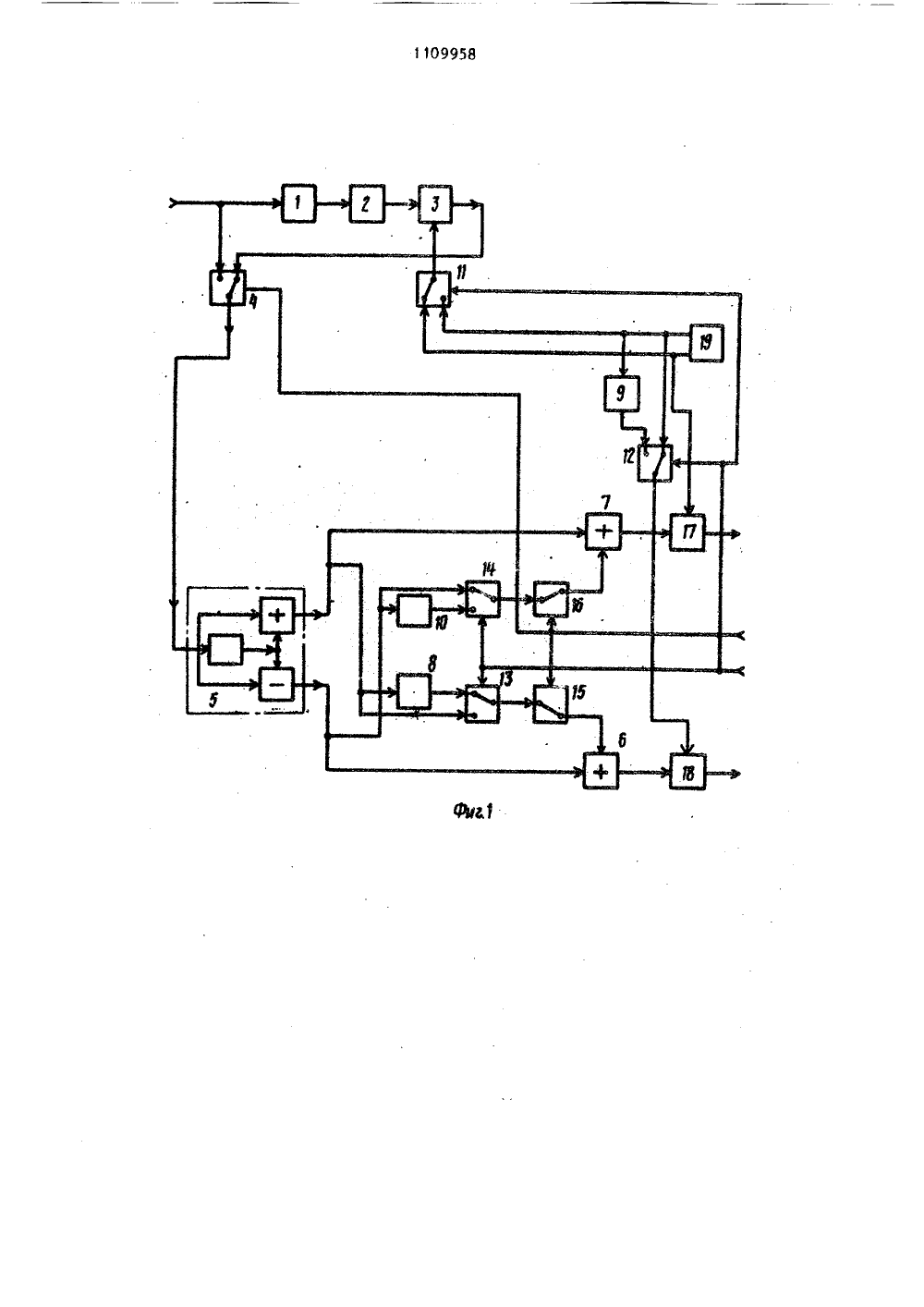

СОЮЗ СОВЕТСНИХцццлццццццррРЕСПУ БЛИН 15 й Н 0 ПИОАНИЕ ИЗОБРЕТЕНИЯ.8)еликобританииН 04 М 9/42, 1972.1981, Р 16,ип). ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРИТИЙ ЕКОДЕР ПАЛ/СЕКАИ (ЕГО ВАРИАНТЫ) .(57) 1. Декодер ПАЛ/СЕКАИ, содержащий последовательно соединенныйкорректор высокочастотных предыскажений, частотный детектор, амплитудный модулятор, первый переключатель ПАЛ/СЕКАИ и блок задержки,первый выход которого соединен свходом первого инвертора, а второйвыход - с первым входом первого сумматора, а также второй и третийпереключатели ПАЛ/СЕКАИ, генератор опорного сигнала, первый выходкоторого соединен с первым входомпервого синхронного детектора и спервым входом первого коммутатора,выход которого соединен с вторымвходом амплитудного модулятора, второй выход генератора опорного сигнала соединен с вторым входом первого коммутатора, с первым входомвторого коммутатора и с вторым входом второго коммутатора через второй инвертор, выход второго коммутатора соединен с первым входом второго синхронного детектора, приэтом входы управления первого и второго коммутаторов являются входами меандра полустрочной частоты,второй вход первого переключателя ПАЛ/СЕКАИ объединен, с входом корректора высокочастотных предыскаженийи является входом декодера ПАЛ/СЕКАИ,а вход управления соединен с входами управления второго и третьегопереключателей ПАЛ/СЕКАИ, о т л ич а ю щ и й с я тем, что, с цельюуменьшения перекрестных искаженийпри приеме сигнала СЕКАИ, в неговведены третий инвертор, второй сумматор, третий и четвертый коммутаторы, причем первый выход блока задержки соединен с первым входом второго сумматора и с первым входомтретьего коммутатора, второй входкоторого соединен с выходом первогоинвертора, а выход - с входом второго переключателя ПАЛ/СЕКАИ, первыйвыход которого соединен с вторымвходом первого сумматора, выход которого соединен с вторым входом второго синхронного детектора, второй выход блока задержки соединенс первым входом четвертого коммутатора непосредственно и с вторым входом четвертого коммутатора черезтретий инвертор, а выход четвертого коьаутатора соединен с входомтретьего переключателя ПАЛ/СЕКАИ,первый выход которого соединен свторым входом второго сумматора,выход которого соединен с вторымвходом первого синхронного детектора, при этом входы управлениятретьего и четвертого коммутаторовсоединены с входом управления первого коммутатора,2. Декодер ПАЛ/СЕКАИ, содержащий последовательно соединенные корректор высокочастотных предыскажений, частотный детектор, амплитуд 11 нцй модулятор, первый переключатель ПАЛ/СЕКАИ и блок задержки, первый выход которого соединен с входом первого инвертора, а второй выходс первым входом первого сумматора и первым входом второго переключателя ПАЛ/СЕКАИ, а также третий переключатель ПАЛ/СЕКАИ, генератор опорного сигнала, первый выход которого соединен с первым входом первого синхронного детектора и с первым входом первого коммутатора, выход которого соединен с вторым входом амплитудного модулятора, а второй вход первого коммутаторас вторым выходом генератора опорного сигнала и с первым входом второго синхронного детектора, вход управления первого коммутатора является входом меандра полустрочной частоты, при этом второй вход первого переключателя ПАЛ/СЕКАИ объединен с входом корректора высокочастотных предыскажений и является входом декодера ПАЛ/СЕКАИ, а вход управления соединен с входами управления второго и третьего переключателей ПАЛ/СЕКАИ, о т л и ч а ю щ и й с ятем, что, с целью уменьшения перекрестных искажений при приеме сигнала СЕКАИ, в него введенц второйсумматор, второй инвертор и второйкоммутатор, вход управления которого соединен с входом управления первого коммутатора, первый вход второго коммутатора соединен с первымвыходом блока задержки второй входсоединен с выходом первого инвертора, а выход - с первым входом второго сумматора, с первым входом третьего переключателя ПАЛ/СЕКАИ и через второй ннвертор с вторым входом первого сумматора, выход которого соединен с вторым входом второго переключателя ПАЛ/СЕКАИ, соединенного выходом с вторым входомпервого синхронного детектора, причем второй вход второго сумматорасоединен с вторым выходом блоказадержки, а выход " с вторым входом третьего переключателя ПАЛ/СЕКАИ,выход которого соединен с вторымвходом второго синхронного детектора.0 Изобретение относится к техникецветного телевидения, в частностик двухстандартным цветным телевизорам и видеоконтрольным устройствам,Известен декодер ПАЛ/СЕКАИ, который содержит последовательно соединенные корректор высокочастотныхпредыскажений, частотный детектор,балансный амплитудный модулятор,блок задержки, генератор опорногосигнала и два синхронных детектора 1,В данном декодере велики фазовые.перекрестные искажения в режиме СЕКАИ, которые обусловлены наличием на вхопах синхронных детекторов двух неразделенных компонентсигнала цветности.Наиболее близким по техническойсущности к предлагаемому являетсядекодер ПАЛ/СЕКАИ, содержащий последовательно соединенные корректорвысокочастотных предцскажений, час Втотный детектор, амплитудный детектор, первый переключатель ПАЛ/СЕКАИ, блок задержки, два выхода которого соединены через второй и третий переключатель ПАЛ/СЕКАИ соответственно с первыми входами первого и, второго синхронных детекторов, вторые входы которых через первый и второй коммутаторы соединены с выюдами генератора опорного сигнала, дричем первый выход блока задержки соединен с первым входом первого сумматора, а второй выход соединен с вторым входом первого сумматора через инвертор, при этом, выход первого сумматора соединен через третий коммутатор с вторыми входами второго и третьего переключателей ПАЛ/СЕКАИ, входы управления которых соединены с входами управления первого переключателя ПАЛ/СЕКАИ, кроме того, первый вцход генератора опорного сигнала соединен с вторым входом амплитудного модулятора непосредвыход которого соединен с вторымвходом первого сумматора, вьжодкоторого соединен с вторым входомвторого синхронного детектора, второй выход блока задержки соединенс первым входом четвертого коммутатора непосредственно и с вторым входом четвертого коммутатора черезтретий инвертор, а выход четвертого коммутатора соединен с входом третьего переключателя ПАЛ/СЕКАМ,первый выход которого соединен свторым входом второго сумматора,выход которого соединен с вторымвходом первого синхронного детектора, при этом входы управлениятретьего и четвертого коммутаторовсоединены с входом управления первого коммутатора,Согласно второму варианту в декодер ПАЛ/СЕКАМ, содержащий последовательно соединенные корректорвысокочастотных предыскажений, частотный детектор, амплитудный модулятор, первый переключатель уПАЛ/СЕКАМ и блок задержки, первыйвыход которого соединен с входомпервого инвертора, а второй выход -с первым входом первого сумматораи первым входом второго переключателя ПАЛ/СЕКАМ, а также третий переключатель ПАЛ/СЕКАМ, генераторопорного сигнала, первый выход которого соединен с первым входом первого синхронного детектора и с пер 35вым входом первого коммутатора,выход которого соединен с вторымвходом амплитудного модулятора, авторой вход первого коммутатора -с вторым выходом генератора опор 40ной частоты и с первым входом второго синхронного детектора, входуправления первого коммутатора является входом меандра полустрочной45частоты, при этом второй вход первого переключателя ПАЛ/СЕКАМ объединен с входом корректора высокочастотных предыскажений и является входом декодера ПАЛ/СЕКАМ, а вход управления соединен с входами управ 50ления второго и третьего переключателей ПАЛ/СЕКАМ, введены второйсумматор, второй инвертор и второйкоммутатор, вход управления которого соединен с входом управления первого коммутатора, первый вход второго коммутатора соединен с первым выходом блока задержки, второй вход соединен с выходом первого3 109958 4ственно и с вторым входом первогокоммутатора через второй инвертор 2Однако паразитные связи в коммутаторе и других узлах устройства вы 5зываЬт взаимное наложение двух компонент сигналов цветности. Поскольку обе компоненты синфазны, такоеналожение вызывает амплитудныеперекрестные искажения, нарушающие цветопередачу.Цель изобретения - уменьшениефазовых и амплитудных перекрестныхискажений при приеме сигнала СЕКАМ.Для достижения поставленной целив декодер ПАЛ/СЕКАМ, содержащий последовательно соединенные корректорвысокочастотных предыскажений, частотный детектор, амплитудный модулятор, первый переключательПАЛ/СЕКАМ и блок задержки, первыйвыход которого соединен с входомпервого инвертора, а второй выход -с первым входом первого сумматора,а также второй и третий переключатели ПАЛ/СЕКАМ, генератор опорногосигнала, первый выход которого соединен с первым входом первогосинхронного детектора и с первымвходом первого коммутатора, выходкоторого соединен с вторым входомамплитудного модулятора, второйвыход генератора опорного сигналасоединен с вторым входом первогокоммутатора, с первым входом второго коммутатора и с вторым входомвторого коммутатора через второйинвертор, выход второго коммутатора соединен с первым входом второго синхронного детектора, при этомвходы управления первого и второгокоммутаторов являются входами меандра полустрочной частоты, второйвход первого переключателя ПАЛ/СЕКАМобъединен с входом корректоравысокочастотных предыскажений и является входом декодера ПАЛ/СЕКАМ,а вход управления соединен с входами управления второго и третьегопереключателей ПАЛ/СЕКАМ, введенытретий инвертор, второй сумматор,третин и четвертый коммутаторы,причем первый выход блока задержкисоединен с первым входом второгосумматора и с первым входом третьего коммутатора, второй вход которого соединен с выходом первого инвертора, а выход - с входом второгопереключателя ПАЛ/СЕКАМ, первыйинвертора, а выход - с первым входом второго сумматора, с первым входом третьего переключателя ПАЛ/СЕКАМ и через второй инвертор с вторым входом первого сумматора, выход которого соединен с вторым входом второго переключателя ПАЛ/СЕКАИ, соединенного выходом с вторым входом первого синхронного детектора, причем второй вход второго сумматора соединен с вторым выходом блока задержки, а выход - с вторым входом третьего переключателя ПАЛ/СЕКАИ, выход которого соединен с вторым входом второго синхронного детектора.На фиг. 1 и 2 представлены структурные электрические схемы двух вариантов декодера ПАЛ/СЕКАМ; на фиг. 3 и 4 - эпюры сигналов, поясняющие работу декодеров ПАЛ/СЕКАМ.Декодер ПАЛ/СЕКАМ согласно первому варианту (фиг. 1) содержит корректор 1 высокочастотных предыскажений, частотный детектор 2, амплитудный модулятор 3, первый ,"переключатель ПАЛ/СЕКАИ 4, блок 5 задержки, первый сумматор 6, второй сумматор 7, первый, втоРой и тре тий инверторы 8-10, первый, второй, третий и четвертый коммутаторы 11-14 второй и третий переключатели ПАЛ/СЕКАИ 15 и 1 б, первый и второй синхронные детекторы 17 и 18, генератор 19 опорного сигнала.Устройство работает следующим образом.11 ри приеме сигнала ПАЛ переключатели 4, 15.и 16 находятся в положении "П", Прн этом принятый сигналпроходит блок 5 задержки, которыйразделяет компоненты Пв и П и чеЯрез сумматоры б и 7 поступает насинхронные детекторы 17 и 18, гдесравнивается с опорным сигналом отгенератора 19 и демодулируется известным способом,При приеме сигнала СЕКАМ распознаватель систем (не показан) переводит переключатели 4, 15 и 16 вположение "С". Принятый сигнал проходит корректор 1 высокочастотныхпредыскажений и поступает на входчастотного детектора 2, где обеспечиваются амплитудное ограничениеподнесущей, частотная демодуляция,выравнивание уровней черного в последовательно чередующихся составляющих Е 1, и Е и коррекция йизф укочастотных предыскажений. Демодулированный сигнал СЕКАМ поступаетна первый вход амплитудного модуля тора 3 балансного типа, На его второй вход через первый коммутатор 11управляемый меандром полустрочнойчастоты от блока цветовой синхронизации (не показан) поступают, опорные поднесущие с двух выходов генератора 19, На первом выходе фазапо опорной поднесущей равна нулю,а на втором сдвинута на угол 90Поэтому составляющие П на выходеР 15 амплитудного модулятора 3 имеютугол 90 , а составляющие П 0(фиг. Зе). Этот сигиее (р 1 черезпервый переключатель 4 поступаетна блок 5 задержки. На выходе ли нии задержки блока 5 выделяетсясдвинутая на строку последовательность сигналов П 1 (фиг. 3 Й .На выходах блока 5 задержки выделяются сумма и разность прямого й 5 и задержанного сигналов (фиг. Зв и1), Эти сигналы поступают на первыевходы сумматоров 6 и 7. На выходахпервого и третьего инверторов 8 и10 последовательности (фиг, Зь ц ъ) ЗО получают фазовый сдвиг 1806(фиг. 3 д и е). Благодаря действиючетвертого коммутатора 14 на второй вход второго сумматора 7 поочередно, через строку подаются компоненты е и ъ (фиг. 3 х ). В результате на его выходе выделяется сигнал 8 + м (фиг, Зи), который содержит только компоненту П 8 с фазовымуглом 0 . Аналогично на второй вход440 первого сумматора 6 поступают поочередно сигналы в и д (фиг. Зз),а на выходе этого сумматора вьщеляется сигнал 1 + з , представляющий собою компоненты П с чередующейся фазой 90 и 270 (фиг. Зк),Сигналы фиг. З,и и н , поступающие на входы первого и второгосинхронных детекторов 17 и 18, повиду ничем не отличаются от сигналов, поступающих на эти входы в режиме ПАЛ. Компоненты 0 и П полнос 6тью разделены и ортогойальны.От генератора 19. на первыйсинхронный детектор 17 подается опорный сигнал с постоянной фазой 0 ф.фаза опорного сигнала, подаваемого на второй синхронный детектор 18, имеет благодаря действию вТорого7 1109958 8коммутатора 12 и второго инвертора ки 9 обеспечивающий разделение ком 9 чередующиеся значения 90 и 2706 . понент П и ППоэтому демодулируемые и опорныесигналы оказываются синфазными. В ственно а на втор й9второ синхронныйрезульФате на выходах первого и детектор 15 черезз второи коммутаторвторого синхронных детекторов 17 11 который с помо. 9 помощью первого ини 18 вьщеляются сигналы Ее у ивертора 8 на каждо" йаждои второ строкеЕс постоянной фазой. Ортогональ- меняет фазу сигнала на 180. Поэтоность демодулируемых сигналов на му компонента П я на входе сийхронвходах синхронных детекторов обес О ного детектора 15 имеет одинаковуюпечивает нечувствительность устрой- фазу 90 на всеха всех строках, что обесства к паразитным связям в его уз- печивает ее демодуодуляцию опорнымлах (проекция одного сигнала на сигналом от генератора 16, такжедругой обращается в точку). Вместе имеющим фазовый с 90 ф Ксдвиг . Компоненс тем устройство мало чувствительно 15 та П имеющая фа8 9 азовыи сдвиг О, дефи к фазовым погрешностям опорных модулнруется синхроннымхронным детекторомсигналов, В самом деле поскольку914 на которь й9 ры поступает опорнаякомпоненты П и 06 на входах синхрон- поднесущая с фазовым углом Оф,ных детекторов полностью разделены9В режиме СЕКАИе . переключатели 4,поворот фазы опорного сигнала на 20 12 и 13 переводяреводятся в положение "С".угол,лМ не вызывает перекрестных ис- На выходах блока 5 задержки, каккажений, а лишь приводит к незна- и в первом вариварианте устройства, вычительному уменьшению амплитуды деляются сигн Пигналы р + П 1 и По Цвыходного сигнала в сов д 9 раз. " (фиг. 4 а и Ь) После второго комполучается чередующаясяВторой вариант предлагаемого уст мутатора 11 получройства рассчитан на использованцедекодера ПАЛ, в котором опорныйсигнал на синхронный детектор К - У , де второго и 9о инвертора 9 эта последоподается с постоянной фазой 909вательность меняетменяет знак (фиг. 4 ъ) 9но меняется фаза сигнала поступаю- ЗО и на выходе9оде первого сумматора 6щего на синхронный детектор К - У получается сигнал ю+ъ (фиг. 4 о ),от блока задержки (такой принцип а на выходе второго сумматора 7используется, в частности в микро- о + ь (фиг 4 Е) Вэтом вариантесхемах ТСА 640 и ТСА 650). Декодео устройства на входы синхронных деПАЛ/СЕКАМ согласно второму вариан- З 5 текторов также поступают разделенту (фиг. 2) содержит корректор 1высокочастотных предыскажений, Отличие состоит в том чтоненты итом 9 что компочастотный детектор 2 с цепями амп- нента П не меняет знак так к китудного ограничения, демодуляции на втоРой синхронный детектор постусигнала, выравнивания уровня черно пает опорный сигнал от генераторанизкочастотных пред 16 с постояннои фазой 90ыскажений, амплитудный модулятор всех строках демодулированный сиг 3, первый переключатель ПАЛ/СЕКАИ 4,- нал Еполучается положительблок 5 задержки, первый и второй нымсумматоры 6 и 7, первый и второй ин Оба варианта устройства обеспеверторы 8 и 9, первый и второй ком- чивают полное разделение и ортогомутаторы 10 и 11, второй и третийнальность компонент П и Упереключатели. ПАЛ/СЕКАМ 12 и 13, ваемых на входы синхронных детекпервый и второй синхронные детек- торов. Поэтому наличие паразитныхторы 14 и 15 и генератор,16 опорно- о вязей в цепях между блоком задержго сигнала. ки и синхронными детекторами в от 9личие от прототипа, не вызывает,устройство работает следующим амплитудных пе ек есобразом.итудных перекрестных искажений(взаимные проекции ортогональных12 и 13 нахВ режиме ПАЛ переключатели 4,5векторов Равн ы нулю . Ри этом). Пи находятся в положении "П". предлагаемое устроиство малочувстСигнал ПАЛ проходит блок 5 задерж- вительно к фазовым искажениям.1109958 Составитель Г. РосаткевичТехред Л.Коцюбняк Корректор О. Билак Петра едак аэ 6107/45 Тираж ВНИИПИ Государственног по делам изобретени 113035, Москва, Ж, Рауш

СмотретьЗаявка

3455303, 21.06.1982

ПРЕДПРИЯТИЕ ПЯ М-5876

ХОХЛОВ БОРИС НИКОЛАЕВИЧ

МПК / Метки

МПК: H04N 9/42

Метки: варианты, декодер, его, палсекам

Опубликовано: 23.08.1984

Код ссылки

<a href="https://patents.su/9-1109958-dekoder-palsekam-ego-varianty.html" target="_blank" rel="follow" title="База патентов СССР">Декодер палсекам (его варианты)</a>

Предыдущий патент: Устройство формирования цветоразностных сигналов в системе секам

Следующий патент: Устройство конвергенции оптических лучей стереотелевизионной камеры с одной передающей трубкой

Случайный патент: Индуктор электрической машины