Цифровой приемник дельта-модулированных сигналов многочастотных кодов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1683181

Автор: Охлобыстин

Текст

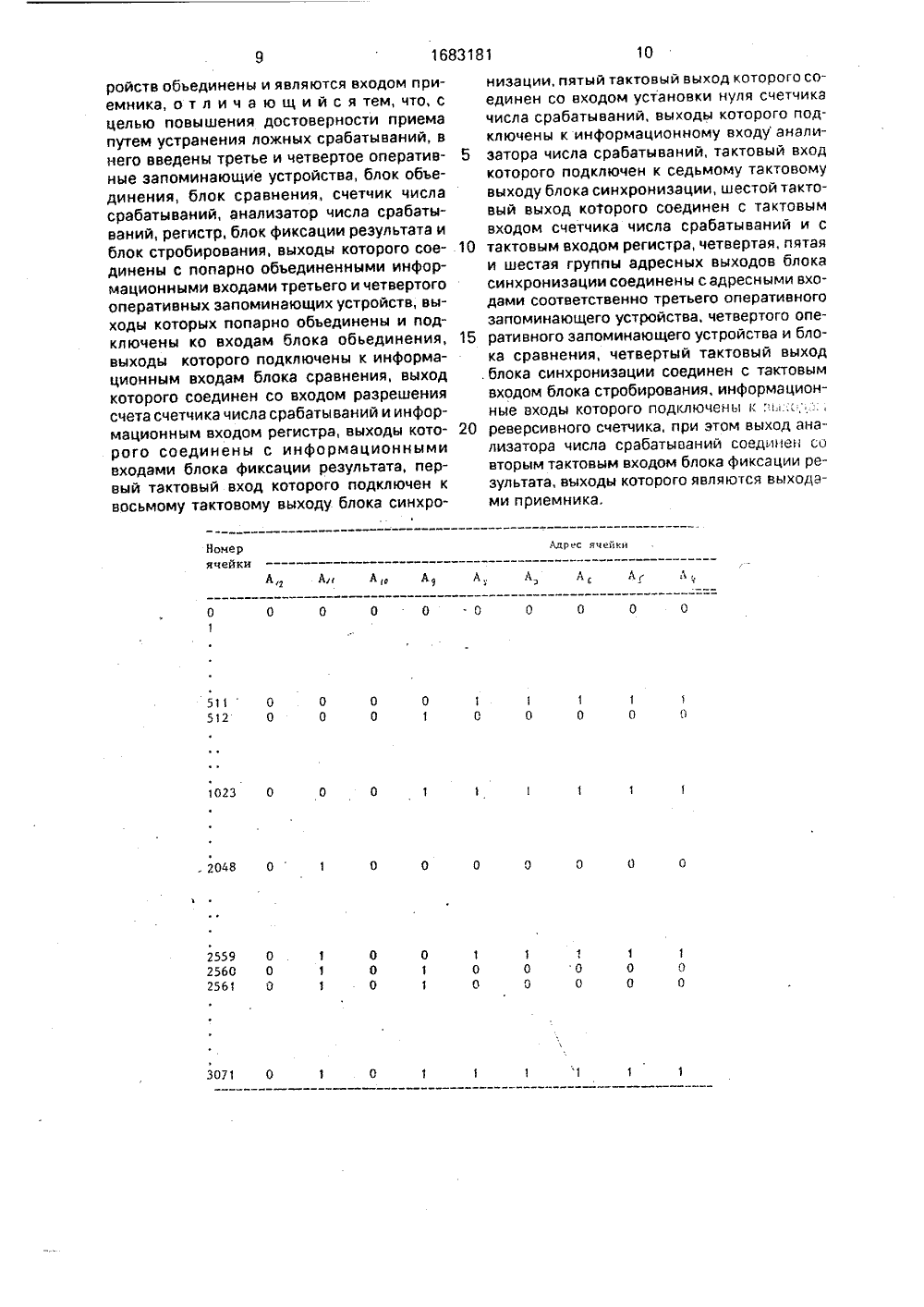

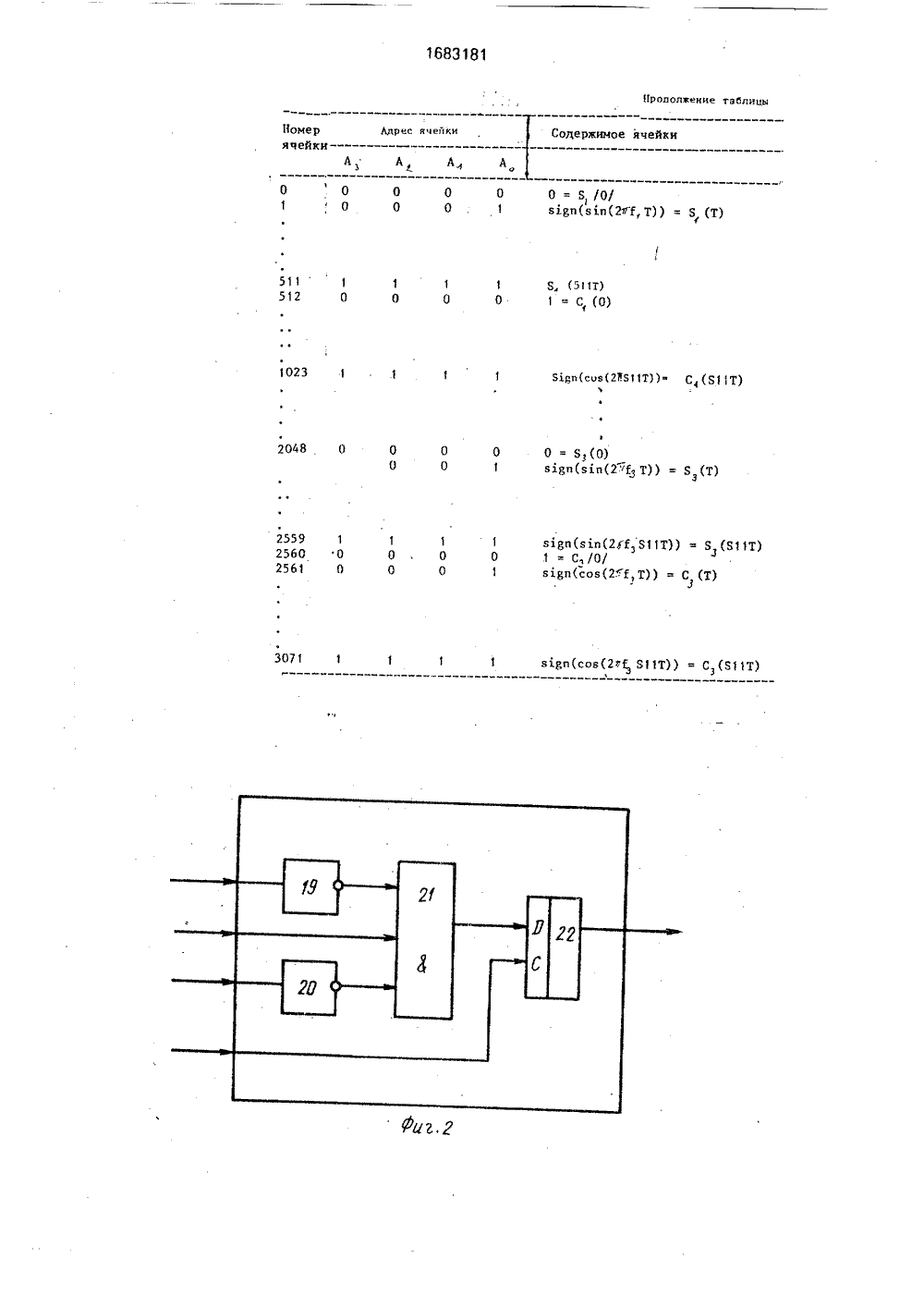

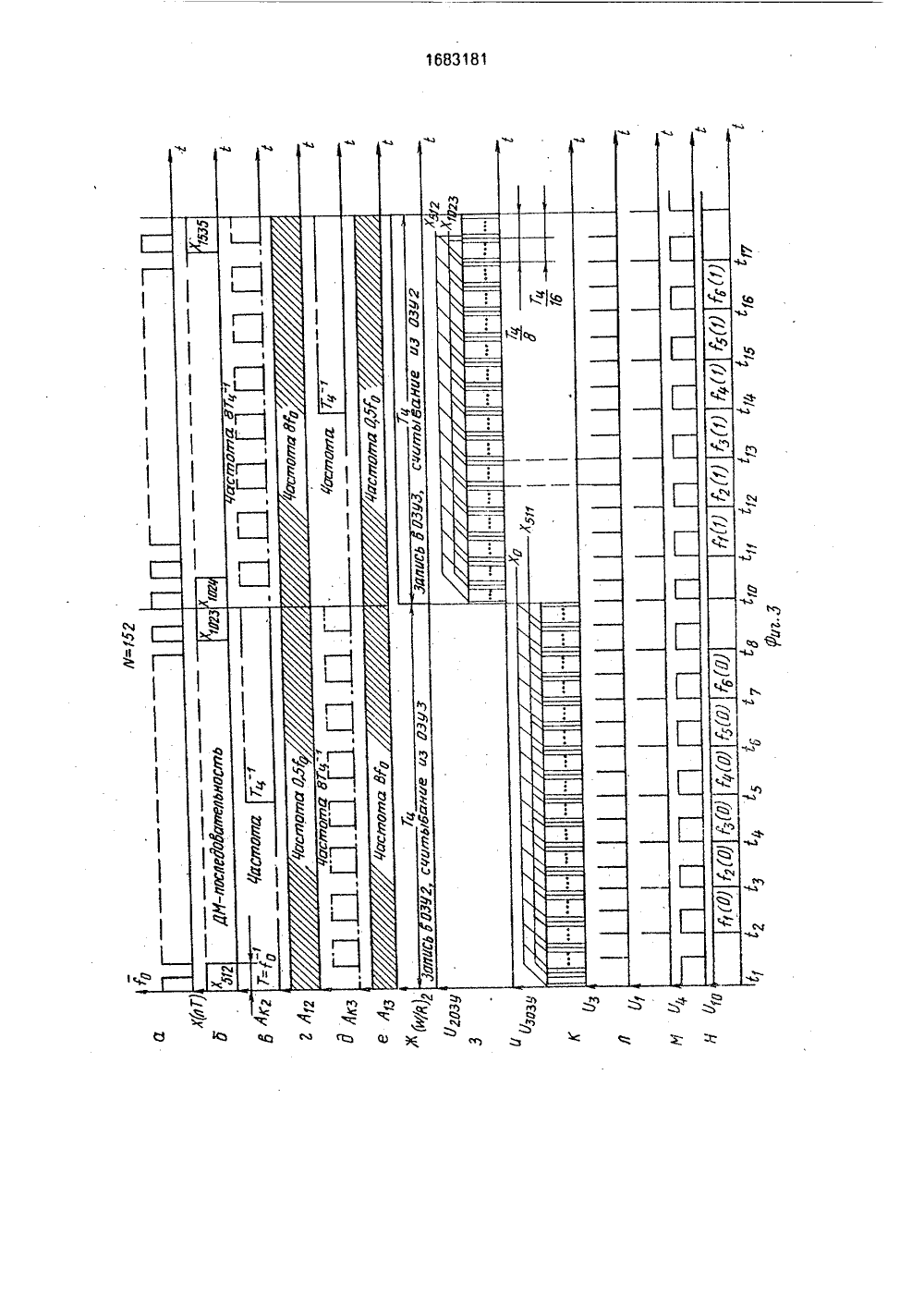

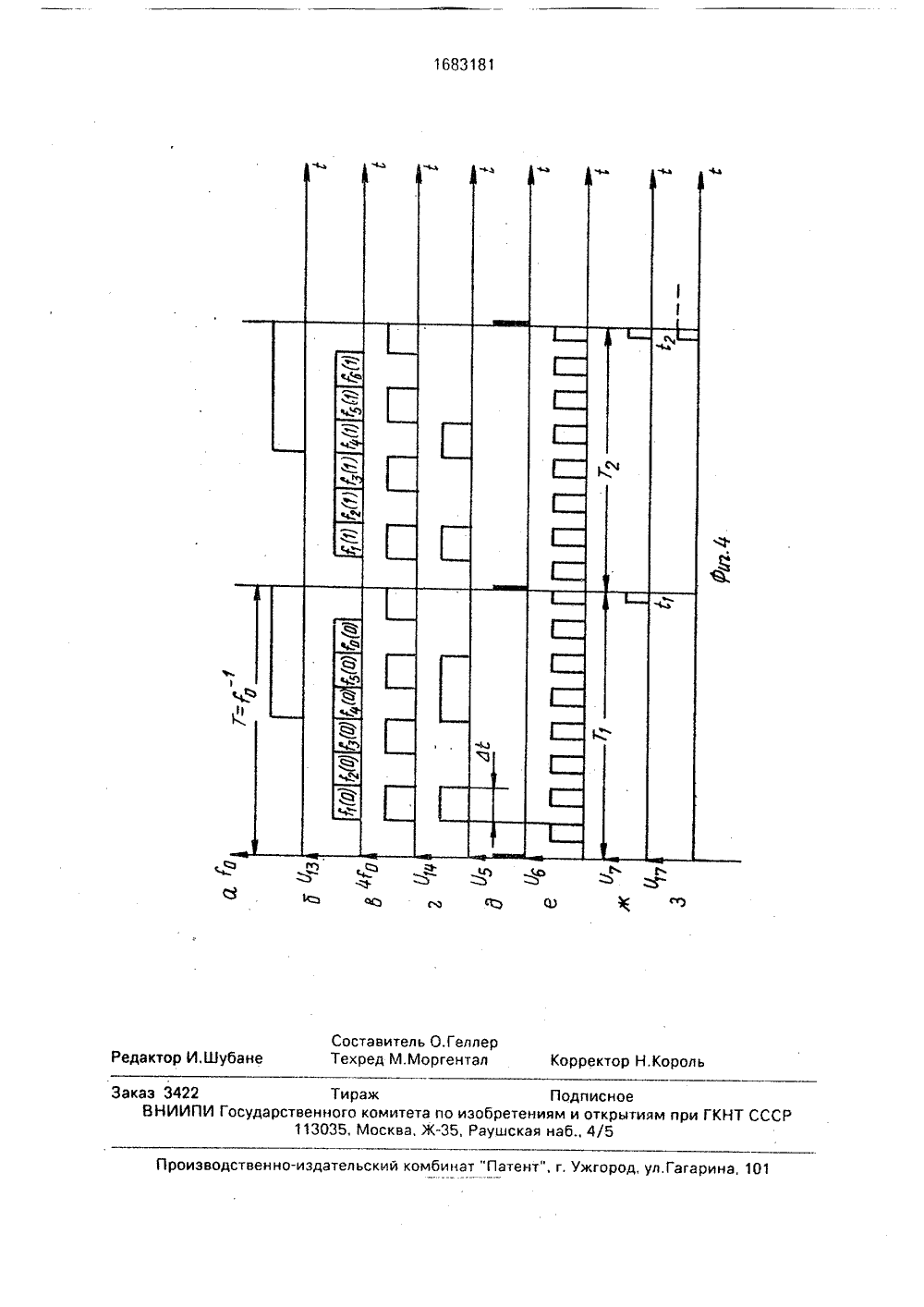

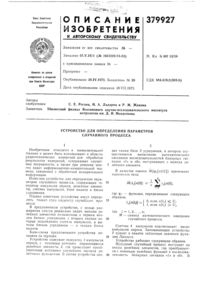

СОЮЗ СОВЕТСКИХ СОЦИАЛИСТИЧЕСКИ 683 А 1 ЕСПУБЛИК п 9)(5) 5 Н 04 1 27/ агарфайфа,., ИБЛ ДСТ. ИЗОБ ИДЕТЕЛ ЬСТ ОРСКОМУ К дова 8.ЛЬТА- МО- МНОГОЧАектросвязи. е достоверия ложных ник дельтаочастотных изации, чеГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР(56) Авторское свидетельство СС(54) ЦИФРОВОЙ ПРИЕМНИК ДДУЛИРОВАННЫХ СИГНАЛОВСТОТНЫХ КОДОВ(57) Изобретение относится к элЦель изобретения - повышениности приема путем устраненсрабатываний, Цифровой приеммодулированных сигналов мнокодов содержит блок 1 синхрон тыре оперативных запоминающих устроиства 2,3,4 и 5, постоянное запоминающее устройство 6, реверсивный и двоичный счетчики 7 и 8, дешифратор 9, блок 10 стробирования, элемент ИЛИ 11, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 12, блок 13 обьединения, блок 14 сравнения, счетчик 15 числа срабатывания, регистр 16, анализатор 17 числа срабатываний и блок 18 фиксации результата. Цель достигается последовательным перебором пороговых значений, начиная от минимального, соответствующего нижней границе рабочего диапазона уровней, с последующим сравнением пороговых значений с предварительно запомненными результатами согласованной фильтрации в каждом частотном канале в предыдущем цикле обработки, 4 ил,Изобретение. относится к электросвязи и может быть использовано в системах передачи слгналов многочастотными кодами 2 иэ 6 (2 из 8),Цель изобретения - повышение достоверности приема путем устранения ложных срабатываний,На фиг.1 прцведена структурная электрическая схема предложенного приемника; на фиг,2 - структурная электрическая схема анализатора числа срабатываний; на фиг.З и 4 - представлены диаГраммы Оаботы приемника.Цифоовой приемник дельта-модулироВанных сигналов мноГОчастотных кОдОВ содержит блок 1 синхронизации, первые, второе, третье и четвертое оперативные запоминаюцие устролитва ОЗУ 2,3,4 и 5, постоянное запомина)ощее устройство ПЗУ 6, Вверсивныл счетчик 7, Двоичный счетчик 8, дешифратор 9, блок 10 стробирования, элемент ИЛИ 11, элемент ИСКЛОЧАЮЩЕЕ ИЛИ 12, блок 13 объединения, блок 14 сравнения, счетчик 15 числа срабатываний, регистр 16, анализатор 17 числа срабатываний и блОк 18 фиксации результата.Анализатор числа срабатываний содержит первый и второй инверторы 19 и 20, элемент И 21 и Д-триггер 22,Приемник работает следующим образом.Сигналы многочастотного кода 2 из 6 (2 из 8), преобразованные В цифровую форму на базе дельта-модуляции с инерционным компанираванием (адаптлвной дельта-модуляции АДУ) поступа)от параллельно,на информационные входы пеовОГО и ВтороГО ОЗУ 2 и 3. Длительность одного символа х(пТ) АДУ - сигнала (фиг.36) равна периоду Т=1 1 О соответствующей тактовой частоты то (Ь показана на фиг,3 а), Сигналы х(гТ), 10 (фиг,3 а,б) показаны в увеличенном масштабе.Обработка последовательности х(пт) Ведется циклами, по К символов в каждом цикле(например, можно принять Й, что при 1 о=32 КГц соответствует длительности Тц одного цикла обработки 16 мс), Для обес" печения работы в реальном масштабе времени ОЗУ 2 3 работают в противофазе если В -м цикле Тц запись текущей информации производится в ОЗ У 2, то В этом же цикле иэ ОЗУ 3 производится считывание информации, накопленной в нем в (-1)- -м цикле и наобОрОт. Такой режим Обеспечивается подачей на ОЗУ 2,3 соответствуюц)их сигналов от второй и третьей групп адресных ВыхОДОВ блока 1 синхрОнизации (его структура будет рассмотрена позднее), Для примера на фиг.З в,г показаны наиболее высокочастотные адресные сигналы для ОЗУ 2,3 - А 1 г (фиг,З г,) и Р 1 э (фиг,Зе) соответственно, и наиболее низкочастотные - Аа (фиг,ЗВ) и Акз (фиг,Зд), а также сигнал.5 (Я/В)2 (фиг.Зж) управления режимом записи- считывания для ОЗУ 2 (О - запись, 1 - считывание).В рассмотренном варианте предусмот рена обработка потока х(пТ) в восьми частотных каналах. При этом за время одного -го цикла Тц обработки из ОЗУ 2 (или ОЗУ 3) 16 раз подряд производится считывание М=512 бит сигнала х(пТ), поступивших на 15 вход устройства в предыдущем (-1)-м цикле,Структура сигналов на выходе ОЗУ 2,3 показана на фиг,Зз,и, Прием одной частотной составляющей производится за время (1/8) Тц, за зто время указанные бит считываются 20 из соответствующего ОЗУ 2 или 3 раза подряд и поступают на согласованнцй фильтр (коррелятор), построенный на ПЗУ 6, элементе 12 ИСКЛЮЧАЮЩЕЕ ИЛИ, двоичном 8 и реверсивном 7 счетчике и дешифраторе 25 9. Работа корреляционного фильтра приприеме одной частотной составляющей заключается в вычислении величиный - 130 1-1 = х(пТ)здп(зп(2 лйпт+и =ОЫ - 1+1 х(п Т.) 3 дп (соз(2 ж 1 ПТ)1 (1) и =огде Р - результат обработки в -м частотном канале, В равенстве (1) подразумевается, что величинц х (пТ), здп (,) (знак числа) принимаютзначение + . На практикеотрицательнце значения отображаются логическим нулем и равенство (1) приводится к ВИДУН - 1-=(х(п Т ЯВ (и Т) - (х(пх)Я 45 и=оЯ 5(пТ.(х(пТ)(+)и=о,1 С(и т) - (х(п т) Рс) (и Т(2)где + - операция "И СКЛ ЮЧАЮЩЕ ЕИЛИ" (реализуется на элементе 12), а 31(пт), Спт) - последовательности значений соответствующих знаковых функций в(1), в который отрицательные значения Отображаются логическим нулем, Далее равенство (2) приводится к видуй - 3Яс 1 =Я х(п Т)Г;81(п Т) (4) и =о до тех пор, пока на выходе двоичного счетГ = 2 й/2-Яс+1 й/2- Сс 4 (3) чика 8 не появится число ч/2, после чегогде сработает дешифратор 9 и направление счета меняется на прямое. В начале второй5 половины интервала тд - то двоичный счетчик 8 снова обнуляется сигналом Оз (фиг,Зк)и реверсивный счетчик 7 снова начинаетработать на вычитание до тех пор, пока навыходе двоичного счетчика 8 не накопитсяп=о 10 число И/2, после чего направление счетаЗначения 1, С 1 для каждой частоты б менЯетсЯ на прЯмое. Такой алгоритм Работыхранятся в ПЗУ 6, Ниже приводится пример обеспечивает формирование на выходе реразмещения информации в ПЗУ 6, При час версивного счетчика 7 к концу интервала тдтотедискретизациидельта-модулированно- - 11 о величины Е; /2, где Г определяетсяго сигнала х(пТ) 32 гКц и длительности цикла 15 Равенством (3) (при 1=1).обработки 16 мс в каждом цикле обрабаты- Результат обработки на интервале тд -вается чбит сигнала х(пТ), и для каждой 11 о фиксируется в блоке 10 стробирования,выделяемой частотной составляющейв на коорый подается сигнал О 4 (фиг.Зм) отПЗУ 6 должно в соответствии с выражением блока 1 синхронизации, стробирование осу(1) хранится 512 х 2 в однобитных весовых 20 ществляется передним фронтом этого сигкоэффициентов, соответствующих величи- нала.Очевидночтодлятого,чтобыизбежатьнам з 1 дп(зп( 2 д 1 пТ)Ци з 1 дп соз(2 лпТ)1 сбоев импульсы О 1(фиг.Зл) разрешения усПри количестве выделяемых частот 1, тановки Реверсивного счетчика 7 должныравном, например, 8, требуемый обьем ПЗУ быть слегка задержаны относительно пере 6 равен таким образом 512 х 2 х 8=7 кБайт, 25 дних фронтов сигнала О (фиг,Зм), ТакимВ приведенной таблице дано содержи- обРазом, результат обработки на частоте 1,моетехячеек ПЗу, вкоторыххранятся веса- пРоведенный на интервале тд - 11 о, присутвые коэффициенты, обеспечивающие прием ствует на выходе блока 10 стробирования вчастот 11, тз (интервалы тд - 1 ю и 111 - т 2 на течение следующего интервала то - 111фиг,Зн), Для остальных частот ячейки ПЗУ 6 30 (фиг,Зн). Аналогично производится обработзаполняются аналогичным образом, Нуле- ка отРезка сигнала х (пТ) и в других частотвые и отрицательные значения знаковых ных каналах с той разницей, что нафункций здп(.) задаются, как уже отмеча- интервале тю - 111 из ПЗУ 6 считываютсялось,логическими нулями. Всоответствиис весовые коэффициенты Я 2(пТ), С 2(пТ) длявычислениями по равенству (3) в начале каж следующей частоты т 2, на интервале 111 - 112дого интервала (1/8) Тц (фиг.Зз), в котором для частоты т 3 т.д. Все результаты обработпроизводится прием одной частоты (напри- ки за один цикл Тц по всем частотам запимер, пусть на интервале тд - 1 о (фиг.Зн сываются в одно из ОЗУ 4 и 5, которыепроизводится прием частоты(в реверсив- также, как и ОЗУ 2,3 работают в противофанцй счетчик 7 записывается число д, а дво 40 зе - если в 1-м цикле осуществляется записьичный счетчик 8 обнуляется, Сигналы Оз, ц в ОЗУ 4, то из ОЗУ 5 производится считываразрешающие обнуление и установку и фор ние, и наоборот,мируемые в блоке 1 синхронизации, показа- Выходные сигналы ОЗУ 2,3 поступаютнц на фиг.З к;л, соответственно. На элемент на блок 13 объединения, с выхода которогоИСКЛЮЧАЮЩЕЕ ИЛИ 12 в первой полови инФормация теперь считывается непрерывне интервала тд - 11 о из ПЗУ 6 считываютсяно в каждом цикле, либо из ОЗУ 4 либо иэзначения 31(пТ), а во второй С 1(пТ) и в тече ОЗУ 5 (для ОЗУ 2,3 аналогичную функциюниекаждойполовиныуказанногоинтервала ыполнял элемент ИЛИ 11), Считцваниесчитываются й значений сигнала х(пТ), на- производится с существенно более высокойкопленные за предыдущий цикл Тц50 частотой, чем запись, За время , (фиг,4 а);В каждом такте работы счетчиков 7,8 равное длельности одного символа сигразрешается лишь в том случае, если выход- нала х(пТ) на входе устройства, через блокной сигнал элемента ИСКЛЮЧАЮЩЕЕ 13 обьединения от одного из ОЗУ 4 и 5ИЛИ 12 равен нулю, то есть когда значения последовательно считываются результатых(пТ) и 3(пТ)/ или С (пТ)/ одинаковы, При 55 обработки (О 1 з, фиг.4 б) на всех частотах, тоэтом в начале первой половины интервала же повтоРяется и в следующих интервалахиз ПЗУ 6 считываются значения Я (пТ) а то, аким образом в течение одного циклареверсивный счетчик 7 работает на вычита- ч Рзультаты обработки на всех частотах вние тактовых импульсов, что продолжается предыдущем цикле Тц считываются М - -512раз подряд. Наиболее высокочастотный ад 1683181ресный сигнал, подаваемый на то из ОЗУ 4 и 5, из которого в данном цикле производится считывание, показан на фиг.4 в (сигнал-1 частоты 41 о). В каждом интервале то(фиг,4 а) в течение одноо цикла Тц от шестой группы адресных выходов алака 1 синхронизации на блок 14 сравнения паступаот двоичные числа, соответствующие Определенным значениям порогов Р срабатывания, с нарастанием от минимальных значений в начале цикла Тц к максимальным значениям в конце цикла, которые сравниваются в блоке 14 с результатами фильтрации на различных частотах (01 з, фиг.4 б), поступающим в каждом интервале 1 а с выхода блока 13 обьединения, В результате сравнения формируются однобитные значения (О или 1), говорящие а наличии или отсутс 1 вии срабатывания в каком-либо частотном канале при данном значении порога Р. Подсчет числа срабатываний на каждом временном интервале то(фиг.4 а) производится счетчиком 15, абнуляемым в начале каждого интервала 1 О 1 короькими импульсами. 05 (фиг,4 Д), поступающими спятого тактового выхода блока 1 синхронизации. Счет производится по передним фронтам сигнала Об (фиг,4 е), подаваемого на тактовый вход счетчика 15 числа срабатываний от шестого тактового выхода блока1 синхронизации, и происходит лишь в тех случаях, когда на его вход разрешения счета подается высокий уровень сигнала с выхода блока 14 сравнения в текущем интеавале Л 1 =1/8 Го (фиг,4 г), Также передними фронтами сигнала О; (фиг,4 е) выходнаяин формация блока 14 сравнения на каждом интервале 0 "(фиг,4 а) последовательно вписывается в регистр 1 б, на выходе катсрого к концу каждого интервала 1 О (фиг,4 а) будет в параллельном позиционном коде появляться информация о количестве и номере частотных каналов, в которых г,роизошло срабатывание (прием частоты) при текущем значенли порога. Выходной си нал счетчика 15 числа срабатываний поступает на информационный вход анализатора 17 числа срабатываний, тактируемый сигналом От (фиг.4 ж) подается с седьмого выхода блока 1 синхронизации. К концу интервала 1 О(фиг,4 а) единица появится на выходе элемента 21 И только в том случае, если на вход анализатора 17 поступает числа 2 (О 1 О в двоичной Форме), л толька в этом случае сработает Д-триггер 22, например, на интервале Т 1 количества срабатываний (сигнал 014, фиг.4 г) равнялось трем на частотах 11, т 4, 75), поэтому к моментут 1 стробиравания число нв выходе счетчика 15 равняется трем (ОО 1), на выходе элемента И 21 нулевой сигнал и Д-триггер 22 остается в нулевом состоянии. На интервале Т 2 (фиг.4 е) на блок 14 сравнения от шестой группы выходов блока 1 синхронизации поступает новое значение порога Р, большее, чем на интервале Т, и срабатывание на частоте, имевшей наиболее низкий уровень из трех(т 1,14,15), устраняется. В результате к моменту 12 (фиг.4 ж) на выходе счетчика 15 срабатываний присутствует число 2 (010) и Д-триггер 22 устанавливается в единичное состояние. К этому же моменту информация о номерах двух сработавших частот (т 1, ) в виде позиционного кода присутствует на выходе регистра 16, откуда она переписывается в блок 18 фиксации результата передним фронтом выходного сигнала 017(фиг,4 з) анализатора 17 числа срабатываний, где и удерживается до Окончания текущего цикла обработки Тц, В начале каждого последующего цикла Тц блок 18 фиксации результата обнуляется коратклм импульсом с восьмого тактового выхода блока 1 синхронизации, Таким образом в каждом цикле обработки Тц на выходе устройства (на выходе блока 18 фиксации результата) появляется информация о срабатывании на двух частотных составляющих входного сигнала, имеющих наибольшие уровни па сравнению с другими.Формула изобретения Цифровой приемник дельта-модулированных сигналов многочастотных кодов, содержащий блок синхронизации, вторая и третья группы адресных выходов которого соединены с адресными входами соответственно первого и второго оперативных запоминающих устройств, выходы которых подключены через элементы ИЛИ к первому вхадуэлемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к выходу постоянного запоминающего устройства, вход которого соединен с первой группой адресных выходов блока синхронизации, первый гактовый выход которого соединен с входом начальной установки реверсивного счетчика, вход разрешения счета которого подключенн к выходу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и к выходу разрешения счета двоичного счетчика, вход установки нуля которого г 1 одключен к третьему тактовому выходу блока синхронизации, второй тактовый выход которого соединен с тактовым входом двоичного счетчика и с тактовым входом реверсивного счетчика, вход направления счета коараго подключен к выходу дешифратора, входы которого подключены к соответствующим выходам двоичного счетчика, при этом информационные входы первого и второгс оперативных запоминающих уст1683181 1 О Адрес ячеяки Номерячейки А Аг( Ар А А,. А Лс АГ А О О о о о оО О О0 О О О 0 511 52 1023 0 О О, 2048 01 0 О О 0 0 0 0 2559 О 1 О 0 1 1 ", 1 1 2560 0 1 О 1 0 0 0 О 0 256 00 1 О 0 0 0 О ЗО 21 О 1 О ройств объединены и являются входом приемника, о т л и ч а ю щ и й с я тем, что, с целью повышения достоверности приема путем устранения ложных срабатываний, в него введены третье и четвертое оперативные запоминающие устройства, блок объединения, блок сравнения, счетчик числа срабатываний, анализатор числа срабатываний, регистр, блок фиксации результата и блок стробирования, выходы которого соединены с попарно объединенными информационными входами третьего и четвертого оперативных запоминающих устройств, выходы которых попарно объединены и подключены ко входам блока обьединения, выходы которого подключены к информационным входам блока сравнения, выход которого соединен со входом разрешения счета счетчика числа срабатываний и информационным входом регистра, выходы которого соединены с информационными входами блока фиксации результата, первый тактовый вход которого подключен к восьмому тактовому выходу блока синхронизации, пятыЙ тактоВый ВыхОд которого со единен со входом установки нуля счетчика числа срабатываний, выходы которого подключены к информационному входу анали затора числа срабатываний, тактовый входкоторого подключен к седьмому тактовому выходу блока синхронизации, шестой тактовый выход которого соединен с тактовым входом счетчика числа срабатываний и с 10 тактовым входом регистра, четвертая, пятаяи шестая группы адресных выходов блока синхронизации соединены с адресными входами соответственно третьего оперативного запоминающего устройства, четвертого опе ративного запоминающего устройства и блока сравнения, четвертый тактовый выход.блока синхронизации соединен с тактовымвходом блока стробирования, информационные входы которого подключены к;.ь 20 реверсивного счетчика, при этом выход анализатора числа срабатываний соединен со вторым тактовым входом блока фиксации результата, выходы которого являются выходами приемника,1683181 Нродолаение таблицы Содержимое ячейки адрес ячейки А А., А ОО О О О О = Б /О/1О 0 0 1 вз.8 п(въп(2 т 7 Т, Т = Б (Т) 1023 1 1 1 Я 1 дд(сцз(2 В 11 Т) ) С (81 Т) Э 2048, 0 0 0 0 0 = Б(0) О О 1 в 18 п(в 1.п(2 Ед Т = Б (Т)1683181 оставитель О,Геллехред М.Моргента Корректор Н,Король убане едакт изводственно-издательский комбинат "Патент", г, Ужгород, ул,Гага Заказ 3422 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4749433, 12.10.1989

ЦЕНТРАЛЬНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ СВЯЗИ

ОХЛОБЫСТИН ЮРИЙ ОЛЕГОВИЧ

МПК / Метки

МПК: H04L 27/32

Метки: дельта-модулированных, кодов, многочастотных, приемник, сигналов, цифровой

Опубликовано: 07.10.1991

Код ссылки

<a href="https://patents.su/8-1683181-cifrovojj-priemnik-delta-modulirovannykh-signalov-mnogochastotnykh-kodov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой приемник дельта-модулированных сигналов многочастотных кодов</a>

Предыдущий патент: Устройство защиты от ошибок

Следующий патент: Устройство для распознавания объектов на двумерном поле

Случайный патент: Способ изготовления точных шкал