Распределитель вызовов12

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 428576

Авторы: Голомолзина, Городецкий, Иэаб

Текст

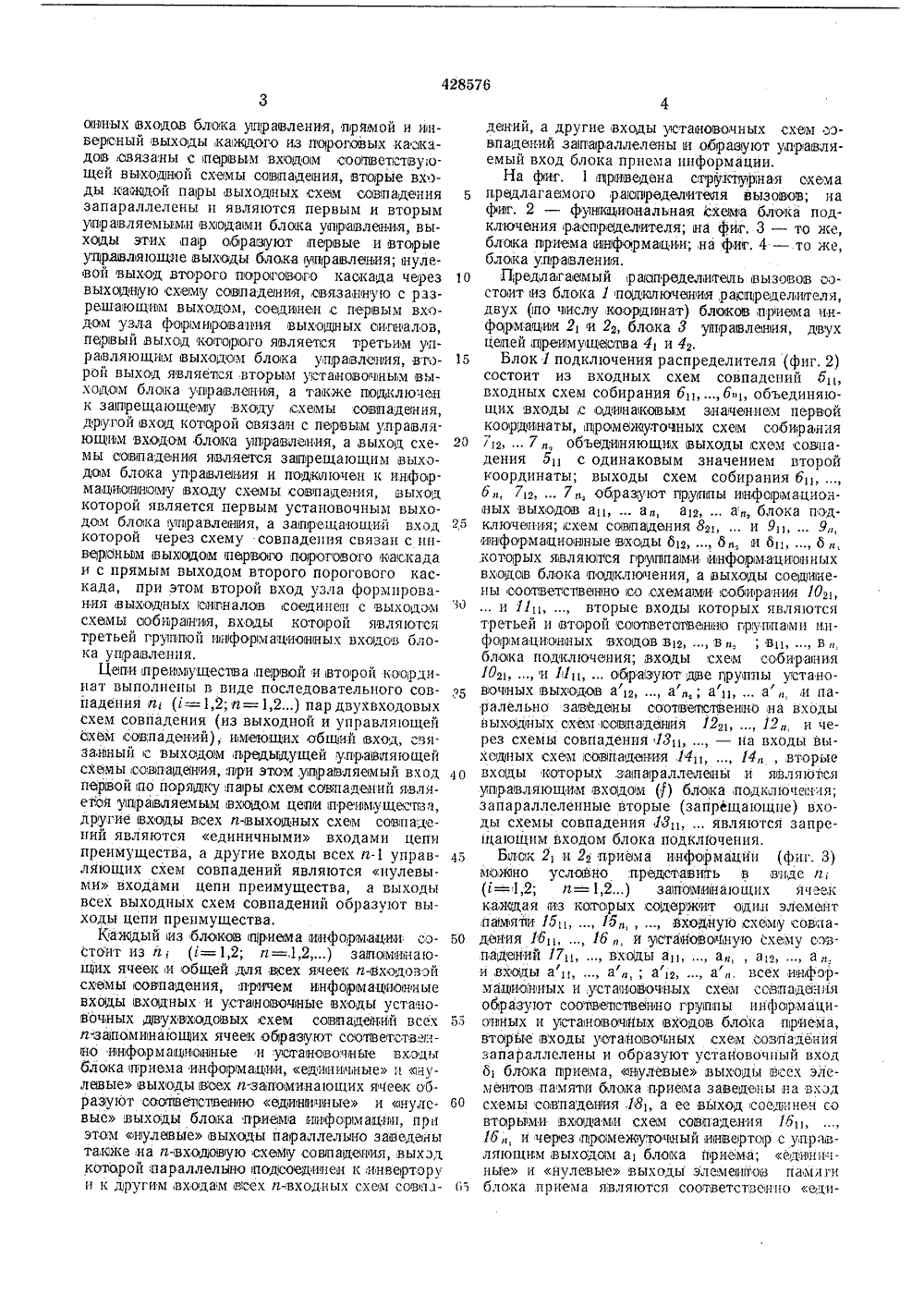

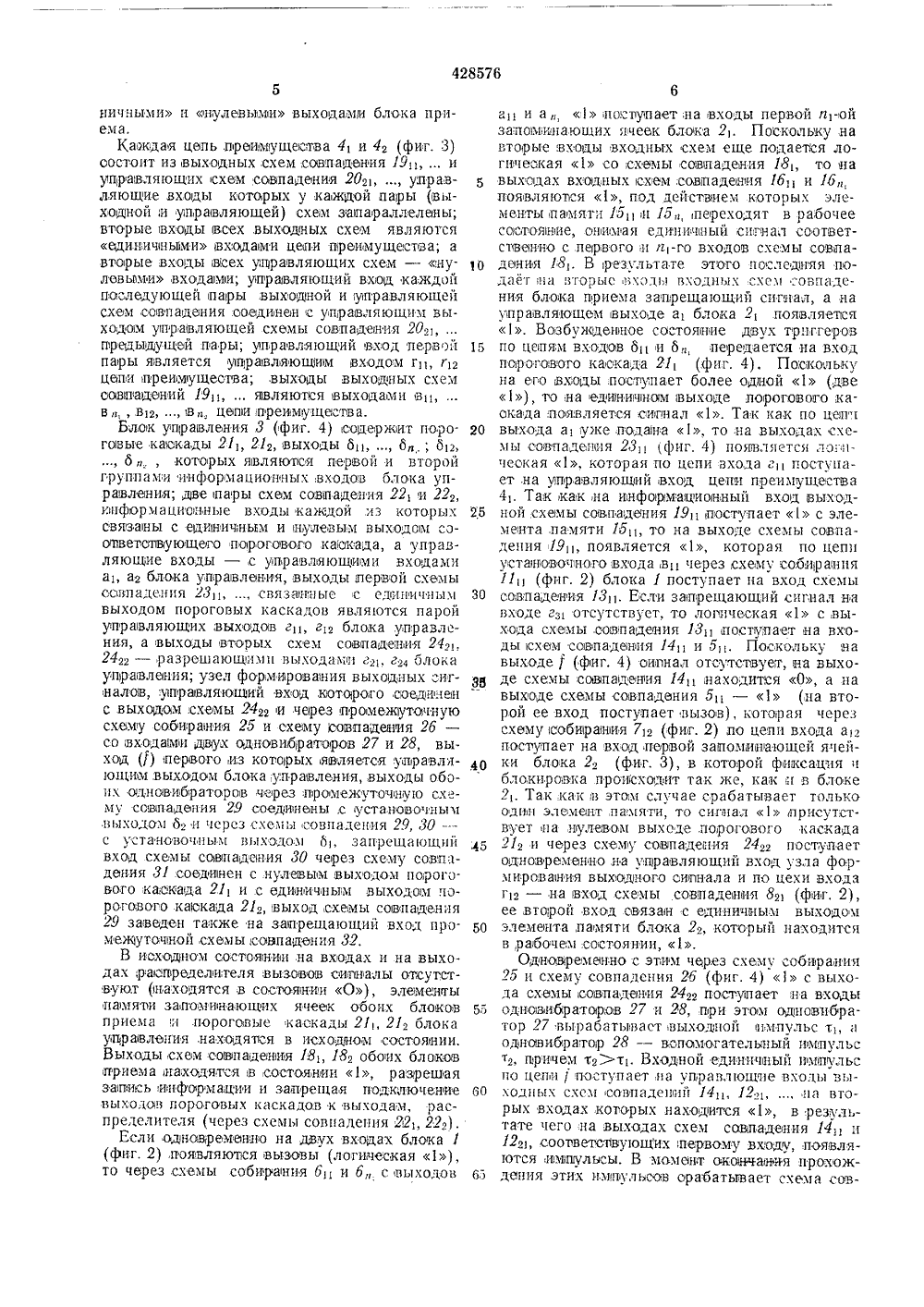

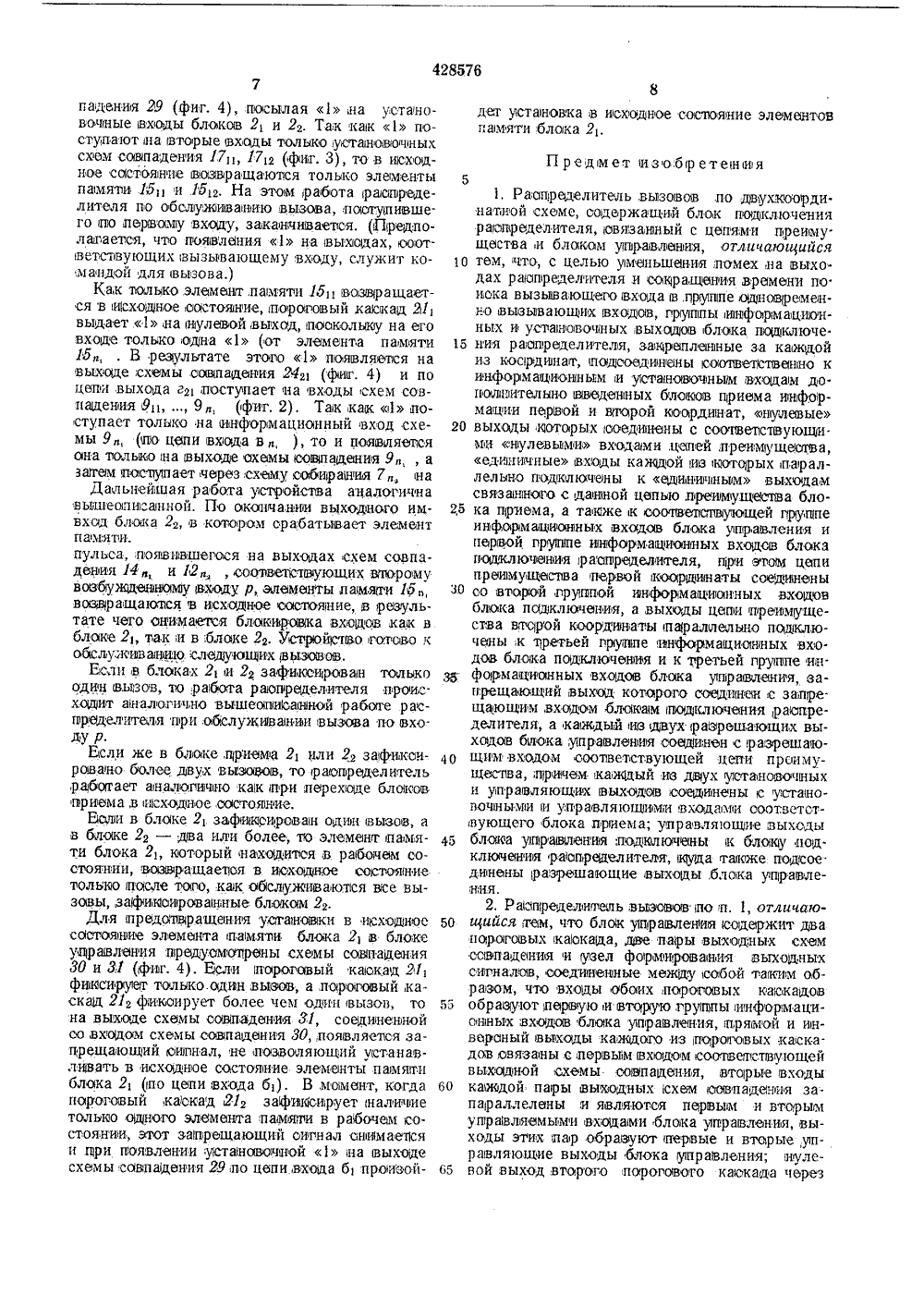

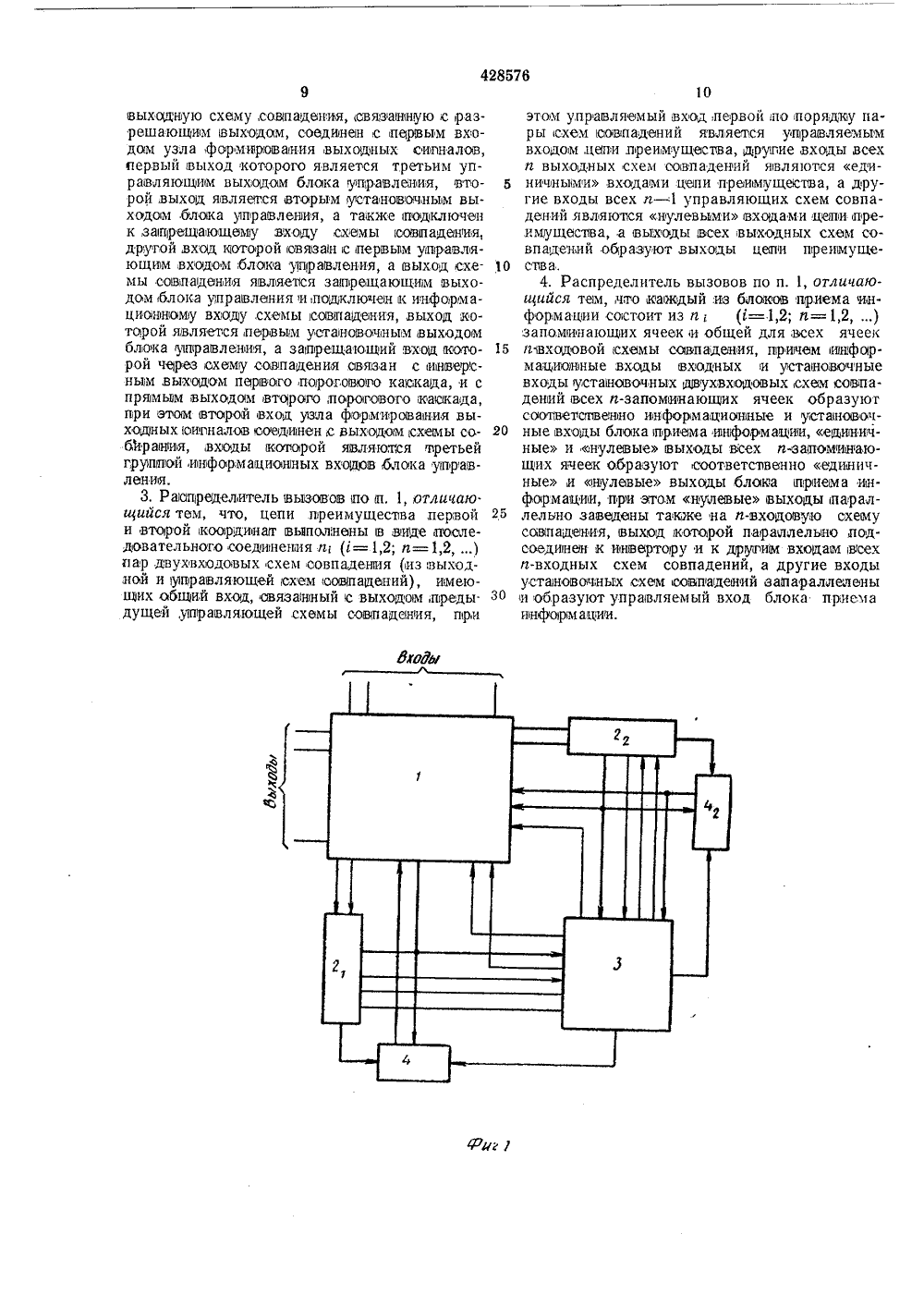

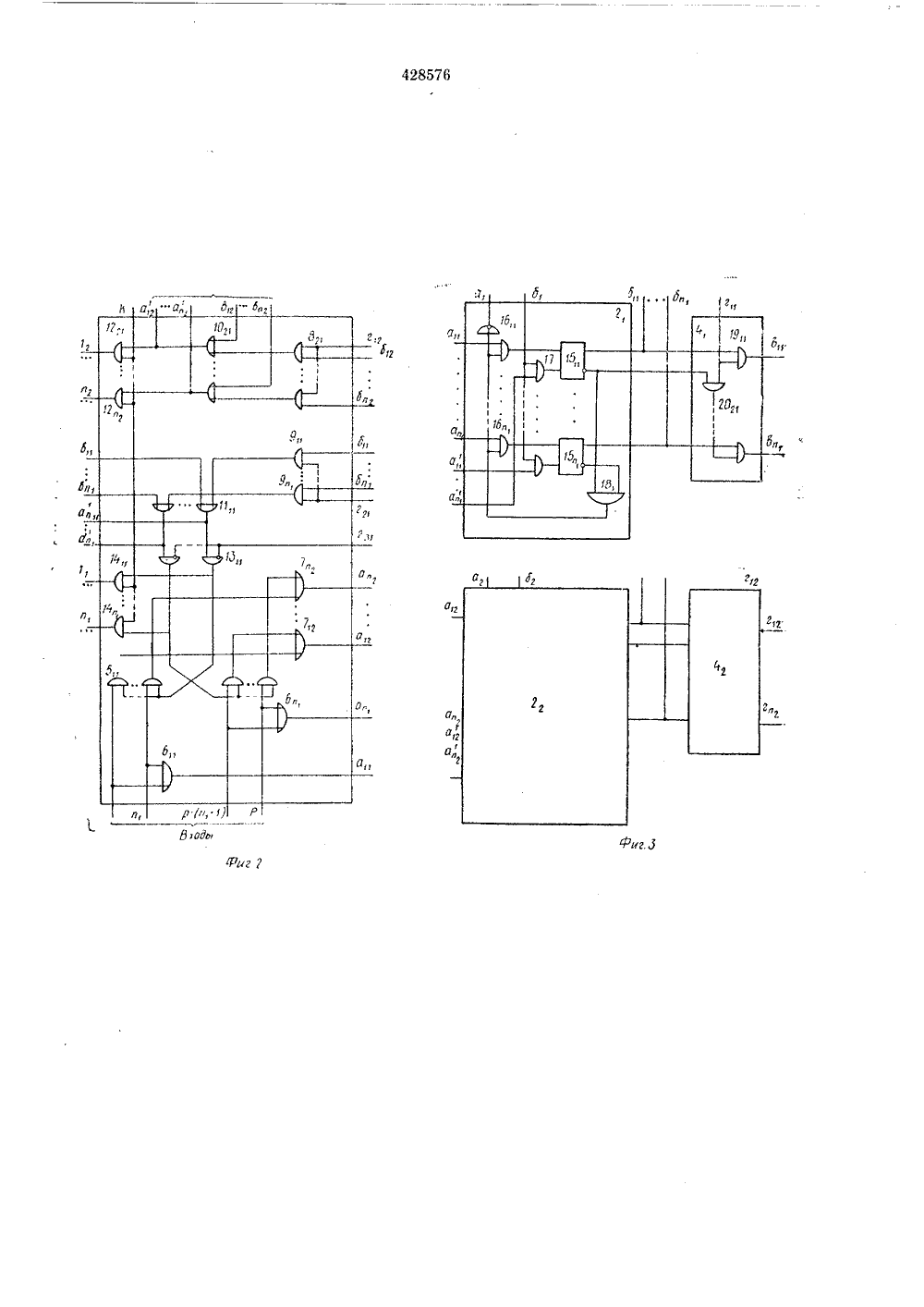

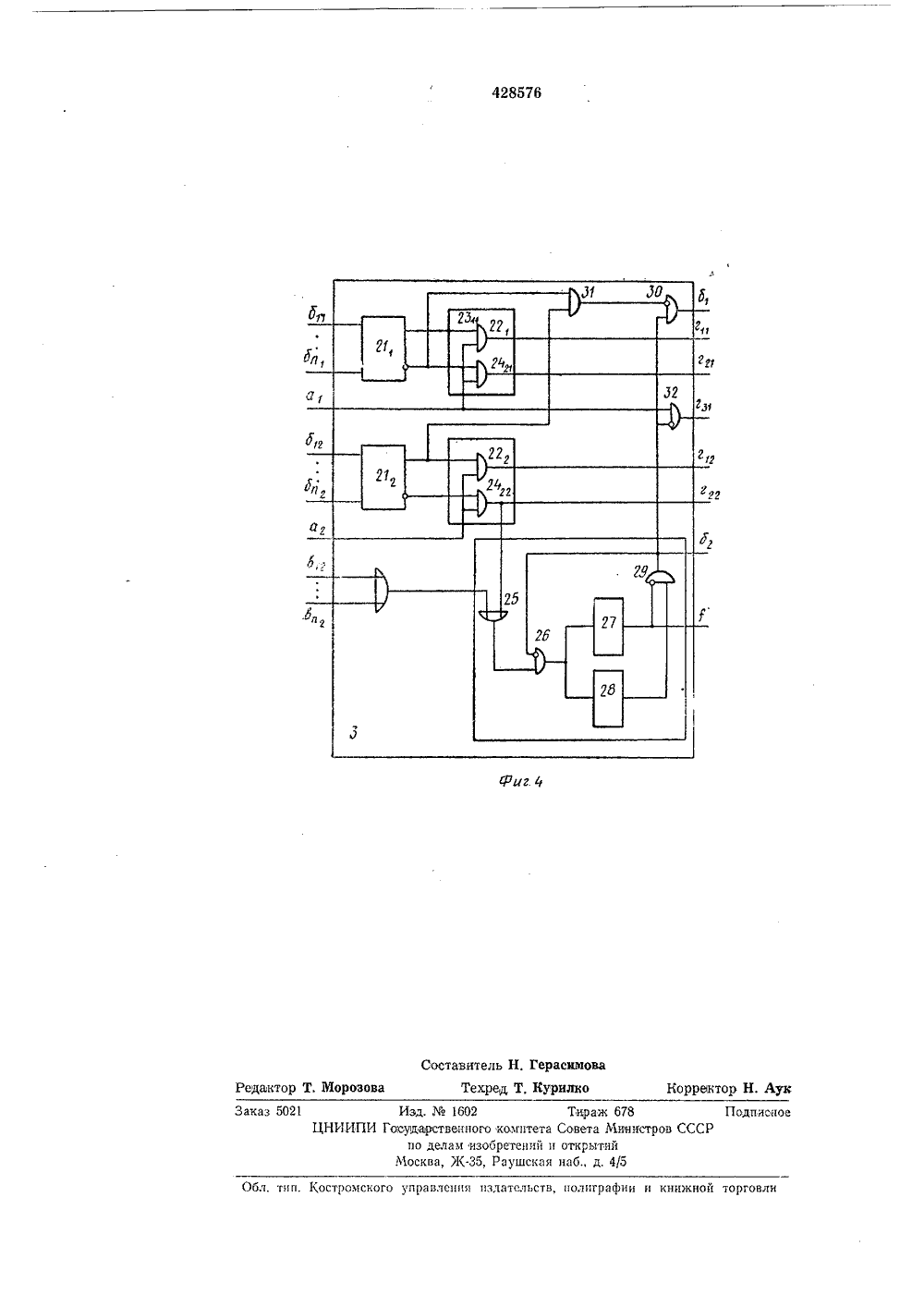

О П И С А Н И Е щ 428576ИЗОБРЕТЕН ИЯ Союз Советских Социалистических Республик(51) Ч. Кл, И 041 3/72 пп 1 соединенпех заявОя о -Гкударственный комитет Совета Министров СССР но делам изобретений и открытий(72) Авторы В. И. Городецкий и С, В. Голомолзииа ИЗОбР ЕТЕ 1 П 1 Я(54) РАСПРЕДЕЛИТЕЛЬ ВЫЗОВОВ 11 зобрстсппс отОПтся к област 11 изба 1 рательных устройств и может быть использовано в савстемах массового обслуживания, в частяости в автомати еоиих телеграфных, системах.Известен ра 1 спределитель вызово 1 в, содержа- тциГ блОк подкл 1 оченвия,ряОпдределителя, цепи преимущества и блок управления.Однако на выходах такого 1 распредел 1 Те.,1 я при определео 1 ном сдвиге мооентов появления вызовсв на разиных входах либо,при о 1 пределе 1- ном соотпошении временных,паранетроев входящих в него элеьеготов возмогно появле 1 нпе помех, что может привести к неправильной работе авяза 1 нных с ра 1 апределителем устройств.С целью уменьшения помех на выходах рас пределителя и сокраще 1 ние времени по 1 иска вызывающего входа в пру 1 П 1 пе однсвреме 1 нно вызьввающих,входов в,предлагаемом;рас 1 пределт 1- теле пру 1 Ппы,инфорхЯцианных и устао 1 овочных выходов блока подключен 1 я раопределителя, 2 О закрепленные за каждой из коюрдинатподсоедпнены соответственно к информационным и установо оным входаы дополнительно,введенных блоков приеза и 1 нфорхЯции первой и вго рой коордпдат, нулс 1 вые выходы которы 25 сослсИсиы с соответству 1 ощпм; пулевым и входамс цепей преимущества, едв 1 и нные входы каждой пз которых,параллельно подключены к едини оным выходаы связанного с да 1 нноц цепьО,Преи 1 мущества блока при Омя, я тякже к соответстВу 10 щей груп 1 пе информационных входов блока управления и к ервой группе информационных входов блока подключения распределителя, прп этом цепи преимущества первой координаты соединены со второи группой пнформациопнь 1 х входов блока подключения, а выхОды цс 11 и преимущества Второй КООрдппять 1 параллельно подключены к третьей группе пнформациоооных входов блока подклю 1 ения и к претьей групне информационных входов блока у 1 правления, запрещающий выход которого соединен с запрещающим входом блока подключения распределителя, а каждый из двух разрешающих выходов бло 1 ка улравления соедз 1 им с рязрешающим входом соответ 1 ствующе 11 цепи преимущества, причез каждый из двух уста- НОВООНЫХ И УПРЯ 1 ВЛЯЮЩИХ ВЫХОДОВ СОЕД 1 И 1 ЕН С установочными и управляющими входами соответствующего блока приема; управляющие выходы блока управления подключе 1 ны к блоку подключения распределитеся, куда также подсоединены разрешающие выходы блока управления.Кроме того, блок управления содержит двапороговых каскада, две пары выходных схем совпадения и узел фо 1 рзИ 1 рова 1 ния выход 1 ных сипналов, соедине 1 нные между собой таким образом, что входы обоих лороговых каскадов образуют первую и вторую пруппы пнформацпэвных входов блока уггравления, прямой и инвер(сньгй выходы,кагждого из пэрюгавьгх каскадов связаны с первьгм входом сюответству;ощей выходной схемы совпадания, вторые входы каидой пары выходных схегм совпадения запараллелены и являются первым и вторым управляемьгии входами блэка уп)равления, выходы этих пар о 6 разуют первые и вторые уцрвалягощгие выходы блока управления; гнулевой выход второго порогового каскада через выходящую схему совладения, связанную с рззрешающии выходом, соединегг,с первым вхюдэм узла формировання выходных оигкалов, первый выход которого является третьим управляющим выходом блошка управления, второй выход является вторым установочным выходом блока управлания, а также подключен к зап 1 рещагощему входу схемьг совпадения, другой вход которой связан с первым управляющвм входом блока у 1 правдения, а выход схемы сювптадения является заорещающим выходэм блока управления и подкдгочен к иггформациюнноъгу входу схемы совпадення, выход которой является первым установочным выходогм блэка управленвя, а запрещающигг вход которой через схему совпадения связан с инвердньвм выходом первого пю)рогового каскада и с прямым выходом второго порогового каскада, при этом второй вход узла формирования вьгходньгх сивналов соединен с выходом схемы аобвранчя, входы которой являются третьей гру 1 ппюй иифэрмациюнных входов блока управленггя.Цепи лреииущества пе)рвюй и второй координат выполнены в виде последовательного совпадения и, (г=1,2; и=1,2.) пар двухвходовых схем совпадения (из выходной и управляющей схем совпадений), имелющих общнй вход, связанный с вьгхэдо)м предыдущей управляющей схемы совпадения, гври этом,управляемьгй вход первой по порядку,пары,схем совпадений явлггегоя угвр авляемььм,входом цели превмугцеств а, другие входы всех и-выхюдньгх схемам совпаденийй являются единичными входами цепи преимущества, а другие входы всех иуправляющих схем совпадений являются нулевыми входами цепи преимущества, а выходы всех выходных схем совпадений образуют выходы цепи преимущества,Каидьгй из блоков приема информации соСтоит из и; (г=1,2; и=,1,2,) зайэмигнаюгцих ячеек и общей для всех ячеек и-вхюдовой схемы совпадения, нричем и,нформациюиные вхо 1 дьг входных и установючньге входы установочных двухвхгэдовых схем совгпаде 1 нигг всех изапэминаюшгих ячеек образуют соответсгввсгно инфэрмацгловные и установочные входы блэка приехга информации, едвнич 1 ные и нулевые выхюдьг всех п.запоминагощих ячеек образуют сээтветствегвню единвчньге и нулевые выходы блэка приама явформацлги, при этом нулевьге выходы параллелыно заведейы такгке,на и-входювую схему совпадения, выход которой параллелыню пэдеоедигнен к,инвертору и к другим входам всех ивходных схем соил 5 10 15 20 25 Зд з 5 40 45 50 55 60 нз даний, а другие входьг установючньгх схем соьпадений запараллеленьг ы образуют управляемый вход блока приема информации.На фиг. 1 вриведена сггруктурная схема предлагаемого,распределитеая вызовов; на фиг. 2 - фувкциональная схема блока подключения распределителя; Ба фиг, 3 - то же, блока приема цвформации;,на фиг. 4 - то же, блэка увравлен ия,П,редлагаемый раапредедипедь вызовов состоит из блока 1 подилючон 1 ия,расщределюеля, двух (по числу коордвнат) блоков приема инфэрмации 2 г и 2 г, блока 3 угправлегвия, двух цепей,цреимущ 6 ства 4 г и 4 г.Блок 1 подключения распределителя (фиг. 2) состоит из входных схем совпадений бц, входных схем собирания бц, , б ц объединяющих входы,с одинаковым значениехг первой координатьг, дромегиутачных схегм собиранггя 7 г,7,объединяющих выходы схем совчгадения Бц с одинаковым значением второй координаты; выходы схем собирания б,г, , бл, 7 гг, ". 7 л., образуют прупльг информацион. ных выходов ац,а, агг,а блока подключения; схем совпадения 8 гци 9 ц,9, внформагциовные входы бгг, , б ., н 61 ц , б , которых являются прувпами инфориациояньгх входов блока подключения, а вьгхады соедигнены соответственно со схемами собирания 10 гци 11 ц вторые входы которых являются третьей и второй соютветотвенню группами информациэнньгх входов в 1 г в ,; вц, , в , блока подклгэчения;,входы схем собирагния 10 гц, и 11 ц,образуют две пруппы установючньгх вьгхюдэв а, , а; ац,аи паралельно заведены соотвепственно на входы вьгхэдньгх схем ссвпадения 12 12, и через схемы совпадения 13 ц, , - на входы выходных схем совпадения 14 гц , 14, вторые вхоаьг которых запараллеленьг и являются управляющим входом (1) блошка подкглючеичя; запараллеленные вторые (запрещагогцие) входы схемы совпадения Иц,являются запрещающим входом блока подключения.Бдск 2, н 2, приема информацйц (фиг. 3) моМно условно гирддсаавиь в виде гг; (К=1,2; п=1,2) запоывнающггх ячеек каждая из которых содвр 1 жит одил элемент пагмяти Иц, , 1 б , входную схему совдадения 1 б,ь , 16 и устанювобную схему совпадений 17 ц, , вхэдьг агц, а аг, , а, и,входы ац , а,; агг, , а, всех ивфэрмациюнных и установочных схем совпадения образуют соотвепственно группьг информациовных и установэч 1 ных входов блока прйема, втэрьм входы установочных схем совпаденйя запараллелены и образуют установочный вход б, блока приема, н 1 улевьге выходы всех элемевгов памяти блошка приема заведеньг на вход схемы совпадения,1 ог, а ее выход соединен со вторыми вхюдами схем совпадения 1 бц, 16 , и черкез промежугочяый инвертор с управляющим выходом аг блока приема; едвн;гчные и нулевые выходы элемеигов памяги блока приема являются соответствепно единичными и нулевым 1 и выходами блока приема.Каждая цепь,преимущества 4, и 4 г (фиг. 3) состоит из выходных схем, совпадения 19,и управляющих схем совпадения 20 г 1, , управл,яющие входы которых у каждой пары (выходной:и управляющей) схем за)параллелены; вторые 1 входы всех выходных схем являются единичньнми входами цепи преимущества; а вторые входы всех управляющих схем - нулевьнми входами; управляющий вход каждой последующей пары,выходной и управляющей схем совпадения соединен с управляющим выходоьм управляющей схемы совпадения 20 г, предьндущей пары; управляющий вход перв й пары является управляющим входом г, г 1 г цепи преимущества; .выходы выходных схем совпадений 19,ьявляются выходами в,в, в 1 г, ., в цепки,преемущеетва.Блок управления 3 (фиг. 4) содержит пороговые ка 1 скады 21 21 выходы 6,1, , 6; 61 г, ., 6 которых являются первой и второй группами информационных входов блока управления; две пары схем соввадення 22, и 22 информацисвные входы каждой из которых связаны с единичным и кулеаьнм выходом соощветотаующего порогового ка(екада, а управляюцние входы - ,с управляющими входами аь аг блока управления, выходы лервой схемы освпадения 231 ь , связанные с единичным выходом пороговых каскадов являются парой управляющих,выходов г, гг блока управления, а выходы вторых схем совпадения 24 г 24 г, - разрешающими выходами г, ггблока управления; узел формирования выходных ситналов, у 1 правляющий вход,которого соединен с выходом, схемы 24,г и через промежуточную схему собирания 25 и схему совпадения 2 б - со входами двух одновибраторов 27 и 28, выход (1) первого из котсрых является управляющиьм выходом блока, управлениявыходы обоих одновибраторо 1 в через промежуточную схему совпадения 29 соединены,с устансво 1 нным выходом бг и через схемы совпадения 29, 30 -- с установочным выходол 6 ь запрещающий вход схемы совпадения 30 через схему совпадения 31 соединен с нулевьнм выходом порогового каскада 211 и с единичным выходсм чсрогового каокада 21 г, выход,схемы совпадения 29 заведен также на запрещающий вход промеж 1 уточной схемы соападения 32.В исходном состоянии на входах и на выходах,распределателя:вызовов ситвалы отсутствуют (находятся,в состоянии 0), элеменеы памяти запоминающих ячеек обоих блоков приема и пороговые каскады 21 ь 21 г блока управления находятся в исходном состоянии.Выходы схем совпадения 18, 18 г обоих блоков приема находятся в состояили 1, разрешая заспись ичнформации и эапрещая подквючение выходов пороговых каскадов к выходам, распределителя (через схемы совпадения 22 ь 22 г).Если однсщременоо на двух входах блока 1 (фиг. 2),появляются вызовы (логическая 1), то через схемы собнграния 6, и бс.выходов 5 10 15 20 2,5 30 36 40 50 55 60 65 а 11 и а, 1 поступает,на входы первой п,-ой запоминающих ячеек блока 2 ь Псскодь 1 ку,на вторые:входы входных схем еще подается логическая 1 со,схемы совпадевия 18 то на выходах входных схем,совпадения 16 и 16, появляются 1, под действием которых элементы памяти 15,н 15, переходят в рабочее ссотояние, онимая едини нный сигнал соответственно с первого,и п,-го входов схемы совпадения 18,. В результате этого последняя подает на вторыс,.,хсдь 1 входных схем:овпадения блока приема запрещающий сигнал, а на управляющем выходе а 1 блока 2, появляется 1. Возбуждегнное состоявве двух триггеров по цепям входов с 11 и 6, передается на вход порогового каскада 21 (фиг. 4), Поскосльку на его входы поступает более одной 1 (две 1), то на единичном выходе порогового каскада появляется сипнал 1. Так как по цепи выхода а 1 уже,подана 1, то на выходах схемы совпадения 231 фиг. 4) появляется логическая 1, которая по цепи входа г,1 поступает на управляющий,вход цепи преимущества 4 Так как,на информац 1 иснный вход выходной .схемы совпадения 191 проступает 1 с элемента памяти 15,ь то на выходе схемы совпадения 191 ь появляется 1, которая по цепи устанювочного входа в, через схему собира(нпя 11(фиг. 2) блока 1 поступает на вход схемы совпадения 13 И. Если запрещающий сигнал на входе готсутствует, то лопическая 1 с,выхода схемы совпадения 1311 поступает на входы схем совпадения 1411 и 5,ь Поскольку ва выходе ) (фиг. 4) еивнал отсутствует, на выходе схемы соапайевия 1411 находится 0, а на выходе схемы совпадения 5 - 1 (на второй ее вход поступает вызовов), которая через схему собирания 71 г (фиг. 2) по цепи входа аг поступает на вход первой заномвнающей ячейки блошка 2 г (фиг. 3), в которой фиксация ч блокировка происходит так же, как и в блоке 2 ь Так как в этом случае срабатывает только сдин элемент памяти, тс сигнал 1 присутств ет ва нулевом выходе,пофрогового каскада 21 г и через схему совпадения 24,г поступает одновременно на управляющий вход узла формирования выходного оивнала и по цехи входа г 1 г - на вход схемы совпаденая 8 г, (фланг. 2), ее,второй вход овязан с единичным выходом элемеита,памяти блока 2., который находится в рабочем состоянии, 1,Одновременно с этим через схему собирания 25 и схему совпадения 26 (фиг. 4) 1 с выхода схемы совпадения 24 гг поступает:на входы одно)вибраторов 27 и 28, при этом одповибратор 27 вырабатьнваст выходной,импульс т а однсвибратор 28 - вспомогательный пмпульс г, причем тг)ть Входной единнчвый импульс по цепи 1 поступает на управлющве входы выходных схем совпадений 14 о 12 г , на вторых входах которых находится 1, в результате чего на выходах схем савпадения 141, и 12 гь соответствующих 1 первому входу, появляются импульсы. В момент оксичан+я прохождения этих щпульсов срабатьнвает схема совпадения 29 (фиг. 4), посылая 1 на у;становочные входы блоков 21 и 22. Так как 1 поступают на вторые входы толькоустановочных схем соападения 1717 д (фиг. 3), то в исходное состояние возаращаюпся только элементы памяти 1 би 1 бд. На этом раббота раопределителя по обслуливанию .вызовапоступившего оо лервому входу, заканчивается. (Предполавается, что появлдния 1 на выходах, ооответеввующих 1 вызывающему входу, служит ко.мандой для вызова.)Как только элемент,памяти 1511 воаеращается в йсходное состояние, пороговый каскад 21, выдает 1 на ненулевой выход, поскольиу на его входа только одна 1 (от элемента памяти 1 б, . В результате этого 1 появляется на выходе,схемы ооепадения 2421 (фиг. 4) и по ценя выхода гпоступает на входы схем совпадения дп, , 9 (фит. 2). Так как 1 поступает только на информационный вход схемы 9, (по цепи вхсда в ), то и появдяегся она только на выходе схемы совпадения 9 а затем пос"пупает через, схему собираоия 7, наДальнейшая работа устройства аналогична вышеописавной. По окончаниии выходного имвход блока 2 в котором срабатывает элемент пая,яти.пульса, появившегося на выходах схем совпа. дения 14 и И соответствующих второму вовбуждевному входу р, эдементы ламяп"и 1 б вовдращаюпся в исходное состояние, в результате чего снимается блокировка входов как в блаке 2 ь так я в:блоке 22. Устройство готсво к обслуживанвю. следующих вызовов.Есдп в блоках 2 и 22 зафиксирован тодько один вьиов, то,работа распределителя происходит аналогично вышеоаиЬааной работе расврщелителя при обслужыванаи вызова по входу РЕсли же в блоке,щривма 21 или 22 зафиксированно более двух вызовов, то раовределитель ,работает анадогячно как при лереходе блоков дрвема в аеходаое состояние,Воли в блоке 21 зафиисирован одвн вызов, а в блоке 22 - два или более, то элеменч памяти блока 2 ь который находится в рабочем состоянии, вооаращается в исходное состояние тольо лосле топо, .как обслуживаются все вызовызафиислрованные блоком 22.Для лредоеаращения установки в исходнос сдстоввие элемента памяти блока 21 в блоке ущравления предуомщрены схемы соападения 30 и Л (фиг. 4), Если пороговый каскад Я 1 фиксируеп только.одын вызов, а пороговый,каскад 212 фиксирует более чем один вызов, то на выходе схемы ссвпадения 81, соединенной со входом схемы совпадения 30 появляепся запрещаюший овпнал, не;позволяющий устанавливать в исходное состояние элементы памяти блока 2 (по цепи входа б). В момент, когда пороговый .канонад 212 зафаюсирует наличие только одного элемента памяти в рабочем состоянии этот запрещающий сигнал снямается и цри проявлении установочной 1 на выходе схемы совпадения 29,по цепи входа б 1 произойдет установка в исходное состояние элементовпамяти блока 2 ьП редмет и,з обер етения1. Распределитель вызовов по двухкоорди.наткой схеме, содержащий блок подключенияраспределителя, связавный с цепями преиму.щества и блоком управленкя, отличающийся10 тем, что, с целью уменьшания лемех,на выхо.дах распределителя и соращения времени поиока вызывающего входа в,пруп(пе одновременно вызывающех входов, группы внформационных и устааовочных,выходов блока подключе.15 ния раапределителя, за 1 цреплеаные за каждойиз коорданат, подсоединены соответственно кинформационным и установочным входам до.полиюительно введенных блоков цриема ивформации первой и второй коордвнат, ненулевые20 выходы Иоторых соедивены с соотвепствукйцими ненулевыми входами цапей,преимущеогва,единичные входы каждойиа которых параллельно подключены к единичным выходамсвязалиного с даоной цепью лревмущеспва бло 25 ка приема, а таиже к ооотвепствупощей пруяпеинформациоцных входов блока управления ипервой пруйпе внформационяых входОв блокаподключения 1 раавределигеля, пр.и этом цепипреимущеспва первой коорданаты соедвненыЗ 0 со второй лрувпой анформационных входовблока псдключения, а,выходы цепя преимущества впорой координаты па 1 ралдельяо подкл,ючаны,к третьей прунпе щнформационных входов блока подключения и к третьей пруппе инз 5- формационных входов блока управления, запрещающий выход которого соединен,с запрещающим,входом блокам подключения 1 распределителя, а каакдый иа двух разрешающих выходов блока управления соединен с,разреша 1 ющим входом соопветствующей цепи прсвмущества, лричем каждый из двух установочвыхи управляющих выходов соединены с установочньвии и управляющими входами соответствующего блока приема; уяравля 1 оаие выходы45 блока уаравления,подключены к блоку подключения распределителя, куда также подсое.динены разрешающие выходы,блошка уцравлен,ия,2. Распределитель вызовов 1 по п. 1, отличаю 50 щийся тем, что блсйс управления содержит двапороговых каскада, две пары выходных схемсовпадения и узел формярования выходныхсигналов, соединенные между собой таким образом, что входы обоих пороговых каскадов55 образуют лервую и вторую грущпы информационных входов блока управления,:прямой и инвераный выходы каждого ив пороговых каскадов связанны с первым входом соответствующейвыходной схемы совпадения, вторые входы60 каоидой пары выходных схем ссвпаденая запараллелены;и являются первым и вторыыупоравляемыми входами блока управления, выходы этиках лар образуют птервые и вторые,управляющие выходы блока управления; нуле 65 вой,выход второго порогового каскада через428576 Ьида выходиую схему,совпадения, связанную с разрешающим выходом, соединен е первым входом узла формирования выходных оипналов, первый выход когорото является третьим управляющим выходом блока управления, вгорой выход являегвя вгорьгм установочным выходом блока управлвния, а также подключен к запрещающему входу схемы совладения, другой вход которой связа 1 н с первьпм управляющим,входом;блока у 1 правления, а выход схемы совпадения является запрещающии выходом блока управления и подключен к информ ационному входу,схемы совладения, выход которой являегся первым установочным выходом блока управления, а запрещатощий вход когорой через схему совпадения овязан с ииверсным выходом первого пороговапо каскада, и с прямым выходом вгорого пороповопо каскада, при этом второй вход узла формироваяия выходных оипналов ооедивен с выходом схемы соби ациявходы которой являются претьей группой ииформационных входов блока управлен ия.3. Раопределитель вызовов по и, 1, отличаю.и 1 ийся тем, что, цепи преимущесгва первой и второй коордипап выполнены в виде последовательного соединения п; (г=1,2; п=1,2, ) пар,двухвходовых схем совпадения (из:выход;ной и управляющей схем совпадений), имеющих общий вход, свяванный с выходом;преды. дущей,управляющей,схемы совпадаяия, при этом управляемый вход нервай по порядиу пары схем совпадений являепся управлясмым входом,цепи лреимущества, друпие входы всех и выходных схем совпадений являются еди ни вными входами цепи преимущества, а другие входы всех и - 1 управляющих схем совпадений являнлся нулевыми входами цепи преимущества, а выходы всех выходных схем совпадений образуют выходы цепи преимуще спва.4. Распределитель вызовов по п. 1, отличаюгчийся тем, лго каждый:из блоков приема информации состоит из п; (г=1,2; п=1,2, ) ,запоминающих ячеек и общей для всех ячеек 15 и входовой схемы совпадения, причем информацио)нные входы входных и уставовочные входы установочных двухвходовых схем совпадений всех и-запоминающих ячеек образуют соопвегственно ииформационные и установоч ные входы блока приема информации, единичные и нулевые выходы всех и-заломинающих ячеек образуют соответсввенно единичные и Булевые выходы блока приема информации, при этом ненулевые выходы парал лелыно заведены таяке на и-входовую схемусевпадения, выход которой параллелыно додсоедивен к инвертору и к другим входам Всех и-входных схем совпадений, а другие входы установочных схем ооападений эапараллелены З 0 и образуют управляемый вход блока приемаинформ ации.428576 г 4 итель Н, ГерасимоваТехред Т, Курилко едактор Т. Морозов ектор Н, А Заказ 502 Тира тета Совета нй и откры ская наб додписное Н Обл. тнп Костромского управления издательств, полиграфии и книжной торговли Иэд.1602 ПИ Государственного конг по делам изобрете Москва, Ж.35, Рауш

СмотретьЗаявка

1656789, 18.05.1971

иэаб рете, В. И. Городецкий, С. В. Голомолзина

МПК / Метки

МПК: H04Q 3/72

Метки: вызовов12, распределитель

Опубликовано: 15.05.1974

Код ссылки

<a href="https://patents.su/7-428576-raspredelitel-vyzovov12.html" target="_blank" rel="follow" title="База патентов СССР">Распределитель вызовов12</a>

Предыдущий патент: Устройство для переключения цветовых каналови цепей опознавания цвета декодирующегоустройства секам-пал

Следующий патент: Устройство для передачи команд по проводам

Случайный патент: Устройство для ультразвуковой контактной очистки длинномерных изделий