Устройство для формирования сигналов передачи данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

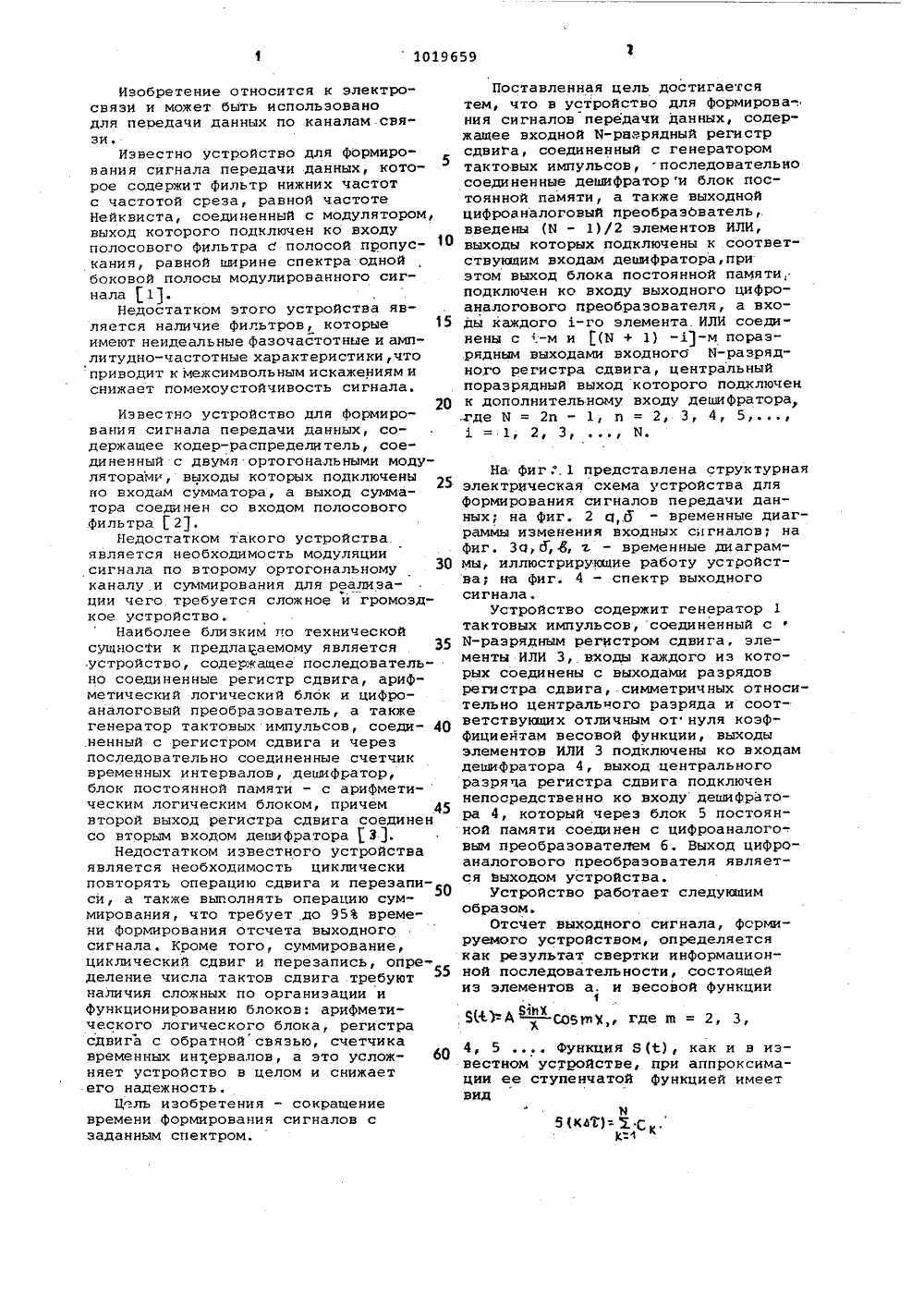

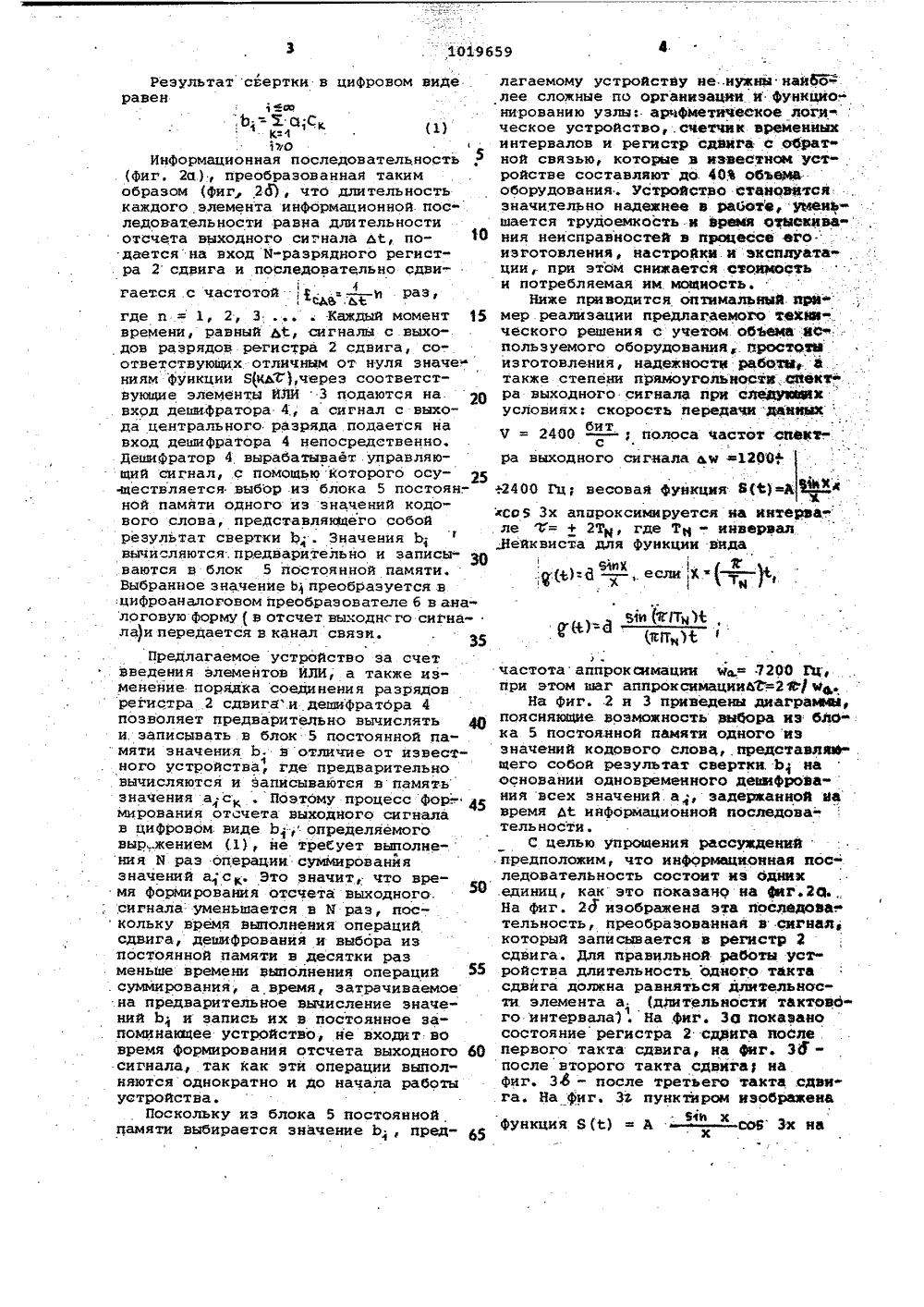

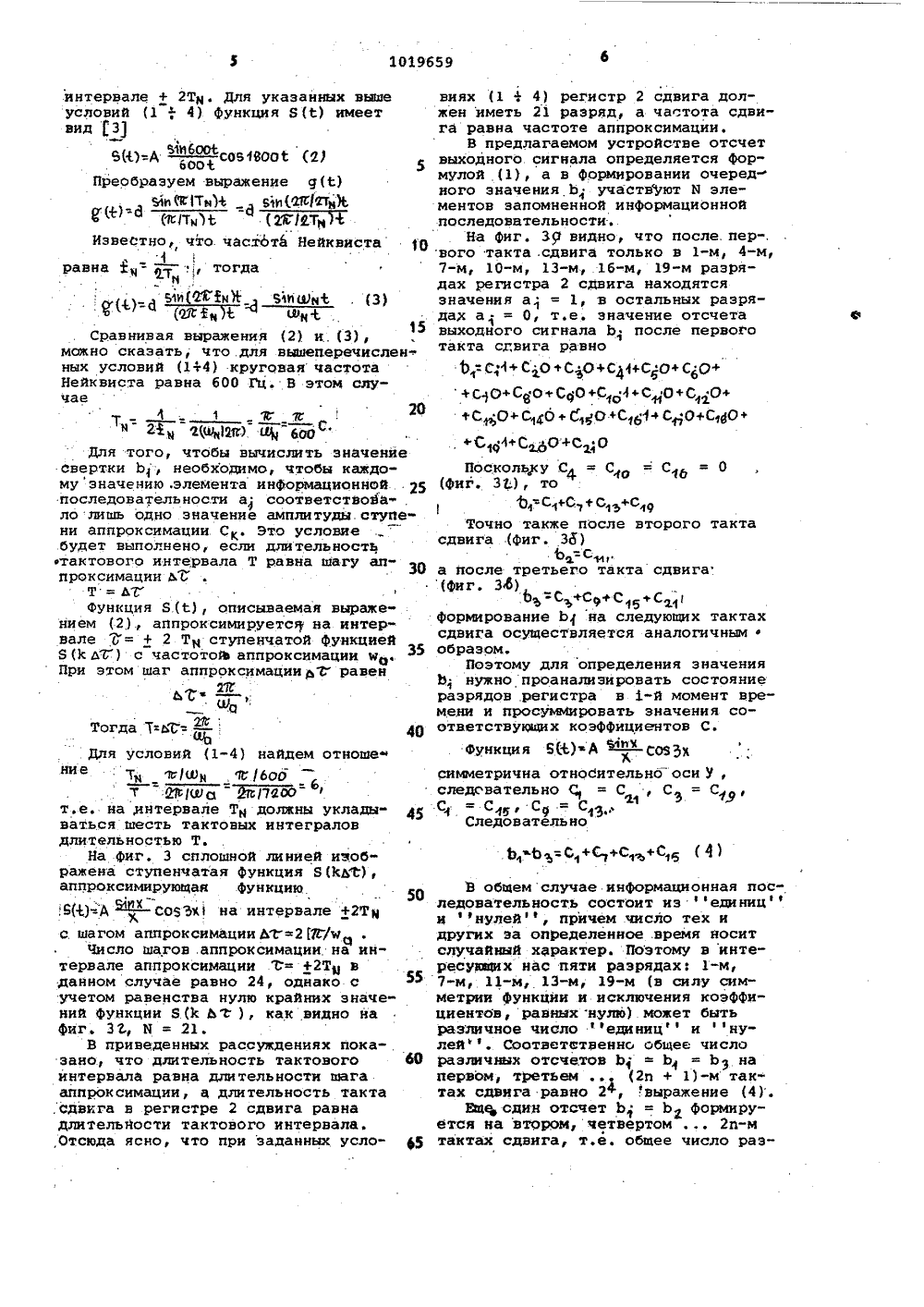

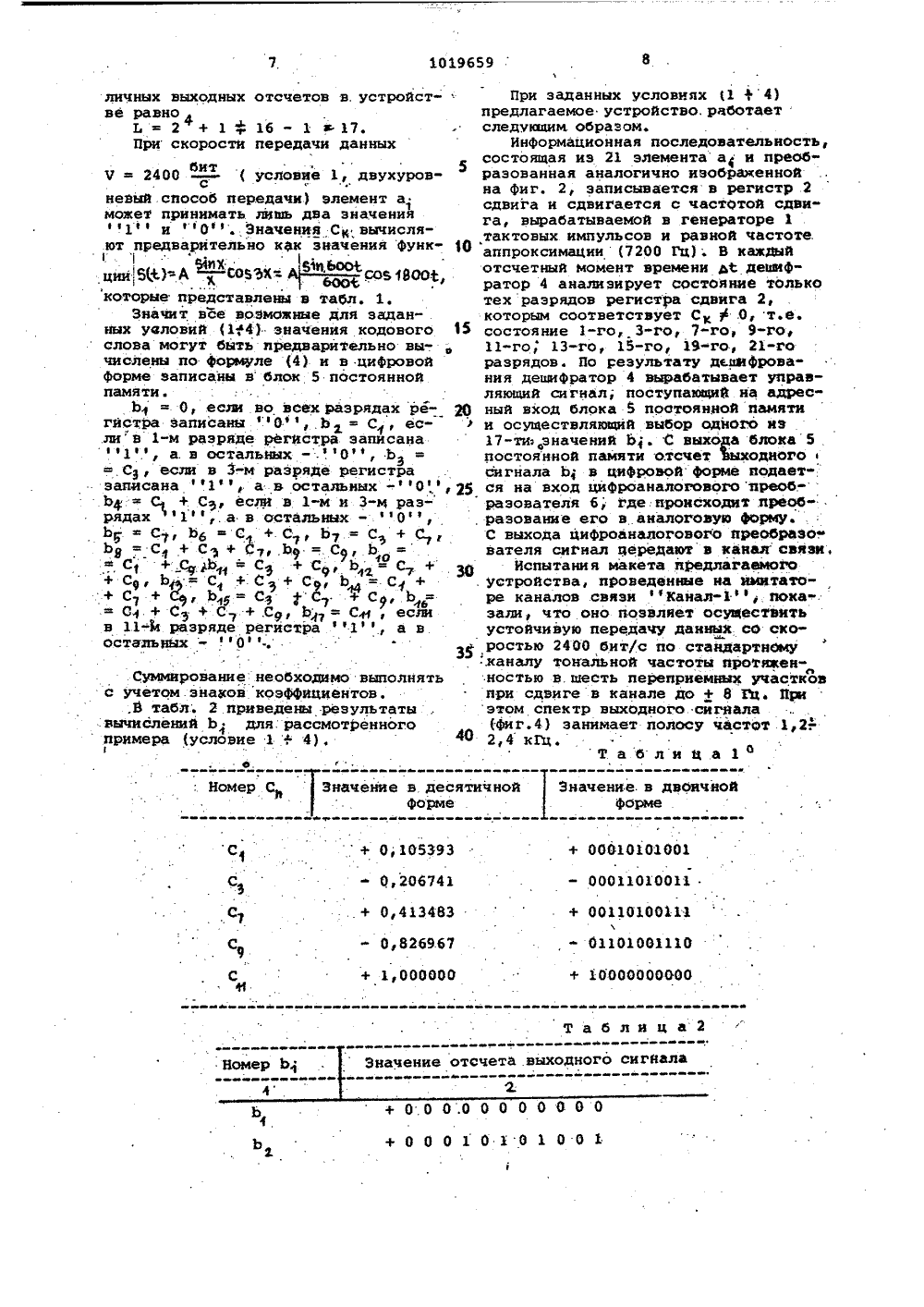

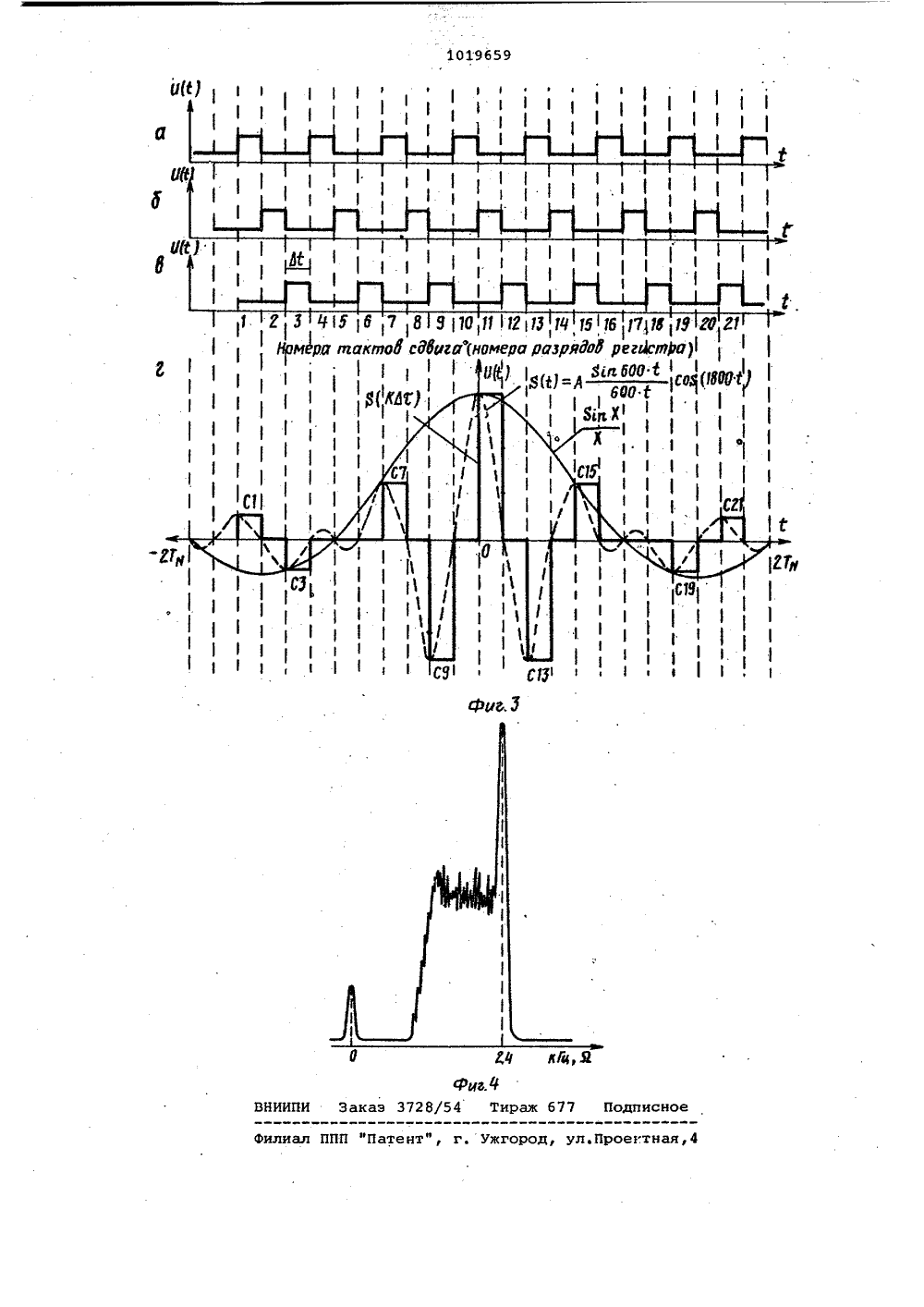

Изобретение относится к электросвязи и может быть использованодля передачи данных по каналам связи.Известно устройство для формирования сигнала передачи данных, которое содержит фильтр нижних частотс частотой среза, равной частотеНейквиста, соединенный с модулятором,выход которого подключен ко входуполосового фильтра с полосой пропускания, равной ширине спектра однойбоковой полосы модулированного сигнала ( 1),Недостатком этого устройства является наличие фильтров, которые 15имеют неидеальные фазочастотные и амплитудно-частотные характеристики,чтоприводит к межсимвольным искажениям иснижает помехоустойчивость сигнала.20Известно устройство для формирования сигнала передачи данных, содержащее кодер-распределитель, сое" диненный с двумя ортогональными модуляторами, выходы которых подключены но входам сумматора, а выход сумматора соединен со входом полосового фильтра ( 2(.Недостатком такого устройства является необходимость модуляции сигнала по второму ортогональному каналу и суммирования для реализацИи чего требуется сложноЕ и громоздкое устройство.Наиболее близким по технической сущности к предлааемому является З 5 устройство, содержащее последонательно соединенные регистр сдвига, ариф" метический логический блок и цифроаналоговый преобразователь, а также генератор тактовых импульсов, соеди ненный с регистром сдвига и через последовательно соединенные счетчик временных интервалов, дешифратор, блок постоянной памяти - с арифметическим логическим блоком, причем 45 второй выход регистра сдвига соединен со вторым входом дешифратора ) 3 ).Недостатком известного устройства является необходимость циклически повторять операцию сдвига и перезаписи, а также выголнять операцию суммирования, что требует до 95 времени формирования отсчета выходного сигнала. Кроме того, суммиронание, циклический сдвиг и перезапись, определение числа тактов сдвига требуют наличия сложных по организации и функционированию блоков: арифметического логического блока, регистра сдвига с обратной связью, счетчика временных интервалов, а зто услож няет устройство в целом и снижает -его надежность.Цль изобретения - сокращение времени Формирования сигналов с заданным спектром. Поставленная цель достигается тем, что в устройство для Формирова". ния сигналов передачи данных, содержащее входной Б-разрядный регистр сдвиГа, соединенный с генератором тактовых импульсов, последовательно соединенные дешифратор и блок постоянной памяти, а также выходной цифроаналоговый преобраэбватель,.введены (Б - 1)/2 элементов ИЛИ, выходы которых подключены к соответствующим нходам дешифратора,при этом выход блока постоянной памяти подключен ко входу выходного цифроаналогового преобразователя, а входы каждого 1-го элемента. ИЛИ соеди" нены с .-м и Б + 1) -Ц-м поразрядным выходами входного Б-разрядного регистра сдвига, центральный поразрядный выход которого подключен к дополнительному входу дешифратора де Н = 2 П - 1, и = 2, 3, 4, 51, 2, 3, , Н.На Фиг:,1 представлена структурнаяэлектрическая схема устройства дляФормирования сигналов передачи данных; на Фиг. 2 с(о - временные диаграммы изменения входных сигналов; нафиг. 3 цК, 8, ъ - временные ди аграммы, иллюстрирующие работу устройства; на фиг. 4 - спектр выходногосигнала.Устройство содержит генератор 1тактовых импульсов, соединенный с фБ-разрядным регистром сднига, элементы ИЛИ 3, входы каждого из которых соединены с выходами разрядоврегистра сдвига, симметричных относительно центрального разряда и соответствукюцих отличным от нуля коэфФициейтам весовой Функции, выходыэлементов ИЛИ 3 подключены ко входамдешифратора 4, выход центральногоразряча регистра сдвига подключеннепосредственно ко входудешифратора 4, который через блок 5 постоянной памяти соединен с цифроаналоговым преобразователем б. Выход цифроаналогового преобразователя является выходом устройства,Устройство работает следующимобразом.Отсчет выходного сигнала, формируемого устройством, определяетсякак результат свертки информационной последовательности, состоящейиз элементов а, и весовой функциит8 Ю=А СО 5 яМ где в = 2, 3,4, 5функция 8, как и в известном устройстве, при аппроксимации ее ступенчатой функцией имеет видй5(")= СК(фиг. 2 а), преобразованная таким образом (Фиг 29, что длительность каждого элемента информационной.пос" ледовательности равна длительности отсчета выходного сигнала АТ, по" 0 даетсяиа вход И-разрядного регистра 2 сдвига и последовательно сдвигается с частотой , = " и раз, где и = 1, 2, 3. Каждый момент 5 времени, равный Ь 1, сигналы с выходов разрядов регистра 2 сдвига, со-. ответствующих отличным от нуля значе:" ниям Функции ЯкаТ),через соответствующие элементы ИЛЙ 3 подаются на вход дешифратора 4, а сигнал с выхода центрального разряда подается на вход дешнфратора 4 непосредственно. Дешифратор 4 вырабатываетуправляющий сигнал, с помощью которого осуществляется выбор .из блока 5 постоян". ной памяти одного из значений кодового слова, представлякшего собой результат свертки Ь. Эначення Ь; вычисляются,предварйтельно и записы- ЗО ваются в блок 5 постоянной памяти, Выбранное значение Ь 1 преобразуется в :циФроаналоговом Преобразователе 6 в аналоговую форму ( в отсчет выходн 4-го сигнала)и передается в канал связи.Предлагаемое устройство за счет введения элементов ИЛИ, а также изменейие порядка соединения разрядов регистра 2 сдвига.и дешифратбра 4 позволяет предварительно вычислять 4 О и. записывать.в блок 5 постоянной памяти значения Ь. и отличие от известного устройства, где предварительно вычисляются и записываютея в памятьзначения а ск . Поэтому процесс Фор мирования отсчета выходного сигнала в цифровом виде Ь:, определяемого выржением (1), не требует выполнения И раз операции. суммированйязначений аск. Это значит; что время Формирования отсчета выходного. ;сигнала: уменьшается в И раз, поскольку время выполнения операцийсдвига, дешифрования и выбора из постоянной памяти в десятки раз меньше времени выполнения операций э 5 . суммирования, а время, затрачиваемое на предварительное вычисление значений Ь и запись их в постоянное запоминакщее устройство, ие входит во время Формирования отсчета выходного 60 сигнала, так как этй операции выпол" няются однократно и до начала работыустройства.Поскольку из блока 5 постояннойпамяти выбирается значение Ь, пред- Я лагаемому устройству ненужны наиюлее сложные по органиэации и Функцио.- нированию узлы: арифметическое логи"ческое устройство,.счавтчик временных интервалов и регистр сдвига с обрат ной связью, которые в известном устройстве составляют до. 40 объейа: оборудования. устройство стаиоются значительно надежнее в работе, 3 ФЮИЬ- шается трудоемкость и время отМакйва ния неисправностей в процессе его изготовления, настройки и эксплуатации, при этом снижается стоимость и потребляемая им.мощность.Ниже приводится оптимальщай Щэ мер реализации предлагаемого твои", ческого решения с учетом обьещ ВС": пользуемого оборудования,. рростотвизготовления, надежиосте Работмф. 3 также степени рямоугольности.сйект. ра выходного сигнала при сйейузаэФх условиях: скорость передачи "м 4 япиюс . Ч = 2400 - ; полоса частот спект.".битсра выходного сигнала дм бб 1209 ба 2400 гц весовая фуякякя б(и)АЯбсср Зх алцроксимируется иа интерва-.ле = + 2 ТИ, где Тбб - инверзаляеяйквиста для функции вида,944:0 я ЕСв ,б и( т) 4частота аппроксимации ма= 7200 Гц,при этом шаг аппроксимацииЮ.=2 Ф) ю.На фиг. 2 и 3 приведены диаграммы, поясняющие воэможность выбора из: блока 5 постоянной памяти одного иэ значений кодового слова,.представлаЭщего собой результат свертки. Ь иаосновании одновременного дешифроаа" иия всех значений а , задержанной Мавремя А информациойной последова".тельности. С целью. упрощения рассуждений предположим, что информационная цос ледовательность состоит нэ одник единиц, как это показано на 4 нг.20. На фиг. 2 д изображена эта последойа. тельность, преобразованная в сигналб который записывается в регистр 2 сдвига. Для правильной работы устройства длительность одного такта сдвига должна равняться длительности элемента а. (длительности тактово" го интервала) .На .Фиг. ЗО покааано состояние регистра 2 сдвига после первого такта сдвига, иа Фиг. ЗЮ- после второго такта сдвига иа фиг. 38 - после третъего такта .сдвига. На фиг. Зъ пунктиром изображена фуяяияя б(в А соб эх яеъе хх+ 10000000000 Таблица 2 личных выходных отсчетов в. устройст-Прн заданных условиях (1 Ф 4) ве Равно 4предлагаемое устройство. Работает Ь : 2 + 1 ф 16 - 1 з 17. . следящим.образом. При скорости передачи данных информационная последовательность, бит5состоящая из 21 элемента а 4 и преоб- Ч = 2400 с. ( Условие 1, двухуров- раэованная аналогично иэобракеннойна Фнг. 2, записывается в регистр 2 невый способ передачи) элемент асдвига и сдвигается с частОтой сдвиможет принимать лишь два значения га, вырабатываемой в генераторе 1г1 и 0 . Значения С вычисля- тактовых импульсов и равной частоте. ют предварительно как значения ФУнк аппроксимации (7200 Гц). В кажЭййфииХ. он,ЬОМ отсчетный момент вРемени дВ де 34 Ф 60 от ф ратор 4 анализирует состояние только которые представлены в табл, 1, тех разрядов регистра сдвига 2,Значит все возможные для задан- которым соответствует С Ф 0 т.е. ных увловий (1 ф 4)- значения кодового 5 состояние 1 тго, Зтго, 7 тго, 9-го слова могут быть предварительно вы-.11 тго, 13 тго, 15 тго, 19-го, 21 тго чиолены по Формуле (4) н в цифровой разрядов. По результату дыИфрова" Форме записаны в блок 5 псстоянной ния дешифратор 4 вырабатывает управ- памяти. ляющнй сигнал; поступающий на адрес"Ь 4 = О, если во всех разрядах ре О ный вход блока 5 постоянной памяти гистра записаны "О,.Ь = С, , ест"и осуществляющий выбор одного из .лне в 1 тм разряде регистра эапйсана 17-тнзначений Ь. С выхода блока 5 1 фф, а. в остальных -. фО, Ь постоянной памятй отсчет выходного= С 1, если в 3-.м раэряде регистра . с)гнала Ь; в цифровойФорме подает- записана .1 ф, а в остальных -О,ф, 25 ся на вход цифроаналогового преобт Ь 4. С) + С 9, если в 1 тм и Зтм раэ- разователя 6; где:происходит пРеобт рядах 1 ,;а в остальных - ффО, . Резование его в аналоговую Форму Ь С 7, Ь 6 С + С, Ь 7 . С + С , С выхода цифроаналогового преобразо". Ь 8 .в . Сз .+ СЪ + 7 Ь 9 =. С, Ь = . вателя сигнал цередают в канал связи, = с + с.гь 1С 9 + с), ь = с + Зо испытаниЯ макета нреДлагаемого + С 9Ь.= С 1 + С+ С, Ь = С + . устройства, проведенные иа имитатот .+ С 7 + С ф Ьу = СЗ С 7 + Су, Ь = ре каналов связи фЕаналф; покат. = с. + С 5 + с. + .с 9, Ь. = с.м, если залн, что оно аозвляет осуществить в 11-Й разряде регистра фф 1 ф, а в устойчивую передачу данный со скоостальних - фОф-. . Ростью 2400 бит/с по стандартному Зэ::.каналу токальной частоты протяаенвиСуммирование необходимо выполнять ностью в.шесть переприемных Участков с учетом знаков коэффициентов, прн сдвиге в канале до + 8 Гц. При,В табл. 2.приведены результатыэтом спектр выходного сйгйала :вычислений Ь для: рассмотренного (Фиг.4) занимает полосу частот 1,2", примера (условие 1 + 4). 4 О 2,4 к 1 ц,Т.абли Ца 1Ф.тттатевю тааюеию тав виттаююивтюи и виюеиюттт иттвит еюююю и. Номер С, Значение в. десятичной Значение. в двоичнойФорме Формев ттттивттФаютаааюааиетювюттавюавт юа юю ттюее юавевтютттттюаеиа и+100000 вардан Т, рабион ЬЬ лнисниньносснв оньноЬо 5 осо1019659 иИ)1011, гд,тЧ тз а рзеВ Яг тара тактаа срааганамера разряраР регьстра)ю О К 4 р 2Физ. Ю НИИПИ Заказ 3728/54 Тираж 677 Подписноелиал ППП ггПатент"е г. Ужгород, ул.Проектная,4

СмотретьЗаявка

2919632, 05.05.1980

СТРУКТУРНО-КОНСТРУКТОРСКОЕ БЮРО ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ СО АН СССР

ФЕСЕНКО БОРИС ВЛАДИМИРОВИЧ, ЧЕРНАВИН АНАТОЛИЙ ДМИТРИЕВИЧ

МПК / Метки

МПК: H04L 25/40

Метки: данных, передачи, сигналов, формирования

Опубликовано: 23.05.1983

Код ссылки

<a href="https://patents.su/7-1019659-ustrojjstvo-dlya-formirovaniya-signalov-peredachi-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования сигналов передачи данных</a>

Предыдущий патент: Выходное телеграфное устройство

Следующий патент: Система передачи и приема двоичных сигналов с частотной модуляцией

Случайный патент: Радиолокационный дальномер