Устройство управления преобразователем аналог-код последовательного приближения

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

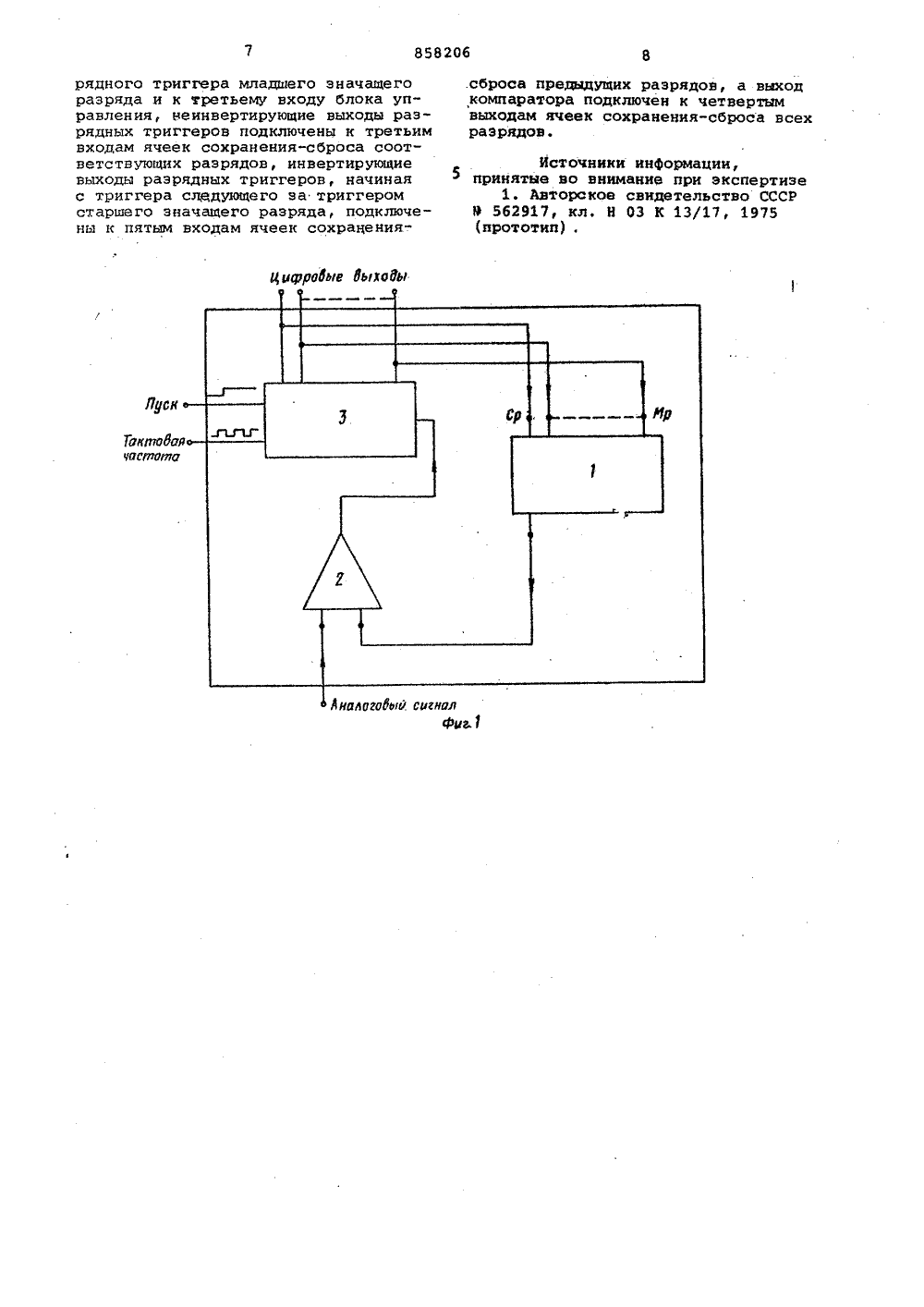

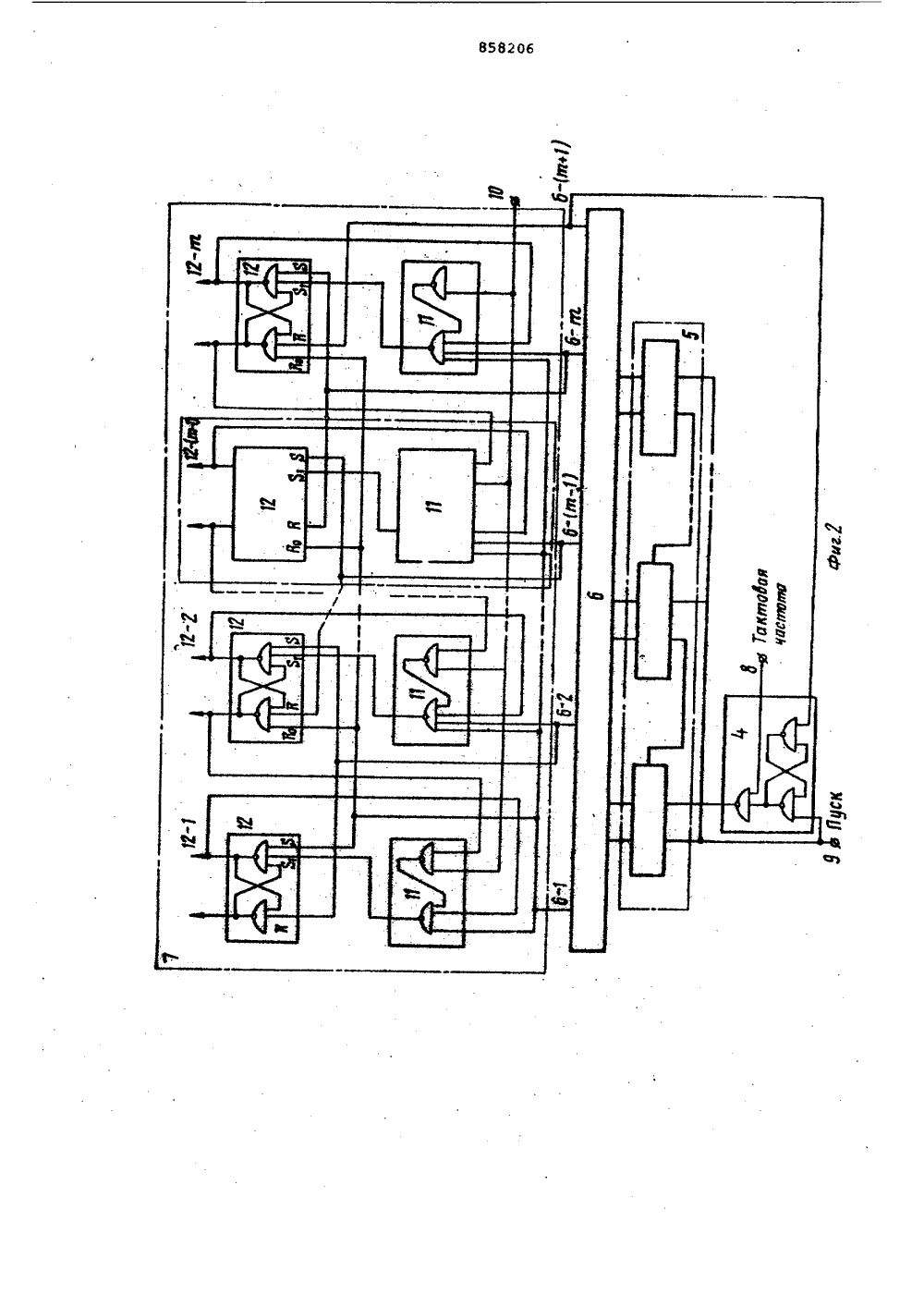

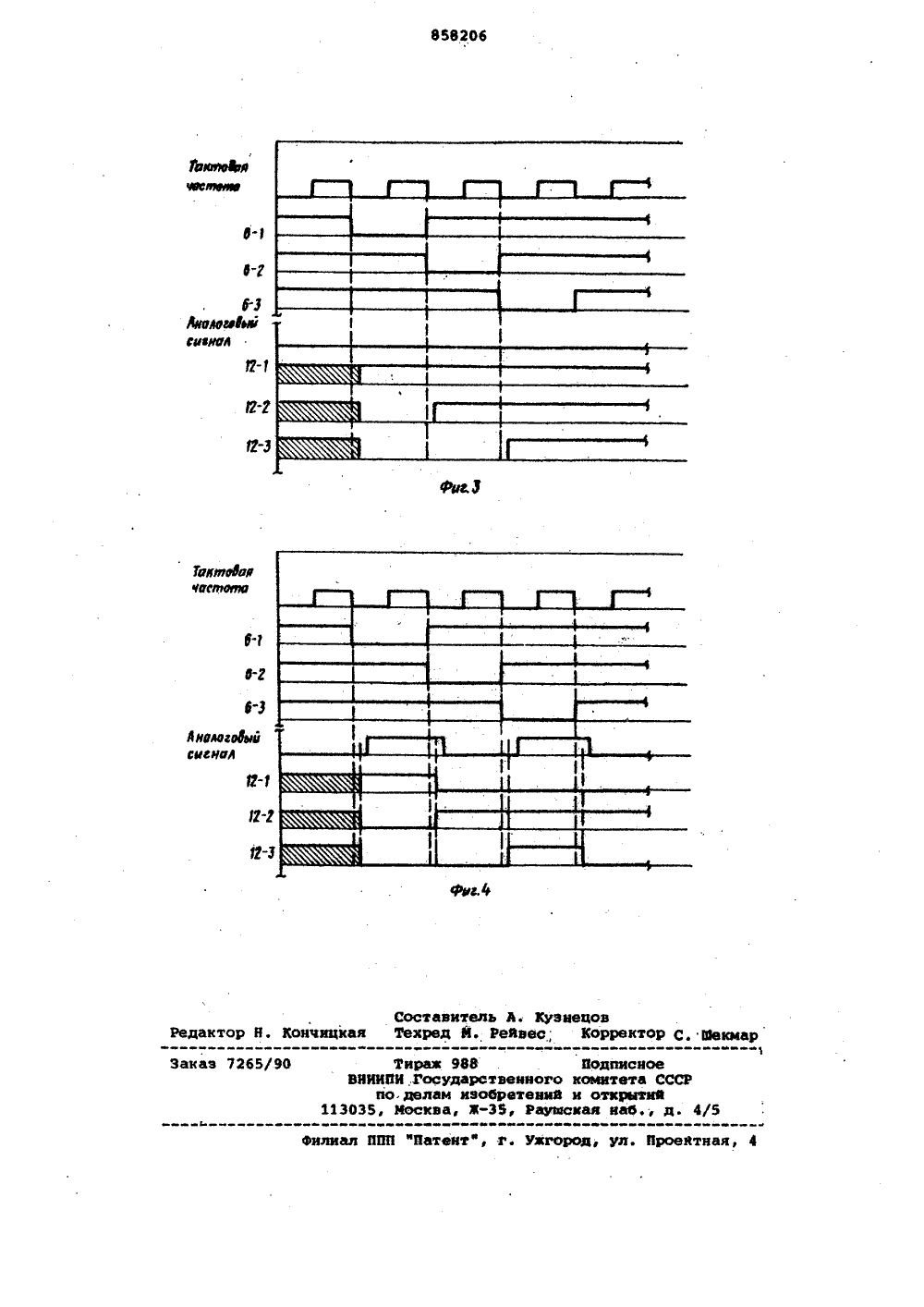

Союз Советских Социалистических Республик(51)М К 3 Н 03 К 13/00 Государственный комитет СССР по делам изобретений н открытий54) УСТРОЙСТВО УПРАВЛЕНИЯ ПРЕОБРАЗОВАТЕЛЕ АНАЛОГ-КОД ПОСЛЕДОВАТЕЛЬНОГО ПРИБЛИЖЕНИЯ е,е автомати ой техни в частно говых си Изобретение относится к к телемеханике и вычислительн к и может быть использовано, сти в преобразователях анало гналов в цифровой код.Известно устройство управления преобразователем, сбдержащее триггер запуска, Формирователь задержанных им пульсов, элементы И,. И-НЕ, схему стробирования выходного сигнала элемента сравнения, регистр, каждый разряд которого содержит управляющий элемент И-НЕ и два триггера, состоящие из одного элемента И-ИЛИ-НЕ с входами триггерной связи и установки, элемента И-НЕ для первого триггера и элемента НЕ для второго триггера, шину тактирующих импульсов и шину начальной установки 1).Недостатком данной схемы является низкая надежность и малое быстродействие преобразования.Цель изобретения - повышение надежности и увеличение быстродействия при сохранении точности преобразовается тем, правлекод последержащее 3 ния.Поставленная цель дости что в известном устройстве ния преобразователем анало довательного приближения,блок управления, выполненный на уйравляющем элементе И-НЕ и триггере наэлементах И-НЕ, выход которого соединен с первыми входами счетчика, выполненного на делителях частоты, выходы которого соединены со входом дешифратора, блок позирования из в-ячеек сохранения-сброса, каждая из которых выполнена на двух элементах И-НЕ,и а-разрядных триггеров, выполненныхна двух элементах И-НЕ для каждогоразряда, при этом дополнительный устанавливающий вход каждого из них соединен с выходом соответствующей ячейки сохранения"сброса, шину фПускф,соединенную с первым входом блока управления и вторыми входами счетчика,шину "Тактовая частота", соединеннуюсо вторым входом блока управления,первый выход дешифратора подключен кустанавливающему входу разрядноготриггера старшего значению разряда ик дополнительным сбрасывающим входамразрядных триггеров последующих разрядов до младшего значения разрядавключительно, а также и первым входамячеек сохранения-сброса всех разрядов,каждый иэ последующих а-выходов дешифратора подключены к сбрасывающемувходу разрядного триггера предыдуще 858206го значащего разряда, и к устананливающему входу разрядного триггераданного разряда, а также ко второмувходу ячейки сохранения-сброса данного значащего разряда, последний выход дешифратора подключен к сбрасынающему входу разрядного триггера младшего значащего разряда и к третьемувходу блока управления, неинвертирующие выходы разрядных триггеров подключены к третьим входам ячеек сохранения-сброса соответствующих разрярядов, инвертирующие выходы разрядныхтриггеровначиная с триггера следующего эа триггером старшего значащегоразряда подключены к пятым входамячеек сохранения-сброса предыдущих 15разрядов, а выход компаратора подключен к четвертым выхоцам ячеек сохранения-сброса нсех разрядов,На Фиг, 1 представлена блок-схемааналого-цифрового преобразователя 2 О,АЦП) последовательного приближения;на Фиг. 2 - устройство управлениящ-разрядного АЦП последовательногоприближения; на фиг, 3 - временнаядиаграмма к примеру 1; на Фиг. 4временная диаграмма к примеру 2,Схема приводимого аналого-цифрового преобразователя (АЦП) поразрядноговзвешивания включает в себя цифроаналоговый преобразователь 1 (ЦАП), компаратор 2 и устройство управления 3(Фиг, 1)Структурная схема устройства управлениясодержйт блок 4 управления, счетчик 5,дешифратор б с выходами бб (пл.+3 ), блок 7 кодирования, шину 8 тактовой Зчастоты, шину 9 "Пуск", шину 10 компаратора,Шина 9 "Пуск" соединена с первымвходом блока 4 управления и вторымвходом счетчика 5, выходы которых соединены со входами дешифратора б, шина 8 тактовой частоты соединена совторым входом блока 4 управления, выход которого соединен с первыми входами счетчика 5. 45Блок управления состоит из управляющего элемента И-НЕ и триггера, построенного на элементах И-НЕ, выходкоторого связан со входом управляющего элемента И-НЕСчетчик 5 состоитиз делителей на два, так что выходпредыдущего связан со входом последующего.Блок 7 кодирования состоит иэя-ячеек 11 сохранения-сброса, построенных на двух элементах И-НЕ,и и-разряд ных триггеров 12, построенных на двухэлементах И-НЕ.Первый выход 6-1 дешифратора подключен к устанавливающему входу 5-разрядного триггера старшего значащегоразряда и к допОлнительным сбрасывающим входам В"разрядных триггеров 12последующих разрядов до младшего значащего разряда включительно, а такке к первым входам ячеек сохранения- у сброса всех разрядов, второй выход 6-2 дешифратора подключен к сбрасывающему входу В-разрядного триггера 12 старшего значащего разряда и к устанавливающему входу 5-разрядного триггера 12, следующего за старшим значащим разрядом, а также ко второму входу ячейки сохранения-сброса следующей за ячейкой старшего значащего разряда, аналогичным образом соединенные последующие выходы дешифратора 6-3-6- -(и+1) с разрядными триггерами и ячейка сохранения в сбро блока 7 кодирования,при этом последний выход б- (и+1) дешифратора соединен с третьим входом блока 4 уПравления, выходы ячеек сохранения"сброса соединены с дополнительными устанавливающими входами 5 -разрядных триггеров тех же разрядов, неинвертирующие выходы разрядныхтриггеров 12-1 Р-в подключены к третьим входам ячеек сохранения-сброса соответствующих разрядов, инверти-. рующие выходы 12-212-п-разрядныхтриггеров 12, начиная с триггера, следующего эа триггером старшего значащего разряда, подключены к пятым входам ячеек сохранения-сброса предыдущих разрядов, а шина компаратора подключена к четвертым входам ячеек сохранения-сброса всех разрядов,Преобразователь аналог-код и устройство управления работают следующимобразом.При подаче сигналов "Пуск" и "Тактовая частота" на блок 4 управления, а также сигнала "Пуск". на первый вход счетчика 5 на выходах дешифратора б (Фиг. 2) последовательно набираются комбинации (011), (1011), (11011), (1110) (Фиг. 3 и 4)При соответствующем аналоговом напряжении на входе АЦП на выходах 12-1-12-а АЦП (фиг. 2) набирается цифровая комбинация 111 при этомкомпаратор в течение цикла преобразования находится н состоянии логического нуля (Фиг. 3, линия К), что является признаком сохранения раэрядон во включенном состоянии.Комбинация (011) на выходах дешифратора 6 вызывает,комбинацию (110) на входах й., 5, 5-разрядного триггера старшего разряда, что приводит к единичному логическомууровню на выходе 12-1, т. е. к включению старшего значащего разряда (СР)ЦАП; при этом на нходах Ко,й, 55 разрядных триггеров младаего разрядавозникает цифровая комбинация 0111,что приводит к нулевому логическомууровню на выходах 12-2-12-п, т. е. квыключению остальных разрядов ЦАП(фиг. 2, 3 и 4),Последующая комбинация 1011 навыходах дешифратора вызывает комбинацию 001 на входах В, 5, 5-разрядноготриггера старшего разряда, что сохраняет предыдущее состояние логической858206 Формула изобретения 45При возникновений последующей .дешифрирующей комбинации 1011 на выходах дешифратора логический уровень "О" с выхода 6-2 подается на В-вход разрядного триггера старшего разряда, 0 а на 5-вход подается логическая "1" с выхода 6-1 (Фиг. 2, 4) . В связи с логической задержкой распространения цифровых сигналов, логический уровень "1" некоторое время сохраняется на 5 -входе разрядного триггера старше 4го разряда (Фиг. 2) . Таким образом, на В 5 5-входах разрядного триггера с.аршего разряда Набирается комбина,ция (011), переустананливающая выход 12-1 в состояние логического "0" 0 (что соответствует выключению старшего разряда ЦАП) . Значение логического уровня сигнала комларатора в дальнейшем не оказывает,.влияния на состояние разрядного триггера старшего45 разряда, так как логический "0", сни",маемый с выхода 12-1 удерживает вход5 в состоянии логической "1 ф. Навйходах 12-2-12-в-разрядных триггеровостальных разрядов возникает комбинация 100 (фиг. 2 и 4),Аналогичным образом происходитвключение последующих разрядов, атакже их: выключение в зависимости отсоотношения между величинами аналоговых сигналов на входе АЦП и выходе1 АПРассмотренные принципы построенияустройства управления позволяют наК-блоках делителей частоты реализовать е ц = 2 К-разрядный АЦП. Приэтом полный цикл работы АЦП составля-.ет 2 К периодов тактовой частоты(фиг, 1 и 2) .Предлагаемый преобразователь можетнайти широкое применение в электромузыкальных инструментах. Устройство управления преобразователем аналог-код последовательного приближения, содержащее блок управления, выполненный на управляющем элементе И-НЕ и триггере на элементах И-НЕ, выход .которого соединен с первыми входами счетчика, выполненного на делителях частоты, выходы котэрого . соединены со входом дешифратора, блок кодирования из е-ячеек сохранения- сброса, каждая из которых выполнена на двух элементах И-НЕ, и в-разрядных триггеров, выполненных на двух элемента И-НЕ для каждого разряда, при этом дополнительный устанавливающий вход каждого иэ них соединен с выходом соответствующей ячейки сохранения-сброса, шину "Пуск", соединенную с первым входом блока управления и вторыми входами счетчика, шину "Тактовая частбта", соединенную со вторым входом блока управления, о т л и - ч а ю щ е е с я тем, что, с целью повышения надежности и увеличения быстродействия при сохранении точности преобразования, первый выход дешифратора подключен к устанавливающему входу разрядного триггера старшего значащего разряда и к дополнительным сбрасывающим входам разрядных триггеров последующих разрядов до младшего значащего разряда включительно, а также к первым входам ячеек сохранения-сброса всех разрядов, каждый из последующих а-выходов дешифратора подключенык сбрасывающему входу разрядного триггера предыдущего значащего разряда и к устанавливавзцему входу раэрщного триггера данного разряда, а также ко второму входу ячейки сохранения-сброса данного значащего разряда, последний выход дешифратора подключен к сбрасывающему входу раз858206 циррв 3 ие Зыюоды рядного триггера младшего значащегоразряда и к третьему входу блока управления, неинвертирующие выходы разрядных триггеров подключены к третьимвходам ячеек сохранения-сброса соответствующих разрядов, инвертирующиевыходы разрядных триггеров, начинаяс триггера следующего за триггеромстаршего значащего разряда, подключены к пятым входам ячеек сохранения".сброса предыдущих разрядов, а выходкомиаратора подключен к четвертымвыходам ячеек сохранения-сброса всехразрядов. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР9 562917, кл. Н 03 К 13/17, 1975858206 а-г ВютаЬю чвтротю фюгюйв юани акт Заказ 7265/90 Иате Филиал 63Мемемйесивил Составитель А. Кузыецовончицкая техред и. Рейвес; корректор с. юекмар Тираж 988НИИИИ .Государе по, делам изо35, Москва, З Иодписноетвеыного комитета СССРбретеный и открмтий3, Раумска наб., д. 4/БВЕВВ ЮВАОг. ужгород, ул. Проейтна

СмотретьЗаявка

2788841, 03.07.1979

ПРЕДПРИЯТИЕ ПЯ Г-4322

ТАМОШЮНАС АЛЬФРЕДАС ВЛАДОВИЧ, СМИРНОВ ВАЛЕРИЙ ВИКТОРОВИЧ

МПК / Метки

МПК: H03K 13/00

Метки: «аналог-код», последовательного, преобразователем, приближения

Опубликовано: 23.08.1981

Код ссылки

<a href="https://patents.su/6-858206-ustrojjstvo-upravleniya-preobrazovatelem-analog-kod-posledovatelnogo-priblizheniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство управления преобразователем аналог-код последовательного приближения</a>

Предыдущий патент: Тиристорный регулятор переменного напряжения

Следующий патент: Реверсивный аналого-цифровой преобразователь

Случайный патент: Инсектицидно-акарицидное средство