Формирователь биполярных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1780156

Автор: Венедиктов

Текст

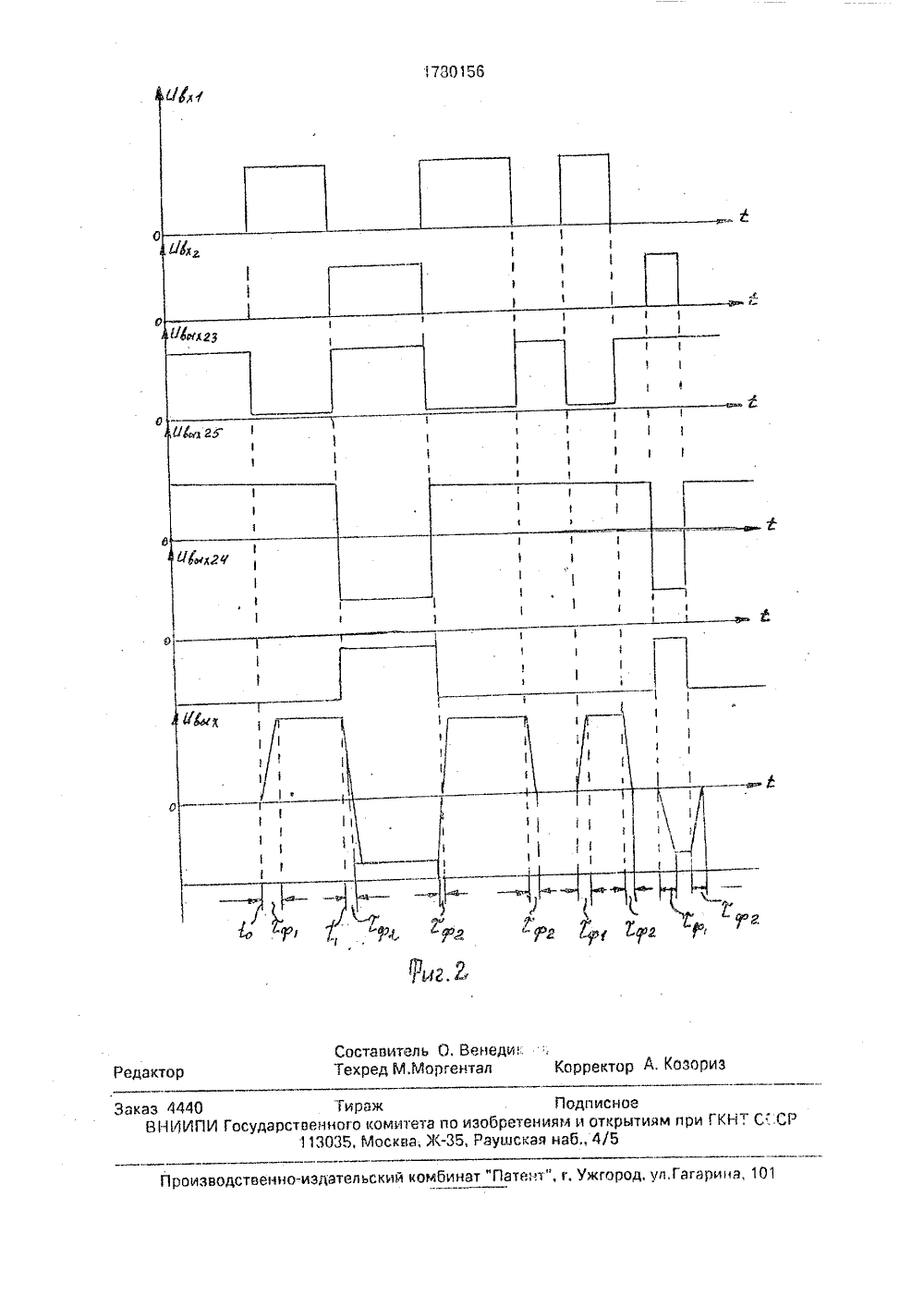

(39) 03 К 50 ф" ЕТЕНИ К АВ лектроприборотво СССР, 1977.тво СССР1, 1988,Ь БИПОЛЯРНЪ тся к импулъснои и и может быть ис льном последоваГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(ГОСПАТЕНТ СССР) ИСАНИЕ ИЗО КОМУ СВИДЕТЕЛЬСТВ(57) Изобретение относивычислительной техникепользовано в магистра 1780156 А 1 тельном интерфейсе с центральным управлением, применяемом в системе электронных модулей в качестве передающего устройства. Формирователь содержит два входа 1 и 2, выход 3, двухполярный источник 4 питания, два канала 13 и 14, каждый из которых содержит выходной транзистор 15, диод 18 и первый резистивный делитель 19, КЗ-триггер 9 с интегрирующей цепью 10, два дополнительных диода 11 и 12, два дополнительных транзистора 16 и 17,дополнительный резистивный делитель 20, два резистора 21 и 22, элемент 2 И-НЕ 23, двухполярный ключ 25 вс вторсм канале. 2 ил.25 30 Изобретение относится к импульсной и вычислительной технике и может быть использовано В магистральном последом- тельном интерфейсе с центральным управлением, применяемом в системе электронных модулей в качестве переда 1 още.о устройства.Известен формирователь биполярных импульсов, содержащий два канала, проводимость транзисторов ОднОГО из которых противоположна проводимости тоанзисторов другого канала, в состав каждого из каналов входят транзисторный кл 1 оч., источник питания Одной поля 12 ности, дВа диода и Выходной транзистор, а также выходную шину.Недостатком этого формигювателя является отсутствие защиты от перегрузки по току и низкое бь 1 стродействие. Наиболее близким по технической сущности является формирователь биполярных сигналов, содеркащий двухполярный источник питания, общий вывод которого соединен с общей шиной устройства, три диода, двенадцать резисторов, три ключа одного типа проводимости и один ключ другого типа проводимости, причем вход первого кл 1 оча соединен с первым ВхОдОм устрОЙства, первый и второй выходные каналы, пе 12- вые выводы первого и второго выходных каналов соединены с выходом устройства, вторые вь 1 ходы - с общей шиной устройсгвэ, третий вывод пер 12 ОГО ВыхоцнОГО канала соединен с положительным выводом двухполярного источниа питания, отрицатель.ный вывод которой соецинен с третьим выводом второго вь 1 ходного канала.Недостатки этого формирователя - отсутст 13 ие защиты От перегрузки пО току, низкое быстродействие и низкая амплитуда выходного сигнала за счст падения напряжения на эмиттерных переходах транзисторов 16 и 17, элемента И-НЕ 12, ключа 20, эмиттернОГО поВторителя 21 и выходнОГО транзистора 27.Цель изобретения - защита от перегрузки по току, повышение быстродейстг 2 ия и амплитуды выходноГО сигнала,На фиг, 1 представлена структурная электрическая схема формирователя; на фиг. 2 - временные Диаграммы, поясня О- . щие алгоритм работы устройства,Формирователь биполярных сигналов содержит два входа 1 и 2, выход 3, двухполяр 11 ый источник 4 питания с положительным и отрицательным полюсами 5 и б, общу 1 О шину 7, резистор 8, В 8-триггер 9: интегрирующей цепью 10 и двумя дог 1 ол 1 читеьными диодами 11 и 12, два канаа 13 и 14, ка 2 кдый из которых содержит выходной транзистор 15, первый и Второй дополнительные транзисторы 16 и 17, диод 18, первый и дополнительный резистивные делители 19 и 20, первый и второй резисторы 21 и 22, при этом первый канал 13 дополнительно содержит элемент 2 И-НЕ 23, а в орой канал 14 - ключ 24 и двухполярный ключ 25.Первым входом 1 формирователя является первый вход элемента 2 И-НЕ 23, второй вход которого объединен с прямым Выходом О ВЯ-триггера 9, содержащего интегрирующую Яс-цепь 10, точка соединения резистора и конденсатора которой подкл 1 очена к 8-Входу этого. триггера 9. Выход элемента 2 И - НЕ 23 соединен с вторыми выводами первого и дополнительного резистивнь 1 х делителей 19 и 20 первого канала 13, база выходного транзистора 15 которого подключена к точке соединения резисторов первого резистивного делителя 19, при этом первые выводы первого и дополнительного резистивных делителей 19 и 20 объединены с вторым выводом первого резистора 21, с положительным полюсом 5 двухполярного источника 4 питания и базой первого дополнительного транзистора 1 б, эмиттер котороГо объединен с первым выводом первого резистора 21, анодом диода 18 и эмиттером второго дополнительного транзистора 17, база которого подкл 1 очена к точке соединения резисторов дополнительного резистивного делителя 20, а его коллектор соединен С катодом диода 18, эмиттером Выходного гранзистора 15 первого канала 13 и чо 12 ез второй резистор 22 - с общей шиной 7,Второй вход 2 формирователя является входом двухполярного ключа 25, второго канала 14. Выход которого соединен с входом кл 1 оча 24 р-и-р-типо и катодом второго дополнительного диода 12, анод которого соединен с катодом первого дополнительного диода 11., а его анод соединен с инверсным выходом 0 ВЯ-триггера 9, Выход 1(Л 1 оча 24 соединен с вторыми выводами первого и дополнительного резистивнь;х делителей 19 и 20, первые выводь которых подкл 1 очены к отрицательному полюсу б двухполярного источника 4 питания, к первому выводу первого резистора 21 второго канала 14 и к эмиттеру первого дополнительного транзистора 1 б, база которого обьединена с вторым ,водом первого резистора 21, с катод,:, диода 18 и с эмиттером второго ,попс,.,1 тельного транзистора 17, база которого подсоединена к точке соединения резисторов дополнительного резист.;ного делителя 20, а еГО коллектоо соединен с анодо 11 диода 18, с эмиттеро;. выходного транзистора 15 и через Вто 12 О,1 рез 11 сто 2230 35 40 (1 го 50- с общей шиной 7. ри этом коллекторы первых дополнительных транзисторов 1 б обоих каналов 13 и 14 объединены с Р-входом ВЯ-триггера 9 и через резистор 8 - с положительным полюсом 5 двухполярно.О источника 4 питания, а коллекторы вьходных транзисторов 15 обоих каналов 13 и 14 Объединены с выходом 3 формирователя.Формирователь биполярных сигналов работает следующим образом.При подаче питающих напояжений от двухполярного источника 4 питания на Я- входе ЯЯ-триг ера 9- низкий потенциал, тзх как в момент нарастания напрлженх 7 я нз положительном полюсе 5 конденсатор интегрируОщей цепи 10 разряжен и представ. ляет низкое сопротивление, шунтирующсе Ь-вход, при этом на прямом выходе Ц В 8 тригера 9 - высокий потенциал, явлгк 7 Дийся разрешающим и поступающим нз второй вход элемента 2 И - НЕ 23, а на его инвертированном выходе ., - низкий. При 7 гизких уровнях входных сигналов на первом и втором входах 1 и 2 все транзисторы обоих каналов 13 и 14 закрыты (фиг. 2, Овх 1, Овх)1, поэтому на коллекторах первых допслнлтельных транзисторов 1 б - высокий потенциал, который поступает на Й-вход В 8-триггера 9, Через первьй резистор 21, ДЫОД 18 и Второй резистор 22 От положительного полоса 5 протекает ток, создавая на первом рс.эисторе 21 первого канала 18 падение напряжения, равного 0,10,2 В. при котором первый дополнительный транзистор 1 б остгеся закрытьм, на диода 18 от этого тока создается прямое падение напряжения, равное 0,7 - 0,8 В. Тзк кзк элемент 2 И-НЕ 23 закрьт(фиг. 2, с(них 2 з), то на базе выходного транзистора 15 - вьсокое напряжение, равное напряжению на поло.кительном полОсе 5 двухполярного источника 4 питания (ток через реэистивный делитель 19 отсутствует), а на его эмиттере потенциал меньший, чем на базе на величину прямого падения напряжения на диоде 18 и первом резистора 21, т,е, 0,8-1 В. Следовательно, эмитгерньй переход ьыходного транзистора 15 загерт напряжением 0,8 - 1 В.Аналогичны роцессы происходят и вь втором канале 11. Исключение составляет двухполярнь 1 й ключ 25, на выходе которого высокий потенциал +0,5.+0,5 В) запирэе-; ключ 24, построенный на транзисторе р-л-р типа, и второй дополнительный диод 12 фиг, 2,гых.25),В зчестве двухполярного ключа 25 мо. жет быть исг Ольэовзн операционный усилитель, диффере; цизльный усилитель или, кзк сзлый простой - двухполярнуй ключ. Алгоритм их работы - положительный потенциал нз выходс при Отсутствии сигнала на входе и отрицательный потенциал на выходе при псложительном сигнале на его входе, Вторые Гополнительные транзисторы 17 первого и второ о каналов 13 и 14 закрыты, так как их эмиттерные переходы обратно смещены из"за токов,.отекающих через первые реэисторь; 2 , и Отсутствия токов через дополнительные резистивные делители 20 этих каналов,ТЗКИМ ОбраЗОМ,ЭМИттерНЫЕ ПЕрЕХОдЫ вторых догОлнлте(Ьных транзисторов 17 Обоих каналов абра-носмещены напряже,;лем С,1 - 0,2 В, ксторое падает на первом :;еэлсто.,".е 21.Гри ио 1 зче з первый вход формиро- ВатЕЛЯ В МОМЕНТ т-.МПУЛЬСа ПОЛОжИтЕЛЬНОй гс 1(7 ярносги Ывх.7 (ф 7 Г. 2, Овх.) элел 4 ент 2 ИНЕ 23 Открывается до насыщения и на его выходе формируется импульс отрицательной полярности относительно положительного напряжен, равного напряжению п Ол ожител ь ног о:",Ол юса 5 двухполя рно го ИСтОЧНИХЗ 4 ПИТЗК 7 Я (фЛГ. 2, О 7 ых.2 З), ОдкО- временно с этим процессом начинают течь токи через первый и дополнительный резистивные делители 19 и 20 первого канала 13,чгго пп 1 од 1, к с 7:47 ыти;о ВыходнОГО и Рто ОО;О поЛслг;л с- ь:1 тоанз" сторО 3 15 и( - р:. Это" н; ря.ан 4 а:ежду коллектором и ЭЛЛ.ГТЕЭ 7" ЭТИХ Т;ЗНЭИСГОРОВ СТЗНОВЯТСЯ г;Ор;:т:з 0,10,2":;: .,е. Второй дополнительный трзнзистср 17 шунтирует диод 18 и на выхода 3 фс рмирователя возникает импульс положительной голЯРностчи Оглх флг. 2, Бвых), амплитуда которого Оавнз величине наг Ояжания поО 7 итель 4 ОГО полюса 5 двух- полЯОНОГО истонз 4 Г 7 итзниЯ, м 7 нус падение напряжения нз первом резисторе 21 от и.Отекания через него двух токов: номизльног 7 тока Вгрузки и тока через этОт реэстор 21, дио., 18 и второй реэистоо 22, КОЛ Орос равно 0,30,4: и не ожет Открыть арф:й Дополниельный транзистор 16, такие минус Лзпря 7 е ия коллектор - эмит;ер выходного и второго дополнительного транзисторов 15 и 7, которые составляот 0,10,2 В, т.е, а;.Г, 7 лтудз выходного сит Зла Равла Ы;,.х:=-Е 7-0,4-0,2-0,2=-Е 7-0,8 В, а бЕЗ птс;рого допо.н 4 гльОГО транзистора 17 ам пл 4 тудз выхос н ОГО си Г наг з равна,.-Е 1-0,4-0,9-0,7.:=.=1 - 1,5 Б, где Е- веЛИЧИЗЗ ПряхЕНИЯ Г 7 ОЛОЖИТЕЛЬНОГО ПОЛЮ- сз 5; О,9 - падение нзпояжения нз диоде 18.ц О л е (-, л и ч а г и я 3 м и л и т у д ы В ыходОГО синала введение второго допслнитольного транзистора 1; позволяет рагу додать длиельностями перо;. 4 гхго и Заднего,:.7 РОНТОВ ВЫХОДНОГО ИМПУЛЬСЗ В ПРЕ 1780156делах от 30 до 120 нс путем изменения величин резисторов первого и дополнительного резистивных делителей 19 и 20 фиг. 2, Овых) а Тахжв ВЫбОРОМ СООТВЕТСТВуЮЩИХТИ- пов транзисторов: выходноо и ворого доголцительного 15 и 17, у которых величины емкостей коллекторного и эмиттерного переходов существенно влияют на длительности переднего и заднего фронтов выходного сиГнала 7 ф 1 и т ф 2 (фиг. 2, Овых).При изменении амплитуды ВходнОГО сигнала в момент ц на первом входе 1 формирователя с вь 1 сокого уровня на низкий (фиг. 2, О, х,1) происходит запирание элемента 2 И - НЕ 23, на выходе которого происходит формирование заднего фронта выходного импульса, сВязанное с зарядами емкостей эмиттерного перехода выходного транзистора 15 и коллекторцого перехода вторс 1 го дополнительного транзистора 17. Затем пооисходит запирание эмиттерного перехода выходного транзистора 15 обратным напряжением, создаваемым за счет протекания тока. через первый резистор 21, диод 18 и второй резистор 21 и подачи полного напряжения Е 1 положительного иоллоса 5 двухполярного источника 4 питания на базу этого транзистора, что уменьшает время рассасывация неосновнь 1 х носителей в его базе, а следовательно, уменьшает задержку заднего фронта выходного импульса Относительно входного с 80 нс до 1520 нс 80100 нс - удлинение выходного сигнала без запирающего напряжения и 1520 нс - удлинение выходного сигнала при подаче на эмиттерный переход выходного транзистора 15 запиоающего напряжения).При подаче импульса положительной полярности на второй Вход 2 формирователя в момент т 1,(фиг, 2, О,х 2) на выходе двухполярного ключа 25 происходит изменение полярности выходного сигнала с положительной на Отрицательную фиг, 2, Ооых 2 Б). Выходной сигнал (импульс) отрицательной полярности с вь.хода двухполярного клокоча 25 поступает на вход ключа 24 р-п-р-типа, открывает его и на его выходе формируется импульс положительной полярности относительно отрицательного напряжения этрицательного полюса 6 двухполярного ИСТОЧНИКа 4 ПИТВЦИЯ (фИГ, 2, Овых 24), ОДНО- временно этот импульс поступает на катод второго дополнительного диода 12. но так как здесь вкл;очены два последовательно соединенных первый и втооой дополнительнь 1 е диоды 11 и 12, то суммарное их сопротивление значительно больше входного сопротивления клокоча 25 и весь ток практически поступает в базу этого ключа, Дальше начинают протекать процессы, ацалогич ные процессам первого канала 13, описанные выше. На Фиг, 2 Овых=ф) изображена эпюра выходного напряжения формирователя, на которой видно значительное уменьшение задних Фронтов,ф 2 импульсов из-за очень короткого времени окончания импульса на первом входе 1 и началом импульса на втором входе 2, Здесь происходит быстрое запирание коллекторного перехода выхсдного транзистора 15 р-и-р-типа первоо канала 13, так как его коллектор поступает напряжение отрицательной полярности и запирает его, Аналогичный процесс происходит и во втором канале 14, Задержка переднего фронта выходного импульса составляет 1520 нс (на фиг, 2 не показана), Длительность переднего фронта Тф 1=120 нс; ф 2=1015 нс. Длительность переднего фронта может быть уменьшена до 30 нс путем выбора выходного и второго дополнительного транзисторов 15 и 11.Период выходных импульсов больше периода входных на 10,15 нс за счет задержки переднего фронта выходного импульса. На фиг. 2 Овых=1(т) показаны также единичные 30 35 40 45 50 55 выходные импульсы, длительность переднего и заднего фронтов которых одинакова и равна 120 нсБыстродействие формирователя достигается путем подачи запирающих напряжений на эмиттерные переходы Выходных транзисторов 15 обоих каналов 13 и 14 и запирающего напряжения положительной полярности на вход ключа 24 второго канала 14,Защита от перегрузки по току в формирователе осуществляется следующим образом,Пусть во время действия входного импульса на первом входе 1 формирователя произошло несанкционированное короткое замыкание на его выходе 3, при этом резко возрасчает его выходной ток, который увеличивает падение напряжения на первом резисторе 21 первого канала 13 до 0,8 В, что приводит к открыванию первого дополнительного транзистора 1 б и уменьшению напряжения на его коллекторе, а следовательно, и на В-входе КЯ-триггера 9, приводящее к измененио его состочция, т.е, на его и:",мом выходе 0 - низкий потенциал, котс й поступает на второй вход элемента 21 Е и блокирует его, а на вго инверсном выходе Ц - высокий положительный потенциал, который запирает ключ 1, об;- выходцых транзистора 15 обои; кацалггв 13и 14 закрыты.Формула изобретенияФормирователь биполярных сигналов, содержащий два входа, выход, двухпалярный источник питания, общий вывод которого соединен с общей шиной формирователя, 5 резистор, один вывод которого соединен с положительным полюсом двухполярного источника питания, два канала, каждый из которых содержит выходной транзистор, диод и первый резистивныйделитель., при О этом коллекторы выходных транзисторов обоих каналов обьединены с выходом формирователя, а их базы подключены к общему вйводу резисторов первых резистивных делителей, первые выводы которых падклю чены соответственно к положительному и отрицательному полюсам двухполярного источника питания, причем второй канал содержит дополнительно ключ, проводимость транзистора которого противоположна пра водимости выходного транзистора первого канала,отличающийсятем,что,сцелью защиты от перегрузки.па току, повышения быстродействия и амплитуды входного сигнала, в него введены ВЯ-триггер с интегри рующей ВС-цепью, общий вывод резистааа и конденсатора котааой подключена к Я- входу этого тоиггера; а вторые выводы резистора и конденсатора подключены соответственно к положительному попасу ЗО двухполярного источника питания и к общей шине, а также два дополнительных диода, анод первого из которых подключен к инверсному О-выходу ВЗ-триггера, а его катод - к аноду второго дополнительного диода, при чем в каждый канал введены два дополнительных транзистора, проводимость которых в первом канале противоположна, а ва втором - одинакова с проводимостью выходного транзистора, дополнительный резистивный 40 делитель и два резистора, кроме того, впервый канал введен элемент 2 И - НЕ, а ва второй - двухполярный ключ, положительный и отрицательный выводы питания которого подключены соответственна к положительному и отрицательному полюсам двухполярного источника питания, при этом коллекторы первых аполнительных транзисторов пеовага и второго каналов соединены с вторым зывадом аез. стара и с В-входом ВЯ-триггера, параллельно змиттерным переходам этих транзисторов подключен первый резистор, первый вывод которого соединен с эмиттерам второго дополнительного транзистора, а ега коллектор соединен с эмиттерам выходного транзистора и через второй резистоо - с общей шиной, а база второго дополнительного транзистора подключена к сбщему выводу резисторов дополнительного резистивнаго делителя, первый вывод котора:-а в первом канале подключен к положительному пал юсу двухполярного источника питания и к базе первого дополнительного транзистора, эмиттер котаааго соединен с анодам диода, а его катод - с эмиттерам выходного транзистора, второй вывод дополнительного резистивного делителя объединен с вторым выводом резистивнаго делит ля и выхбдом элемента 2 И-НЕ, первый вход которого соединен с гервь:м входам ;армиравателя., а второй ега в,;ад с прямым-выходам ВЗ-триггера, второй вход формирователя соединен с входам дв,хпалярнага клкча второго канала, к выходу катарага подклачены катод второго далалнительнага -,нада и вход ключа, а ега выход соединен с вторыми выводами первого и дапалнительнога резистивных делителей, первый вывод дополнительного резистивнагоелптел;: второго канала падкл.ач.=н к отрицательному полюсу двухполяр. ага источника питания и эмиттеру первсга дополнительного транзистора, база катарага саеди ,ена с катодом диода, а ага анод - с эмиттерам выходного транзистора второго канала,оставитель О, Венеди,:.ехред М.Моргентал Корректор А, Козор Редак Производ енно-издательский комбинат Патент", г, Ужгород, ул,Гагарина, 10 аказ 4440 Гираж ВНИИПИ Государственного комитета по изобрете 113035, Москва, л(-35, РаушскПодписноениям и открытиям при ГКН я наб.,4/5

СмотретьЗаявка

4870689, 02.10.1990

КОНСТРУКТОРСКОЕ БЮРО ЭЛЕКТРОПРИБОРОСТРОЕНИЯ

ВЕНЕДИКТОВ ОЛЕГ ЛЕОНИДОВИЧ

МПК / Метки

МПК: H03K 5/01

Метки: биполярных, сигналов, формирователь

Опубликовано: 07.12.1992

Код ссылки

<a href="https://patents.su/6-1780156-formirovatel-bipolyarnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь биполярных сигналов</a>

Предыдущий патент: Импульсный усилитель

Следующий патент: Устройство фиксации уровня

Случайный патент: Сошник