Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1661762

Авторы: Гаазе, Слесаренко, Чернятин

Текст

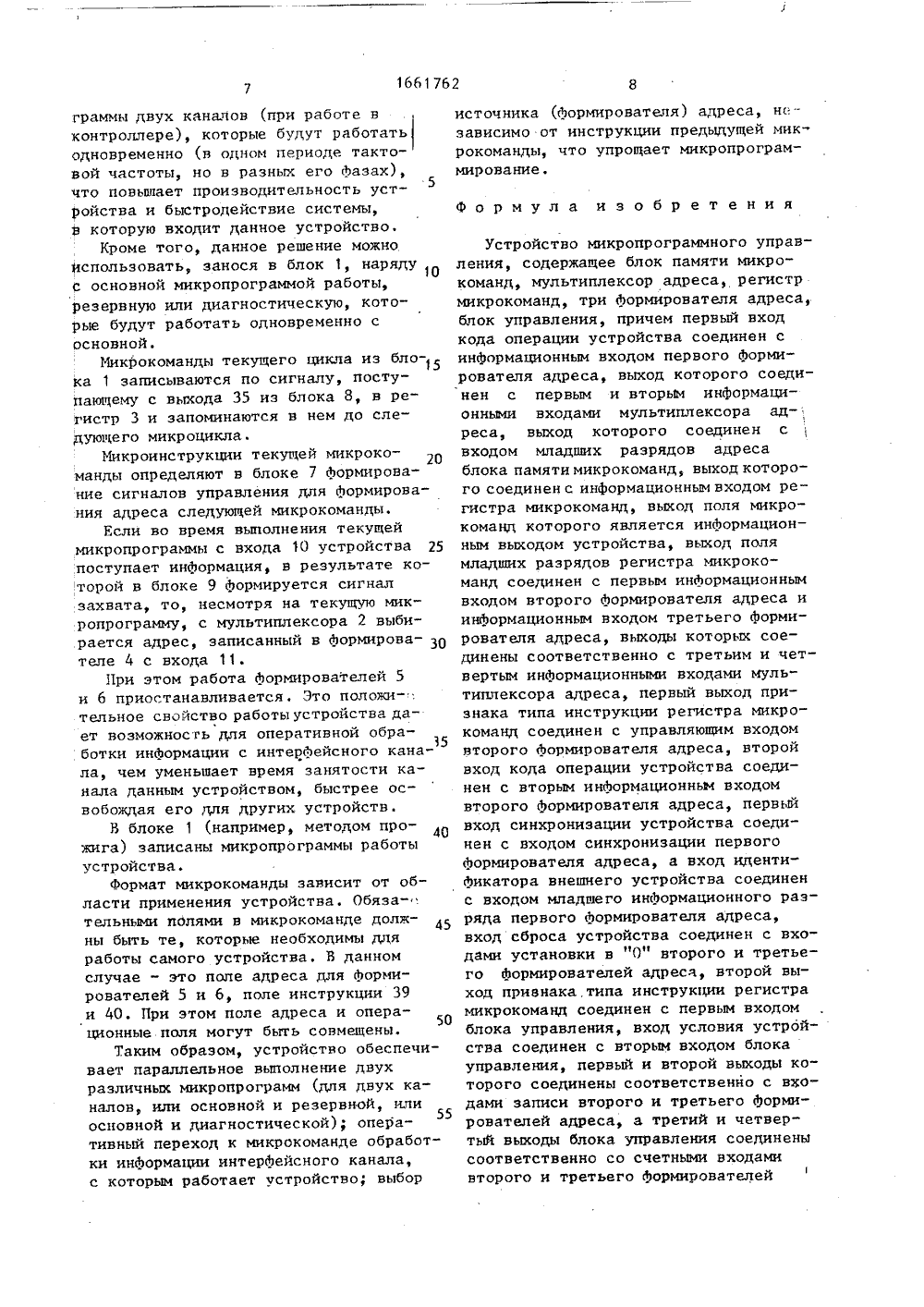

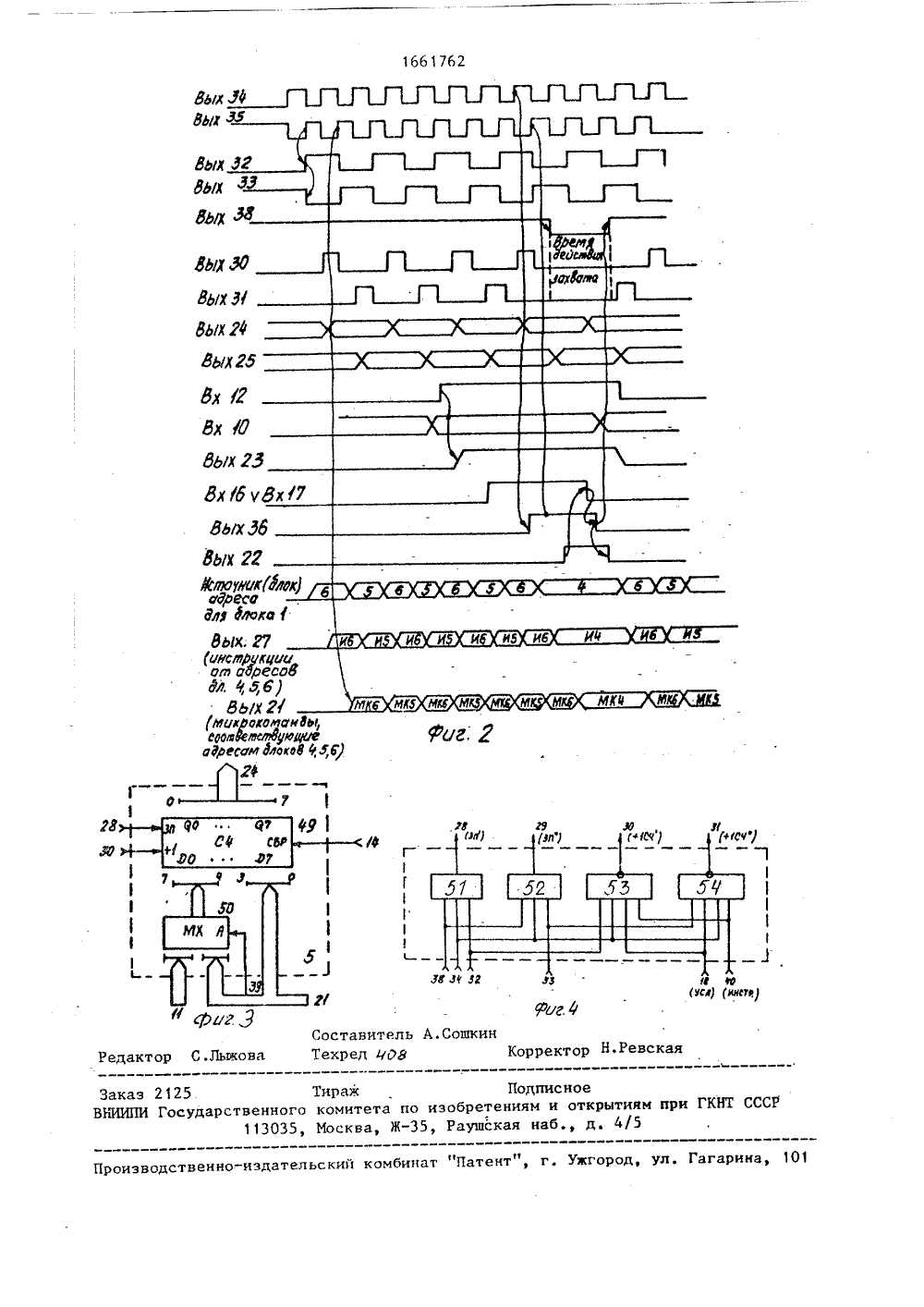

(5 ц 5 ( 06 Р 9/22, 9/46 ОПИСАНИЕ ИЗОБРЕТЕНИЯК А ВТОРСНОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТ 8 ЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР(56) Проектирование питеровых систем нз. комплектах микропрограммируемых БИС. М.: Радио и связь, 1984, гл . 4,3Иик Лж., Брик Дж. Проектирование микропроцессорных устройств с разрядно-модульной организацией. - И.; 11 ир, 1984, с. 43.(57) Изобретение относится к вычислительной технике и предназначено дляобеспечения микропрограммного управления устройств обработки данных, Целью предлагаемого изобретения является повьппение быстродействия. Устройство содержит мультиплексор адреса, реИзобретение относится к цифровойвычислительной технике и может найти применение при проектировании микропроцессоров, контроллеров, ЭВ 11 и вычислительных систем с микропрограммным управлением и высоким быстродействием, а также предназначено дляреализации разнообразных управляющихЬункций, важнейшими из которых являются: определение последовательностимикрокоманд, выбираемых из блока памяти микропрограмм и анализ сигналовсостояния из центрального процессора,Яц 1661762 А 1 гистр микрокоманд, блок памяти микро- команд, с первого по четвертый элементы И, элемент ИЛИ, первый и второй элементы И-ИЕ, элемент НК, элемент сложения по модулю 2, регистры команд и адреса, первый и второй счетчики, первый и второй мультиплексоры, Т-триггер, с первого по третий П-триггеры, схему сравнения. Новыми в уст - ройстве являются третий и четвертый .элементы И, элемент ИЛИ, элемент ИЕ, Т-триггер, с первого по третий П-триггеры, схема сравнения, схема сложе - ния по модулю 2. Введение дополнительных блоков позволило в одном устройстве микропрограммного управления обеспечить параллельную работу двух микропрограмм разных каналов и рпера-. тивный переход на подпрограмму обработки информации приоритетного канала, С Это достигается разделением во времени информации, коммутируемой мультиплексором адреса. 4 ил., 1 табл.Ффвй или других устройств, работающих н системе для принятия решений о переходах в микропрограмме,1 ель изобретения - повышение быстродействия устройства (что обеснечивается возможностью одновременного :В выполнения двух микропрограмм, независимых друг от друга).Иа Миг, 1 представлена функциональная схема устройства; на Лиг. 2 - общая диаграююа работы устройства, синхронизируемого "игналами, поступающими от внешнего генератора на входсинхронизации устройства; на .иг, 3 -пример реализации первого Аормирователя адреса; на Аиг. 4 - пример реализации блока управления.5Устройство (Аиг. 1) содержит блок1 памяти микрокоманд, мультиплексор 2адреса, регистр 3 микрокоманд, Аормирователи 4 - 6 адреса, блок 7управления, блок 8 синхронизации, 10блок 9 захвата инициативы,На )иг, 1 приняты также следующиеобозначения: первый вход 10 кода операции, второй вход 11 кода операции,первый вход 12 синхронизации устройства, второй вход 13 синхронизацииустройства, вход 14 сброса устройства, вход 15 идентиАикатора внешнегоустройства, вход 16 признака чтенияустройства, вход 17 признака записиустройства, вход 18 условия устройства, вход 19 управления записи кодаоперации устройства, вход 20 адресаустройства, выход 21 шины микрокоманды, являющийся инАормационным выходом 25устройства, выход 22 ответа-признакапринятия кода операции, группа 23 соединений между выходом Аормирователя4 и первым и вторым инАормационнымивходами мультиплексора 2 и входомблока 9, группа 24 соединений междувыходом блока 5 и третьим инАормационным входом мультиплексора 2, группа25 соединений между выходом блока 6и четвертью входом мультиплексора 2,группа 26 соединений между выходоммультиплексора 2 и входом блока 1,группа 27 соединениймежду выходамиблока 1 и входамирегистра 3,первый выход 28 записи блока 7, второй выход 29 40записи блока 7, первый выход 30 счетаблока 7, второй выход 31 счета блока 7, выход 32 тактовой частоты положительного потенциала блока 8, выход33 тактовой частоты нулевого потенциала блока 8, прямой выход 34 синхроимпульсов блока 8, инверсный выход 35синхроимпульсов блока 8, прямой выход36 сигнала захвата блока 9, инверсныйвыход 37 сигнала захвата блока 9, вы 50ход 38 выбора ответа блока 9, выходы39 и 40 признаков типов инструкциирегистра 3Кроме того, блок 9 (Аиг.1)содержит три П-триггера 41-43, элемент 44 сложения по модулю 2; дваэлемента И 45 и 46, элемент ИЛИ 47 иэлемент сравнения 48.Блок 1 представляет собой постоянное запоминающее устройство, в которое, например, методом прожига заносятся необходимые микропрограммы,Мультиплексор 2 коммутирует. инАормацию с четырех направлений на один выход в зависимости от кода,поступающего на два его управляющих входа.Регистр 3 представляет собой регистр, инАормация в который записывается по переднему Аронту поступающего на его синхровход синхроимпульсаФормирователь 4 адреса может быть выполнен в виде регистра адреса, в который под действием сигнала,.поступающего на вход 12 устройства, записывается инАормация с входа 10 устройства.Формирователь 5 адреса (Аиг. 3) содержит счетчик 49 и мультиплексор 50 на два направления, который коммутирует инАормацию (с входа 11 устройства или с шины 21 микрокоманд) на входе счетчика в зависимости от типа инструкции (39), поступающеч на адресный вход мультиплексора с шины микрокоманды.Формирователь 6 адреса может быть представлен в виде счетчика.В зависимости от выбранной элементной базы Аормирователи 4-6 адреса могут быть выполнены независимо друг от друга, либо в виде единого Аормирователя адреса с той же совокупностью входов/выходов, что и у совокупности Аормирователей 4-6. Блок 7 управления устройством (Аиг, 4) содержит два элемента И 51 и 52 и два элемента ИЛИ 53 и 54.Блок 8 синхронизации устройства представляет собой Аормирователь серии импульсов, необходимых для синхронной работы блоков устройства.Устройство работает следующим образом,На вход 13 блока 8 поступают синхроимпульсы от внешнего генератора. На основе этих импульсов в блоке 8 Аормируется серия импульсов на выходах 32 - 35 разной длительности и Аазы, Импульсы на выходах 34 и 35 блока 8 находятся в противоазе один относительно другого и соответствуют частоте поступающих на вход 13 устройства импульсов. Импульсы на выходах 32 и 33 блока 8 Аормируются путем деления на 2 частоты импульсов с входа 13, например на счетном триггере.62бприостанон работы Аормирователей адреса 5 и 6, т.е. на время выполнения действия, вызванного микрокомандой по захвату, состояние Аормирователей 5 и 6 не меняется.При отсутствии сигнала захвата (выход 36) (его потенциал равен О) на вход блока 1 через мультиплексор 2 поступает адрес с Аормирователя 5 или Аормирователя 6 в зависимости от потенциала сигнала, поступающего с выхода 32 блока 8 (см. таблицу)На инАормационные входы Аормирователя 5 поступает инАормация с входа 11 устройства и с выхода регистра 3 шины 2 1. В зависимости от управляющих импульсов, поступающих с блока 7 формирователь 5 работает, например, в режиме накопителя или счетчика. В режиме накопителя Аормирователь 5 запоминает и выдает на мультиплексор 2 инАормацию, которая записывается в него по сигналу записи с выхода 28 блока 7, входа 11 и шины 2,1 или только с шины 21. Это зависит от инструкции, поступающей в Аормирователь 5 с регистра 3 в виде разряда микрокоманды (выход 39).В режиме счетчика, например, в формирователе 5 происходит изменение значения адреса на +1 по каждому сигналу счета, поступающему с выхода 30 блока 7.Работа Аормирователя 5 происходит при потенциале сигнала на выходе 32 блока 8, равном 1. Это определяется блоком 7, Аормирующим сигналы записи на выходе 23 и счета на выходе 30.Работа и режим работы Аормирователя 6 могут быть аналогичны работе формирователя 5. Только Аормирователь 6 должен работать при потенциале сигнала на выходе 33 блока 8, равном О, что определяет в блоке 7 Аормирование сигналов записи ва выходе 29 и счета на выходе 31.В результате того, что на один из двух управляющих входов мультиплексора 2 заведен тактовый сигнал с выхода 32, а Аормирователи 5 и 6 работают в разных полупериодах .тактов, при отсутствии сигнала захвата на выходе 36 выборки адреса с мультиплексора 2 производится поочередно с Аормирователя Аормирователя 5 и 6 за один период тактового сигнала (Аиг. 2). Это дает возможность заносить (например, методом прожига) в блок 1 микропроКод адреса на управляющих входах сточник адреса 40 сигнал 36 сигнал. 32 0 0 О 1 1 0 1 1 формирователь 5 45 формирователь 6 Формирователь 4 Формирователь 4 Из таблицы видно; что при наличии 50 сигнала 36 (его потенциал равен 1) через мультиплексор 2 проходит адрес с формирователя 4 (независимо от потенциала сигнала 32), так как Аормирователь 4 соединен с двумя инАормационными входами мультиплексора 2, который, поступая на блок 1, вызывает соответствующую интерАейсному каналу мыкрокоманду. На это время происходит 516617Блок 7 Аормирует управляющие сигна 1 лы на выходах записи 28 (Зп) и счета 30 (+1 Сч) для Аормирователя 5 и записи 29 (Зп") и счета 31 (+1 Сч ) для Аормирователя 6 в зависимости от сигнала условия, поступающего на вход 18 устройства, типа признака инструкции 40 с шины 21, а также сигналов с выходов 32 - 34 блока 8 и сигнала с выхода 38 блока 9.ПнАормация, поступающая с интерфейсной шины на вход 10 устройства и сопровождаемая сигналами, поступающими по входам 12 и 15, записывается в блок 4, с выхода которого поступает на первый и второй инАормационные входы мультиплексора 2 и на инАормационный вход 23 блока 9, вход 20 которого закоммутирован на тот адрес, который 20 присвоен устройству на интерАейсной магистрали. Если поступившая инАормация и скоммутированный адрес совпадают, то в блоке 9 Аормируется сигнал захвата (выход 36), который сви детельствует о наличии информации на входе 10, требующей обработки в приоритетном порядке. Это в устройстве достигается тем, что сигнал с выхода 36 блока 9 заведен на один из управляю щих входов мультиплексора 2, на второй вход которого завещен тактовый сигнал с выхода 32 блока 8. Кодовая комбинация этих сигналов определяет источник адреса, который выбирается из мультиплексора 2 для текущей микро- команды, выбираемой из блока 1, что представлено в таблице.граммы двух каналов (при работе вконтроллере), которые будут работатьодновременно (в одном периоде тактовой частоты, но в разных его фазах),что повышает производительность устройства и быстродействие системы,9 которую входит данное устройство.Кроме того, данное решение можноИспользовать, занося в блок 1, наряду 1 ОС основной микропрограммой работы,резервную или диагностическую, которые будут работать одновременно сосновной.Иикрокоманды текущего цикла из бло ка 1 записываются по сигналу, поступающему с выхода 35 из блока 8, в регистр 3 и запоминаются в нем до следующего микроцикла.Микроинструкции текущей микрокоманды определяют в блоке 7 формирование сигналов управления для формирования адреса следующей микрокоманды.Если во время выполнения текущеймикропрограммы с входа 10 устройства 25поступает информация, в результате которой в блоке 9 формируется сигналзахвата, то, несмотря на текущую микропрограмму, с мультиплексора 2 выбирается адрес, записанный в Аормирова Отеле 4 с входа 11.При этом работа формирователей 5и 6 приостанавливается. Это положи- .тельное свойство работы устройства дает возможность для оперативной обра 15ботки информации с интерфейсного канала, чем уменьшает время занятости канала данным устройством, быстрее освобождая его для других устройств.В блоке 1 (например, методом прожига) записаны микропрограммы работыустройства.Формат микрокоманды зависит от области применения устройства. Обяза"тельными полями в микрокоманде должны быть те, которые необходимы дляработы самого устройства. В данномслучае - это поле адреса для формирователей 5 и б, поле инструкции 39и 40. При этом поле адреса и операционные поля могут быть совмещены.Таким образом, устройство обеспечивает параллельное выполнение двухразличных микропрограмм (для двух каналов, или основной и резервной, илиосновной и диагностической); опера 55тивный переход к микрокоманде обработки информации интерфейсного канала,с которым работает устройство; выбор источника (формирователя) адреса, н зависимо от инструкции предыдущей мик рокоманды, что упрощает микропрограммирование.Формула изобретенияУстройство микропрограммного управления, содержащее блок памяти микро- команд, мультиплексор адреса, регистр микрокоманд, три формирователя адреса, блок управления, причем первый вход кода операции устройства соединен с информационным входом первого формирователя адреса, выход которого соединен с первым и вторым информационными входами мультиплексора адреса, выход которого соединен с входом младших разрядов адреса блока памяти микрокоманд, выход которого соединен с информационным входом регистра микрокоманд, выход поля микро- команд которого является информацион - ным выходом устройства, выход поля младших разрядов регистра микрокоманд соединен с первым информационным входом второго формирователя адреса и информационным входом третьего формирователя адреса, выходы которых соединены соответственно с третьим и четвертым информационными входами мультиплексора адреса, первый выход признака типа инструкции регистра микро- команд соединен с управляющим входом второго формирователя адреса, второй вход кода операции устройства соединен с вторым информационным входом второго формирователя адреса, первый вход синхронизации устройства соединен с входом синхронизации первого формирователя адреса, а вход идентификатора внешнего устройства соединен с входом младшего информационного разряда первого формирователя адреса, вход сброса устройства соединен с входами установки в "0" второго и третьего формирователей адреса, второй выход признака типа инструкции регистра микрокоманд соединен с первым входом блока управления, вход условия устройства соединен с вторым входом блока управления, первый и второй выходы которого соединены соответственно с входами записи второго и третьего формирователей адреса, а третий и четвертый выходы блока управления соединены соответственно со счетными входами второго и третьего формирователейадреса, о т л и ч а ю щ е е с я. тем, что, с целью повышения быстродействия, введены блок синхронизации и блок захвата инициативы, который содержит элемент сравнения, три Л-триггера5 первый и второй элементы И, элемент ИЛИ и элемент сложения по модулю 2, причем второй вход синхронизации устройства соединен с первым входом блоО ка синхронизации, первый выход которого соединен с первым входом первого элемента И и с третьим входом блока управления, второй выход блока синхронизации соединен с входами синхро низации регистра микрокоманд и второго Э-триггера, третий выход блока синхронизации соединен с четвертым входом блока управления, с первым разрядом управляющего входа мультиплексора20 адреса, первым входом элемента сложе.ния по модулю 2, выход которого соединен с 0-входом первого й-триггера, прямой выход которого соединен с вторым разрядом управляющего входа муль тинлексора адреса и с 0-входом второго Р-. триггера, инверсный выход которого соединен с входом установки ъ "О" первого Э-триггера, с С-входом третьего Р-триггера и пятым входом блока управления, четвертый выход блока синхронизации соединен с шестым вхо.дом блока управления и с входом пер"вого старшего разряда блока памятимнкрокомащ, вход второго старшегоразряда которого соединен с инверсным выходом первого П-триггера, входыпризнаков чтения и записи кода операции устройства соединены соответственно с первым и вторым входами элементаИЛИ, выход которого соединен с первымвходом. второго элемента И и входомустановки в "О" третьего Э-триггера,прямой выход которого является признаком принятия кода операции устройства,шина единичного потенциала подключенак Л-входу третьего В-триггера, инверс-ный выход которого соединен с вторымвходом второго элемента И, выход которого соединен с вторым входом первогоэлемента И, выход которого соединенс входом синхронизации первого Р-триггера, вход управления записью кодаоперации устройства соединен с вторымвходом элемента сложения по модулю 2,вход адреса устройства соединен с первым входом схемы сравнения, выходпервого формирователя адреса соединенс вторым входом схемы сравнения, выходкоторой соединен с третьим входом второго элемента И.юг, 4 Составитель А.Сошк Техред 1/РЗ рректор Н,Ревск едактор С,Лыков аказ 2125 Тираж И 1 ИПИ Государственного комитета по изо 113035, Москва, Ж, Роизводственно-издательский комбинат "Патент", г. Ужгород, ул. Гагарина, 10 Вы Вы ВыХ ВЫХ ВЬВ ВЫХ Вьа 8 ыВюафВ М УлПодписноетениям и открытиям при ГКская наб д, 4/5

СмотретьЗаявка

4496651, 21.10.1988

ПРЕДПРИЯТИЕ ПЯ А-3592

ЧЕРНЯТИН ВАЛЕРИЙ МИХАЙЛОВИЧ, ГААЗЕ МИХАИЛ ВИКТОРОВИЧ, СЛЕСАРЕНКО СВЕТЛАНА АЛЕКСАНДРОВНА

МПК / Метки

Метки: микропрограммного

Опубликовано: 07.07.1991

Код ссылки

<a href="https://patents.su/6-1661762-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Генератор случайных чисел

Следующий патент: Устройство с динамическим изменением приоритета

Случайный патент: Датчик давления