Устройство для вычисления степной функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

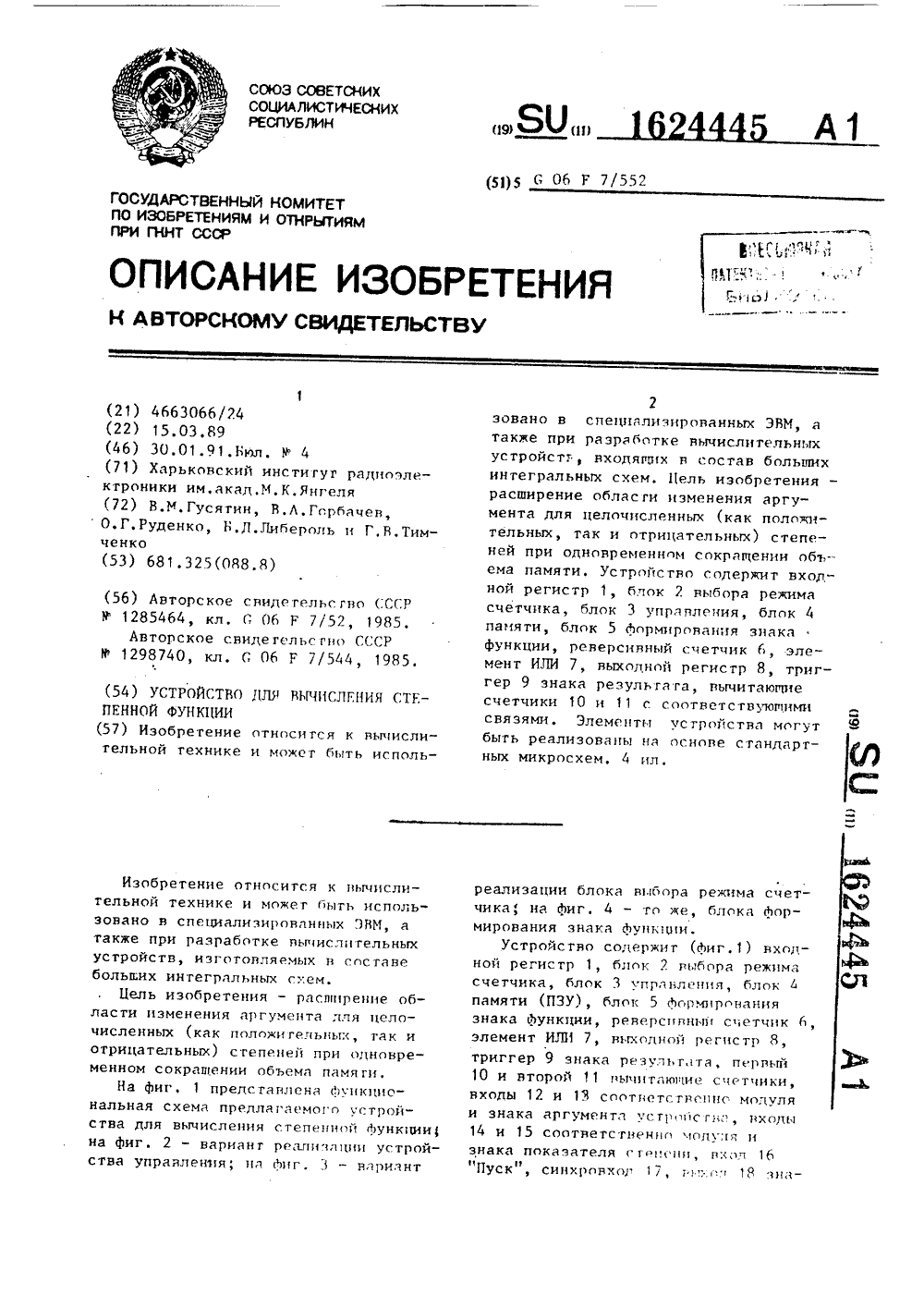

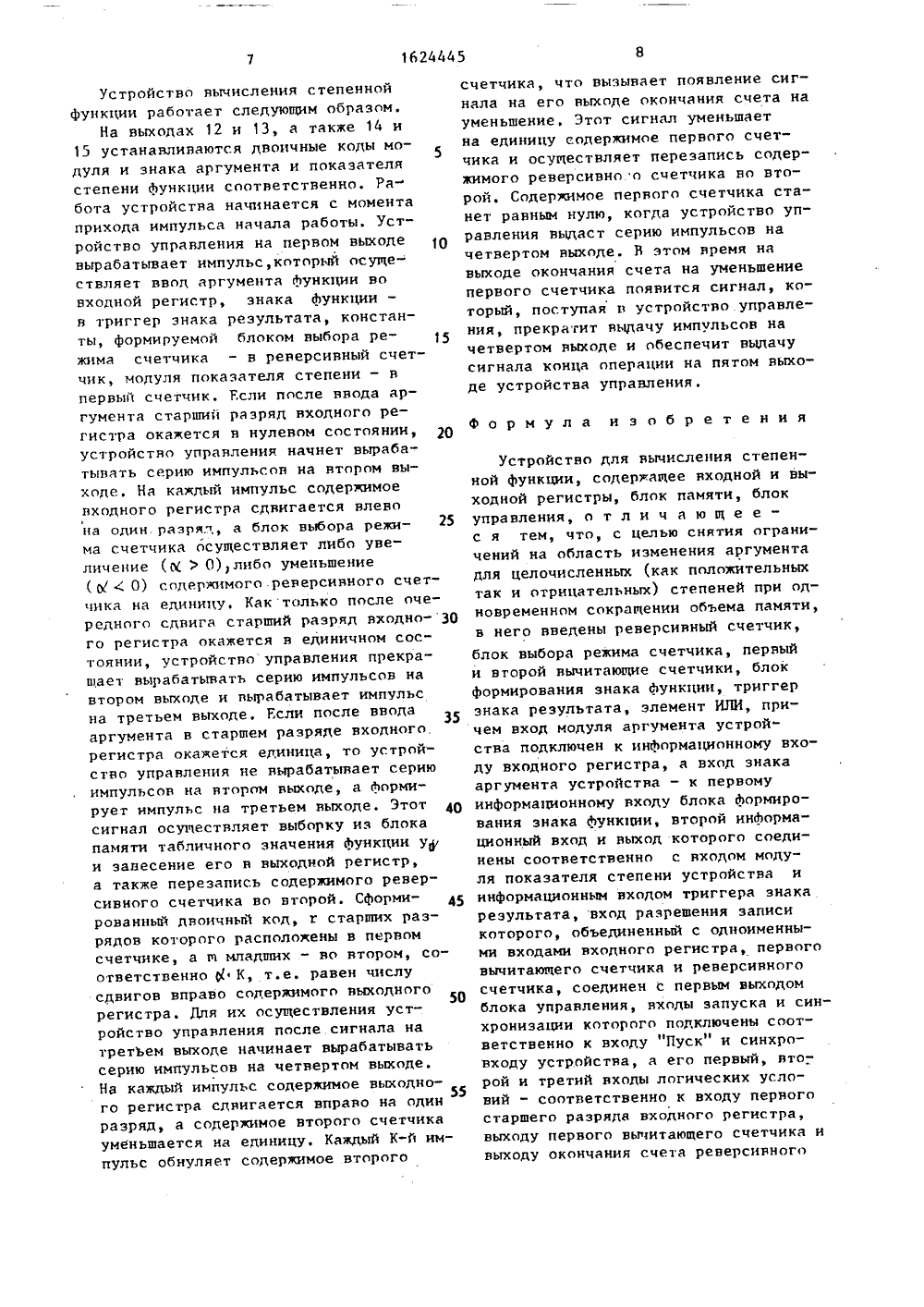

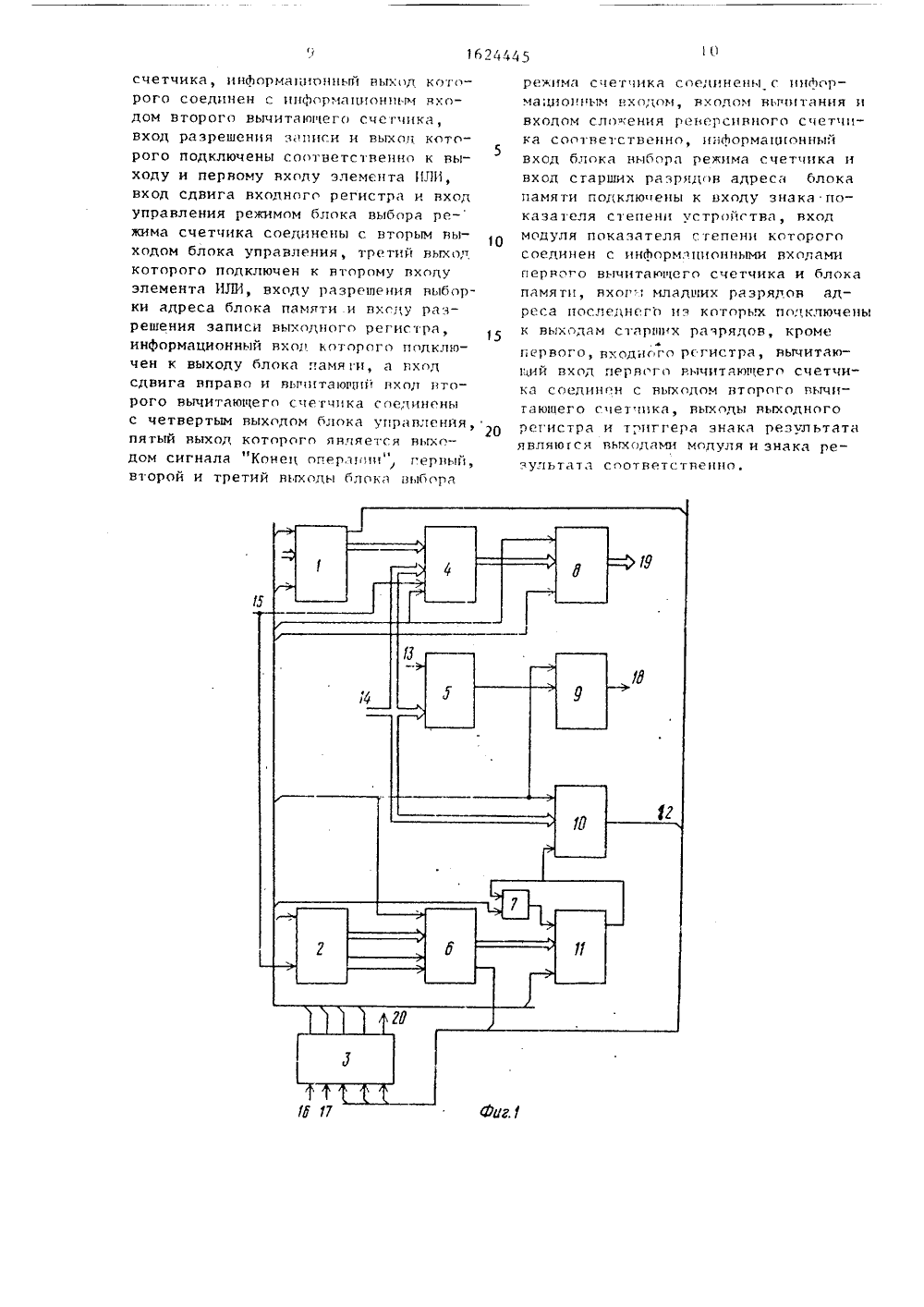

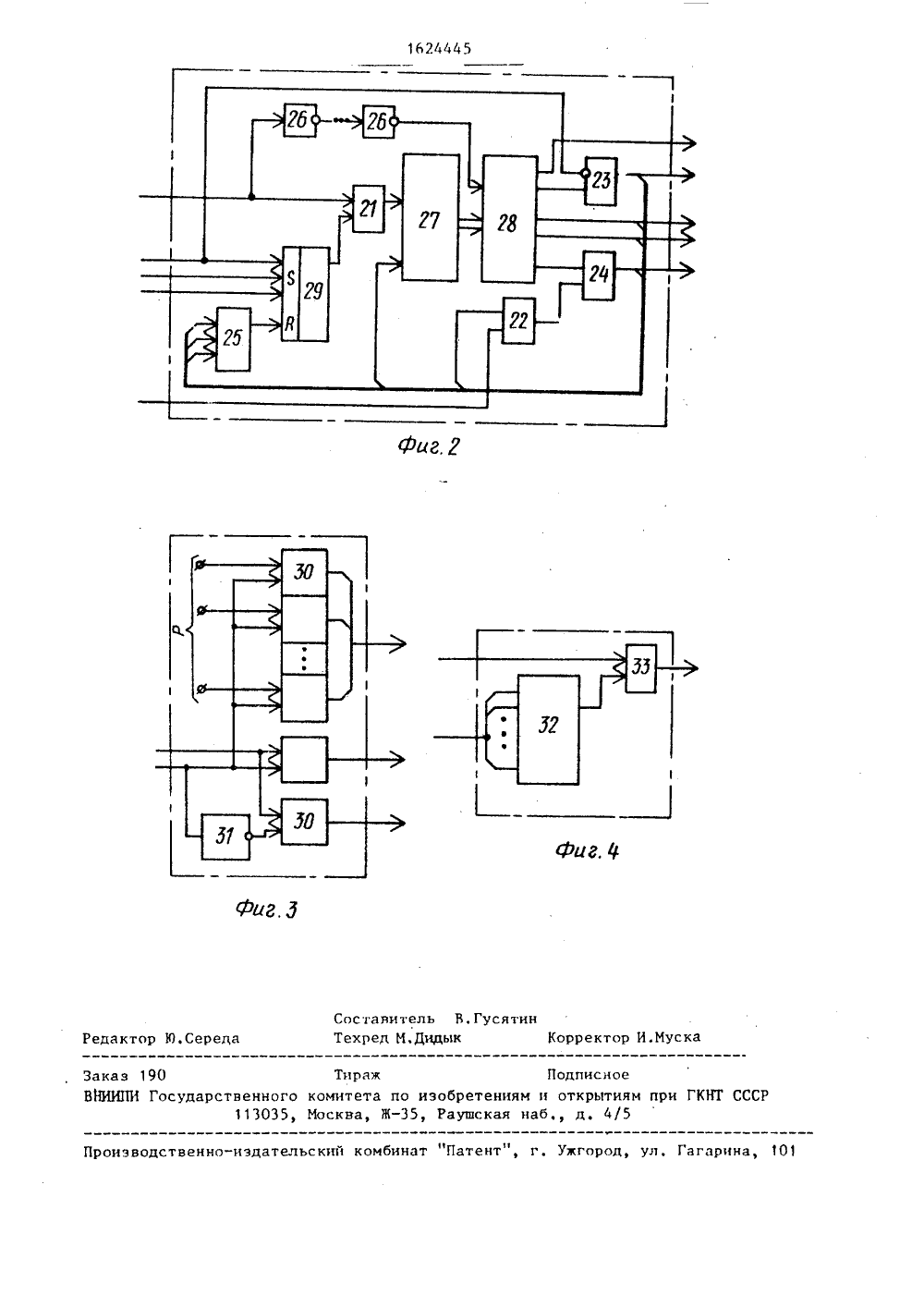

54) УСТРОЙС ЕННОЙ ФУНК 7) Изобрете ельной техни е и может ть испольрежима счетблока фор тельноизовано так строи льших ласти исл трицат енном На ф альная тва длва тва у влещ 1 я ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ К АВТОРСКОМУ СВ ВО ДЛЯ ВЬсИСЛГНИЯ СТЕИие относится к вычисл зобретение относится к ычисл технике и может бытЬ иСпоЛЬ- в специализированных ЭВМ, а ри разработке вычислительных тв, изготовляемых в составе интегральных схем.изобретения - расширение обзменения аргумента лля целоых (как положительных, гак и ельных) с гепеней при одновресокращении объема памяти.иг. 1 представлена функциссхема предлагаемого устройя вычисления степенной функци нг реализации устро на фиг. 3 - вариант эовано в спецттализированных ЭВМ, атакже при разработке вычислительныхустройст., входящттх в состав большихинтегральных схем. ель изобретениярасширение области изменения аргумента для целочисленных (как положительных, так и отрицательных) степеней при одновременном сокращении обьема памяти. Устройство содержит входной регистр 1, блок 2 выбора режимасчетчика, блок 3 управления, блок 4памяти, блок 5 формирования знакафункции, реверсивный счетчик 6, элемент ИЛИ 7, выходной регистр 8, триггер 9 знака результата, вычитающиесчетчики 10 и 11 с соответствующимисвязями. Элементи устройства могутбыть реализованы на основе стандартных микросхем. 4 ил. реализации блока вибо чика, на фиг. 4 - то же,мирования знака функции.Устройство содержит (фиг,1) вход -ной регистр 1, блоквыбора режимасчетчика, блок 3 управления, блок 4памяти (ПЗУ), блок 5 формированиязнака функции, реверспвний счетчик 6,элемент ИЛИ 7, виходной регистр 8,триггер 9 знака резульгата, псрвий1 О и второй 11 вычитающи счетчики,входы 12 и 11 соответсгвепнс модуляи знака аргумента усгр чгс гв , ходи14 и 15 соответственно модуля изнака показателя е гапс нц, вход 1645 ка резуль гата, выход 19 модуля результата и Выход 20 конца операции. Элементы усгройства могут быть реализованы на основе стандартных микро 5 схем.Блок 3 управления (фиг.2) содержит элементы И 21-23, элементы ИЛИ 24 и ,25, элементы НЕ 26, счетчик 27, дешифратор 28, триггер 29, блок 2 выбора режима счетчика содержит элеменгы И 30-30 щ+, элемент НЕ 31.Усгройство управления работает следующим образом.Счетчик 27 имеет пять состояний, с 15 помощью дешифратора 28 каждому состоянию поставлен в соответствие по номерам выход устройства управления. В исходном состоянии содержимое счетчика равно нулю и оно не дешифрирует ся. Из состояния в состояние счетчик перЕводигся синхроимпульсами, поступающими на второй вход устройства управления. Сменой состояний счетчика управляег триггер 29 и элемент И 21, 25 Синхроимпульсы поступают также на первый разрешающий вход дешифратора через цепочку элементов НЕ, которая обеспечивает задержкуимпульса на время окончания переходных процессов в 3 о счетчике. Устройство управления начинает работу с момена прихода на его первый вход импульса начала работы "Пуск", этот сигнал устанавливаеттриггер 29 в единичное состояние.Пер-35 вый синхроимпульс установит счетчик в первое состояние, Этот же импульс поступит на разрешающий вход дешиА- ратора и на его первом выходе,так же как и на первом выходе устройства40 управления, появится импульс.Второй синхроимпульс переводит счетчик во второе состояние, Если при этом ца третьем входе устройства управления установлен уровень логической единицы, т.е. старший разряд входного регистра находится в единичном состоянии, то элемент И 23 по вгорому входу будет заперт ина Втором Выходе устройстВа упраВле ния импульс будет отсутствовать, а третий синхроимпульс переведет счетчик в третье состояние. В противцом случае элемент И 23 будет открыт и первый же импульс с его Выхода установит григгер 29 в нулевое состояние, Это приводит к тому, что второе состояние счегчика не будет изменяться следующими синхроимпульсами до тех пор, пока ца третьем входе устройства управления це появится уровеньлогической единицы, В гчецие времени, когда счетчик будег находитьсяво втором состоянии, устройство управления ца втором выходе будет вырабатывать серию импульсов. Уровеньлогической единицы ца третьем входеус гройс гва управления установиттриггер 29 в единичное состояние, аочередной синхроимпульс переведетсчетчик в третье состояние и на третьем выходе дешифратора и третьем выходе устройства управления появитсяимпульс. Этот же импульс поступаетна первый вход элемец га И 22, еслина втором входе этого лемецта присугствут уровень логической единицы,когда содержимое первого счтчикаравно нулю, на выходе элемента ИЛИ24 и на пятом выходе устройс гва управления ныраба гываетсн сигнал концаоперации. Этот сигнал устанавливаетсяв нулевое состояние григгер 29 и счетчик 27, Если это не происходи г, гоочередной синхроимпульс переведетсче гчик в четвер го состояние. Первый же импульс с четвртого выходаустройства управления установит триггер в нул .вое состояние, э го приндегк тому, чо че гвртое сос гояцие счетчика не булег изменяться следующимисинхроимпульсами до тех лор, пока цачетвертом вход устрой гва управления це появится уровень логической единицы, когда содержимое первого счетчика станет равным пулю. В течение времени, когда счегчик будет находиться в четвертом состоянии, устройсгво управления будет вырабатывать серию импульсов ца че-вертом выходе. Уровень логической единицы ца четвергом входе устройства управления установи г триггер в единичное состояние, а очер,цой синхроимпульс переведег счегчик в пятое состояние, На лятом выходе устройства управления появигся сигнал конца операции.Принцип рабогы блока выбора режима счетчика (фцг.З) состоит в том, что ца гервый вход потуцает импульс, а на второй вход - знак показателя степени функции. Если ца втором входе устананлив, гся уронць логической единицы 1 ф :. О), то импульсы с перво- Ьго вхопа поступаюг на второй выход, а на первом выходе появляется ш-разрядный двоичный код числа Р, который здддетсл ндрн х ц , хментоВ И 1-и со(.Г 1 Ри 1 д(ц 11кой, РСП 1 цд Е Ором (ХОЕР УГ г НднпиБает .я уронРИЬ логи" с ко 1 о ну 1 я(Ь.,) О), ТГ ИМу,1 С Г ПСрНОГ О ВХОДПОСТУПС)Г Нс ТРРТИ 1 ЕХО;)Д Цс 1 РРВГМ выходе ед всех рдзрддх уст;ц;вИвается уровень логи ского нуля. И Быхоле бкд 5 форови 5 ка функции (Аиг,.) УГ гдцавливдс.т я уровень логиРГкой с; Пы, с;и аргумент Ауцкиии отри(т(л,цй и ЦЕЧЕтццй ПОКаэсЗТЕ Ст ПРЦИ.11 реллагдемое устройство и вс 5 ят БъчислЯть с тРпРццуО Аункцин) Гу = х где х - поо)(сггРЕе,( и гтрЕатете нье действительц; чи,(лС ПО.10 СИТСПЦЬЭ(ТР 1 Ц", Г .,ЦСцельс .,слд. Уг.1 ос,ог(Г Г1 т вычисления,споц,.уя; ,ч;(С БО 1 СТ(сЗ , РПСц" ;ПИ; И "С Р -грацценно) с. : ;)м цця дг т;. -мецтд, ри этом ;т(я;т (ьц,я и-НОСТЬ БЬ)С.,РЦИ 51 т"ЦС ,УЦ.ЦИ 1нд Вссй области спрцбудет грегьпдт, гсцт(; ц : ,р: 11 ГГ ГИ Е( Т)ЗИЧС)ГСДН 1 ЯТлблиНос сР;( н с ( Рп(ц)ЦРДЕЦМ ШДГ1хЛ(С(КС Г)прРДелим ;исл ПВОИЧНОГО КГЛД тсблич ног о црс О зс,х р ,5;н К аргу Рна н рвалГт;цл(ци ф,ць: и ние,ргум( нтд и К;,с: О(и к 1 з -енеик) Аункцип 1 рд Гце.овд г.1(. -цо, если прел г 1 ц , усис ь гдб -личцс)м Биде д Р.сОро и:и.,5 ц минтевеце, т) зд (чО: (",дци 1 Гдвигд друм( г, и дноозндеИ Ауцкдш, но мо но:гпи( с -ЕцЕ СКОО О: Д (С ; АЦ.П;и Ц ЦС-- Я (б х1 с)Гсчит ц м ин Грвс им 1 НЯ5 аргумента с яд м Л х ны (ислим всезначения АуцкИи и занесем в таблицу,.1.1 я 1 с( с,"д три 1 д. ОГГ ссу 1 д я (1 Гл огдбли Ньх зц,чцй Ауцкиивцо 256.,11, )с сх .", фх. (1 спр;1 НРДлиг х - 2 хн, д для с( сгвет(твуих25 зц ций нкдш у = 2 у г еиО) или нпрдв (с сна К рдзрялп(, 11 осле такг 1 о (;ни а значдргие 4 О РРяды ар умец гд поцдддт в интерндп гдГ)пчц(1 о преес ) свлия ункии,1; ПОЗВОЛЯГт ПОЛучигЬ Р Гао.Ичцс1 чецие у, Лгя поучецил искомогсЕд ения Ауцкнп, получг цно тдбличцое зндчеше ( с лпуст слвинуть наУстройство вычисления степенной функции работает следующим образом.На выходах 12 и 13, а также 14 и 15 устанавливаются двоичные коды мо 5 дуля и знака аргумента и показателя степени функции соответственно. Работа устройства начинается с момента прихода импульса начала работы. Устройство управления на первом выходе вырабатывает импульс, который осуществляет ввод аргумента функции во входной регистр, знака функции - в триггер знака результата, константы, формируемой блоком выбора ре жима счетчика - в реверсивный счетчик, модуля показателя степени - в первый счетчик. Если после ввода аргумента старший разряд входного регистра окажется в нулевом состоянии, 20 устройство управления начнет вырабатывать серию импульсов на втором выходе. На каждый импульс содержимое входного регистра сдвигается влево на один. разря.1 а блок выбора режима счетчика осуществляет либо увеличение (0( 1 0)либо уменьшение (О ( О) содержимого. реверсивного счетчика на единицу, Как только после очередного сдвига старший разряд входного регистра окажется в единичном состоянии, устройство управления прекрашает вырабатывать серию импульсов на втором выходе и вырабатывает импульс на третьем выходе, Если после ввода аргумента в старшем разряде входного. регистра окажется единица, то устройство управления не вырабатывает серию импульсов на втором выходе, а Формирует импульс на третьем выходе. Этот 4 О сигнал осуществляет выборку иэ блока памяти табличного значения функции у и занесение его в выходной регистр, а также перезапись содержимого реверсивного счетчика во второй. Сформированный двоичный код, г старших разрядов которого расположены в первом счетчике, а щ младших - во втором, соответственно (хф К, т.е. равен числу сдвигов вправо содержимого выходного регистра. Для их осуществления устройство управления после сигнала на третьем выходе начинает вырабатывать серию импульсов на четвертом выходе. На каждый импульс содержимое выходного регистра сдвигается вправо на один разряд, а содержимое второго счетчика уменьшается на единицу. Каждый К-й импульс обнуляет содержимое второго счетчика, что вызывает появление сигнала на его выходе окончания счета на уменьшение. Этот сигнал уменьшает на единицу содержимое первого счет" чика и осуществляет перезапись содержимого реверсивно.о счетчика во второй. Содержимое первого счетчика станет равным нулю, когда устройство управления выдаст серию импульсов на четвертом выходе. В этом время на выходе окончания счета на уменьшение первого счетчика появится сигнал, который, поступая в устройство управления, прекратит выдачу импульсов на четвертом выходе и обеспечит выдачу сигнала конца операции на пятом выходе устройства управления.формула изобретенияУстройство для вычисления степенной функции, содержащее входной и выходной регистры, блок памяти, блок управления, о т л и ч а ю щ е е - с я тем, что, с целью снятия ограничений на область изменения аргумента для целочисленных (как положительных так и отрицательных) степеней при одновременном сокращении объема памяти, в него введены реверсивный счетчик,блок выбора режима счетчика, первый и второй вычитающие счетчики, блок формирования знака функции, триггер знака результата, элемент ИЛИ, причем вход модуля аргумента устройства подключен к информационному входу входного регистра, а вход знака аргумента устройства - к первому информационному входу блока формирования знака функции, второй информационный вход и выход которого соединены соответственно с входом модуля показателя степени устройства и информационным входом триггера знака результата, вход разрешения записи которого, объединенный с одноименными входами входного регистра, первого вычитающего счетчика и реверсивного счетчика, соединен с первым выходом блока управления, входы запуска и синхронизации которого подключены соответственно к входу "Пуск" и синхровходу устройства, а его первый, вто" рой и третий входы логических условий - соответственно к входу первого старшего разряда входного регистра, выходу первого вычитающего счетчика и выходу окончания счета реверсивного1624 л 45 иг.1 б 17 счетчика, инАорманионный выход которого соединен с информационным входом второго вычитающего счегчика,вход разрешения записи и выход которого подключены соответственно к выходу и первому входу элемента ИГИ,вход сдвига входного регистра и входуправления режимом блока выбора ре-жима счетчика соединены с вторым выходом блока управления, третий выходкоторого подключен к второму входуэлемента ИЛИ, входу разрешения выборки адреса блока памяти и входу разрешения записи выходного регистра,информационный вход которого подключен к выходу блока памя ги, а гходсдвига вправо и вы штаюпПп вход второго вычитающего счетчика соединеныс четвертым выходом блока управления,пятый выход которого является якходом сигнала Конец операгии, герный,второй и третий выходы блок выбора режима счетчика соединены с инАс 1 рма;ионным входом, входом вычитания и входом сложения реверсивного счетчика соответственно, информационный 5вход блока выбора режима счетчика и вход старших разрядов адреса блока памяти подключены к входу знака показателя степени устройства, вход модуля показателя степени которогосоединен с информационными вхопамипервого вычитающего счетчика и блока памяти, вхог, младших разрядов адреса последнего из которьх подключены к выходам старших разрядов, кроме первого, входного регистра, вычитаю - щий вход первого вычитающего счетчисоединен с вьходом второго вычитающего счетчика, выходы выходногорегистра и триггера знака результатаявляются выходами модуля и знака результата соответственно1624445 фиг. Р Редактор 10.Сере 90 Тираж ПодписноеГосударственного комитета по изобретениям и открытиям при113035, Москва, Ж, Раушская наб., д, 4/5 роизводственно-издательскщ комбинат "Патент", г. Ужгород, ул. Гагарина, 101 ЗакаВНИИПИ оставитель В, Гехред М,Дидык тин Корректор И.Муск

СмотретьЗаявка

4663066, 15.03.1989

ХАРЬКОВСКИЙ ИНСТИТУТ РАДИОЭЛЕКТРОНИКИ ИМ. АКАД. М. К. ЯНГЕЛЯ

ГУСЯТИН ВЛАДИМИР МИХАЙЛОВИЧ, ГОРБАЧЕВ ВАЛЕРИЙ АЛЕКСАНДРОВИЧ, РУДЕНКО ОЛЕГ ГРИГОРЬЕВИЧ, ЛИБЕРОЛЬ БОРИС ДАВЫДОВИЧ, ТИМЧЕНКО ГЕОРГИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 7/552

Метки: вычисления, степной, функции

Опубликовано: 30.01.1991

Код ссылки

<a href="https://patents.su/6-1624445-ustrojjstvo-dlya-vychisleniya-stepnojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления степной функции</a>

Предыдущий патент: Устройство для извлечения корня из суммы квадратов трех чисел

Следующий патент: Генератор случайного марковского процесса

Случайный патент: Способ кормления свиней