Демодулятор фазоманипулированных сигналов с компенсацией помех

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1545332

Авторы: Гусельников, Чесноков

Текст

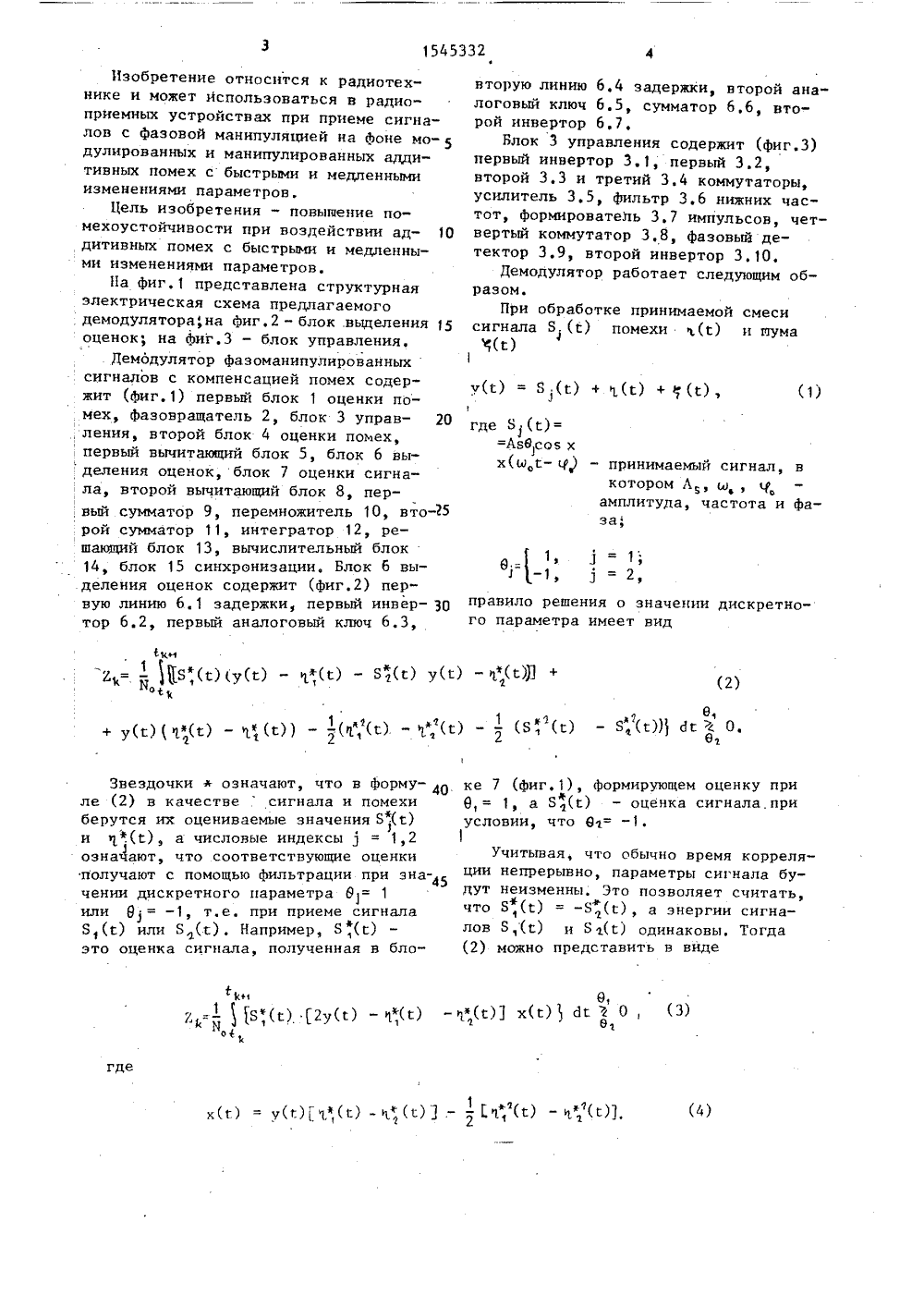

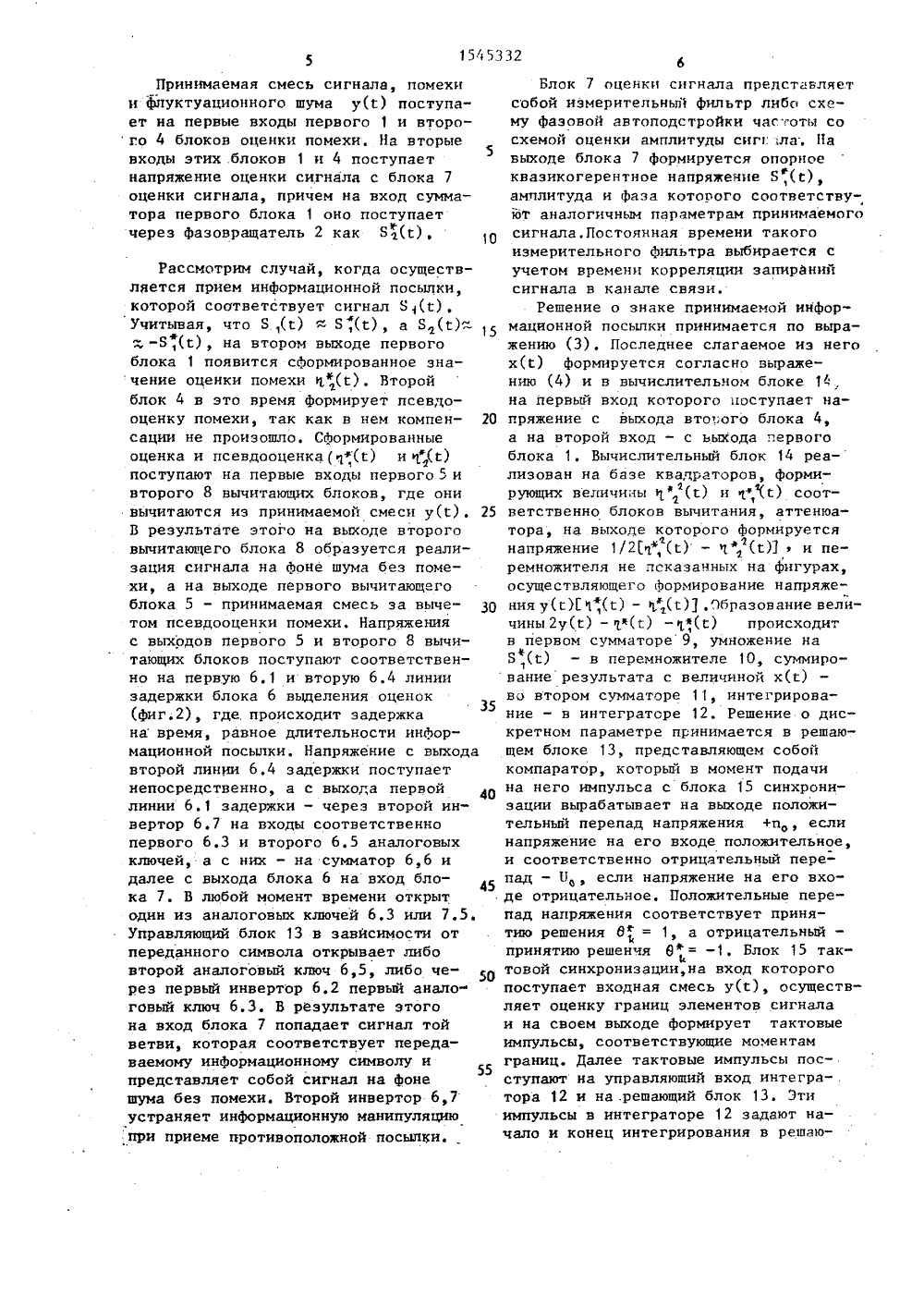

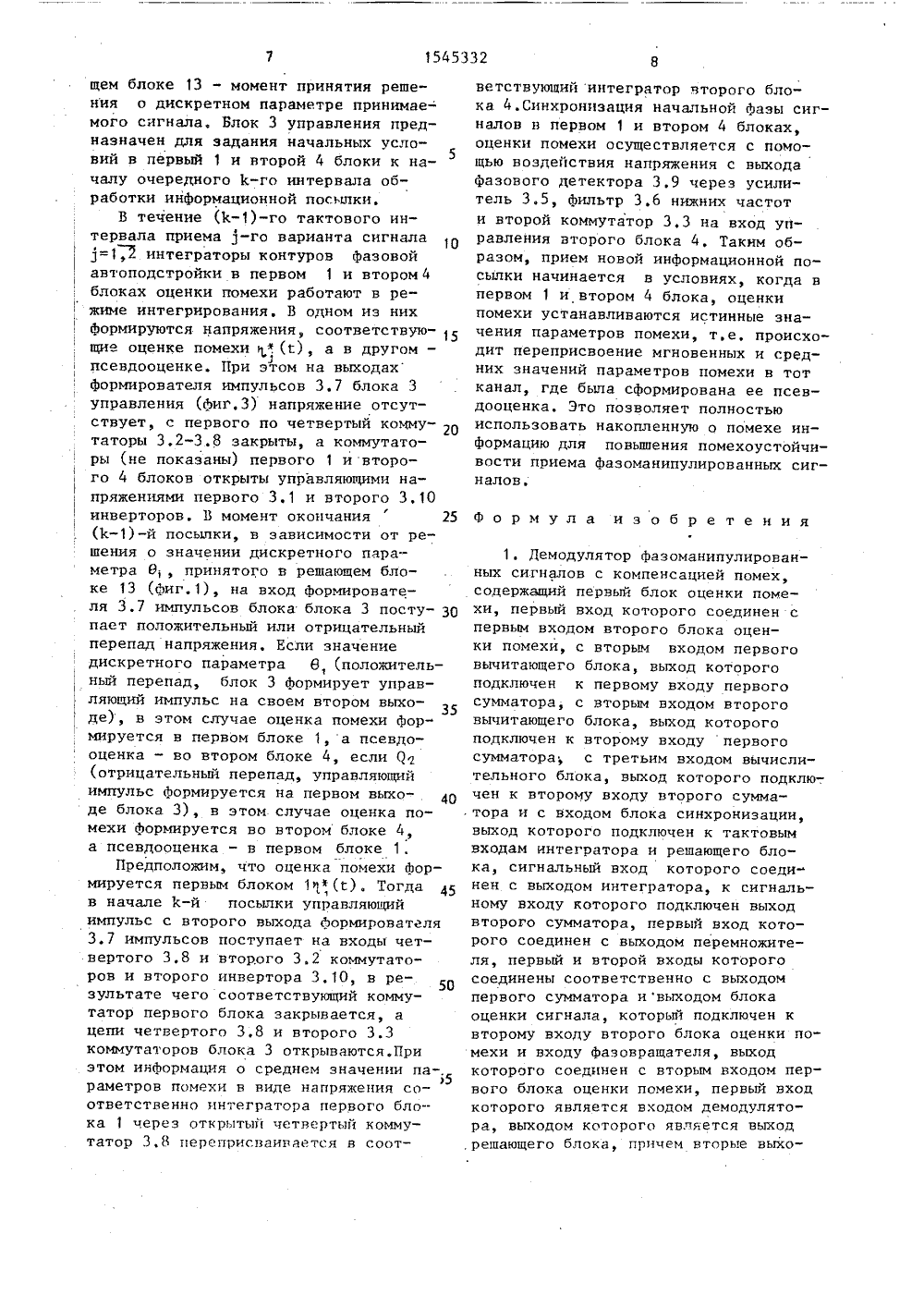

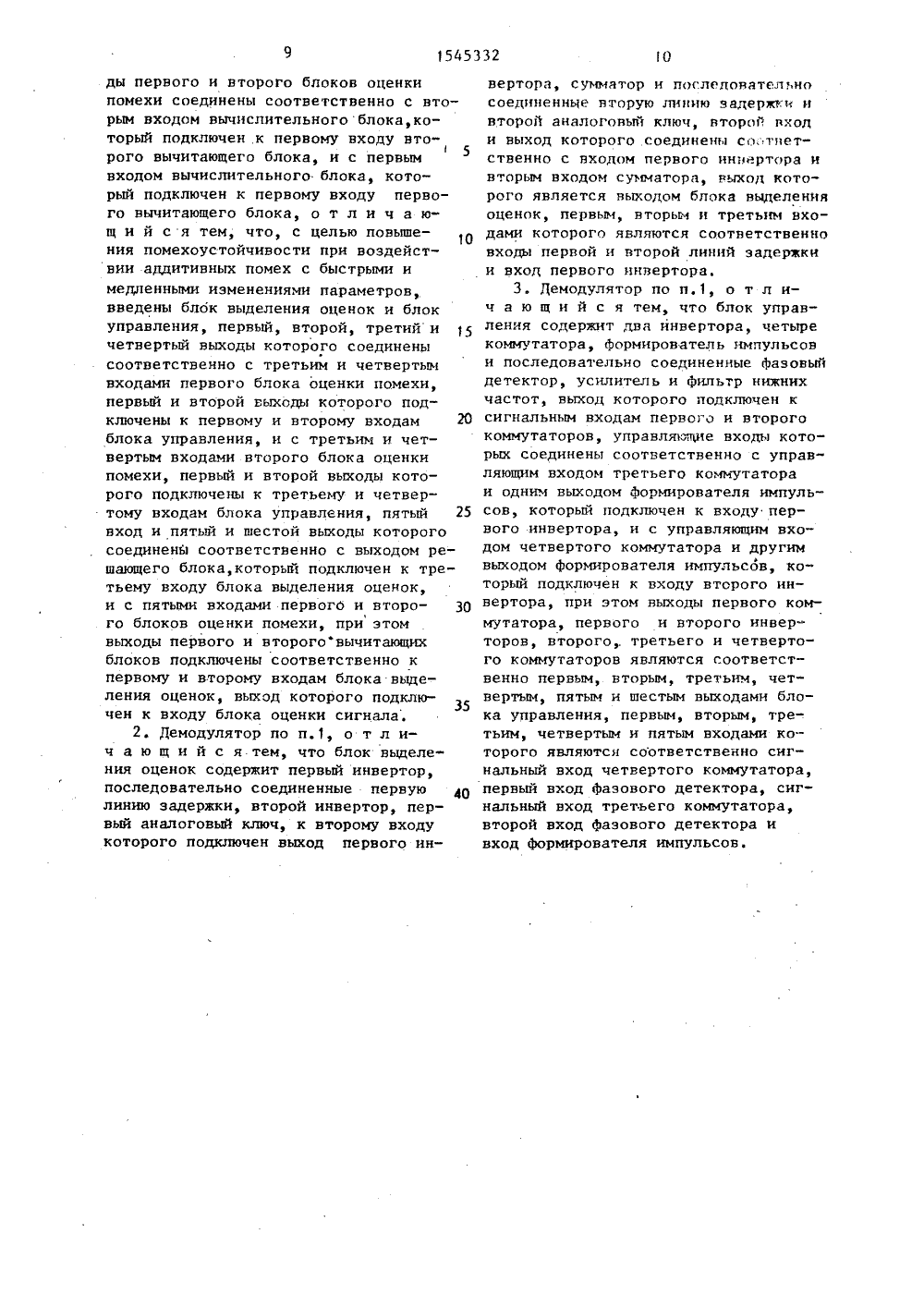

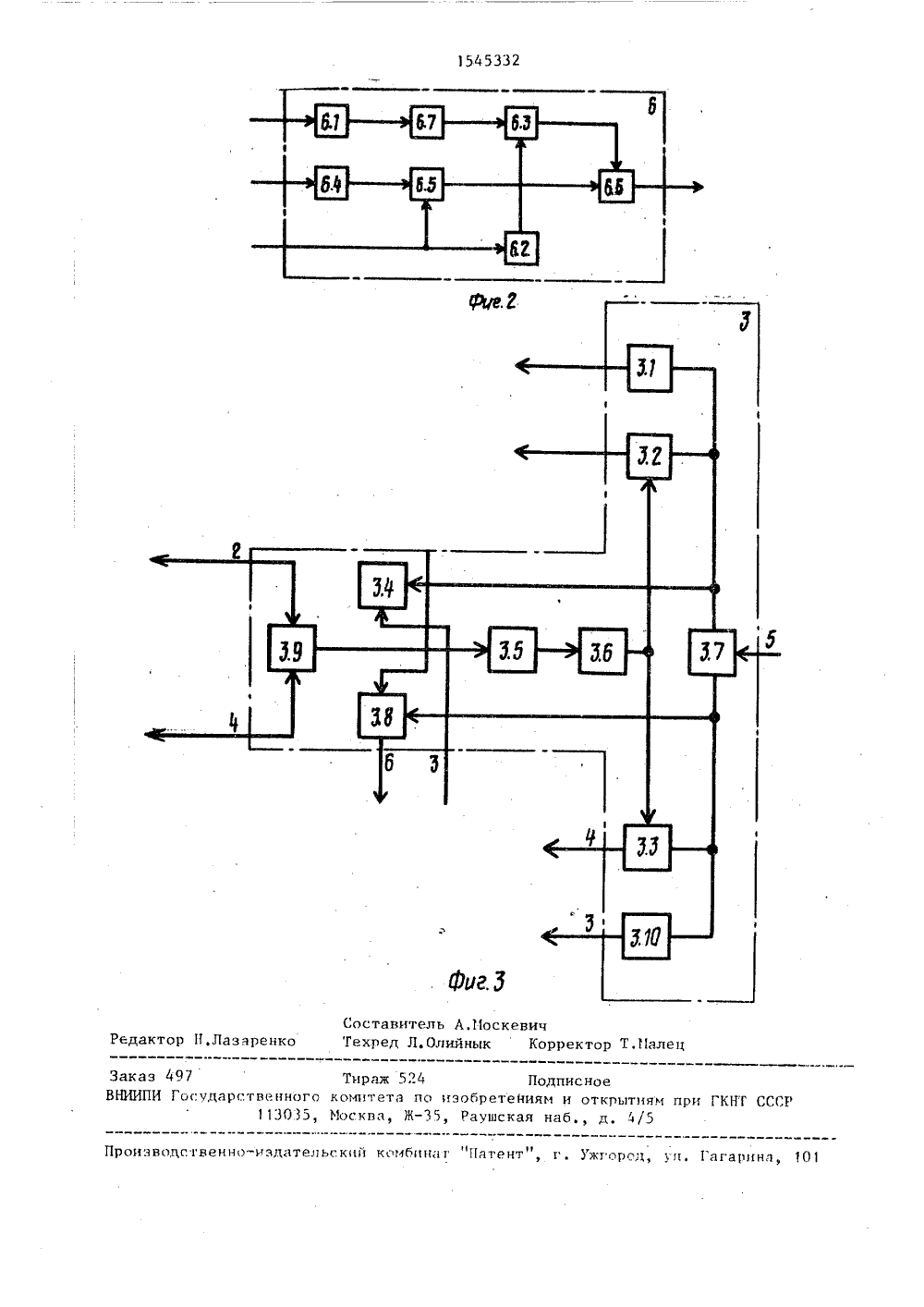

(51)5 Н ИЕ ИЗО СКОМУ ДЕТЕЛЬСТВ 19 4284743/24- 13.07.87 23.02,90. Бю 1.А.Чесноко 621,394.62( Сосулин Ю,Г нивания сто - 1.: Совет(21) (22) (46) (72) (53) (56) и оц лов. Р 7и Ю,А.Гусельников 88,8)Теория обна астических с Руженияигна 98 кое радио с 1 ЕХдиотехние и едлен оду по ения лок ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМПРИ ГКНТ СССР(54) ДЕИОДУЛЯТОР ФАЗОИАНИПУЛИРО НЫХ СИГНАЛОВ С КО 11 ПЕНСАПИЕЙ ПО (57) Изобретение относится к ра никеЦель изобретения - повыше помехоустойчивости при воздейст аддитивных помех с быстрыми и м ными изменениями параметров. Де лятор содержит блоки оценки 1 и мех, фазовращатель 2, блок упра (БУ) 3, вычитающие блоки 5 и 8, выделения (БВ) 6 оценок, блок о ки 7 сигнала, сумматоры 9 и 11,45332 А ени: : ,К 1 множитель 10, интегратор 12, решающийблок 13, вычслтельнь. блок 14 иблок синхронизации 15. Цель достигается введением БУ 3, предназначенногодля задания начальных условий в блокоценки 1 и 4 к началу очередного К-гоинтервала обработки информационнойпосылки, а также введением БВ 6, с помощью которого на вход блока оценки 7попадает сигнал той ветви, которая соответствует передаваемому информационному символу и представляет собойсигнал на фоне шума без помехи.В устр-ве осуществляется переприсвоение мгновенных и средних значений параметров помехи в тот канал, где была сформирована ее псевдооценка. Этопозволяет полностью использовать накопленную о помехе информацию для повышения помехоустойчивости приема фазоманипулированных сигналов, 2 з.п,ф-лы,3 ил.(4) Изобретение относится к радиотех" нике и может использоваться в радио- приемных устройствах при приеме сигналов с фазовой манипуляцией на фоне мо дулированных и манипулированных аддитивных помех с быстрыми и медленными изменениями параметров.11 ель изобретения - повышение помехоустойчивости при воздействии ад дитивных помех с быстрыми и медленными изменениями параметров.На фиг,1 представлена структурная электрическая схема предлагаемого демодулятора,на фиг,2 - блок выделения 15 оценок; на фиг.З - блок управления,. Демодулятор фазоманипулированных сигналов с компенсацией помех содержит (фиг,1) первый блок 1 оценки помех, фазовращатель 2, блок 3 управ,ления, второй блок 4 оценки помех, первый вычитающий блок 5, блок б вы деления оценок, блок 7 оценки сигнала, второй вычитающий блок 8, пер, вый сумматор 9, перемножитель 10, вто-с 5 рой сумматор 11, интегратор 12, решающий блок 13, вычислительный блок 14, блок 15 синхронизации. Блок б выделения оценок содержит (фиг.2) первую линию 6,1 задержки, первый инвер тор 6.2, первый аналоговый ключ 6.3,Звездочкиозначают, что в формуле (2) в качествесигнала и помехиберутся их оцениваемые значения Б (с)и )1+, а числовые индексы 1 = 1,2означают, что соответствующие оценкиполучают с помощью фильтрации при эна чении дискретного параметра 81= 1или В = -1, т,е. при приеме сигналаБ (с) или Б (с), Например, Б,(с)это оценка сигнала, полученная в бловторую линию 6.4 задержки, второй аналоговый ключ 6,5, сумматор 66, второй инвертор 6.7,Блок 3 управления содержит (фиг,З)первый инвертор 3,1, первый 3,2,второй 3.3 и третий 3.4 коммутаторы,усилитель 3.5, фильтр 3.6 нижних частот, формирователь 3,7 импульсов, четвертый коммутатор 3.8, фазовый детектор 3.9, второй инвертор 3,10.Демодулятор работает следующим образом.При обработке принимаемой смесисигнала Б.(с) помехи ъ(г.) и шумаправило решения о значении дискретного параметра имеет вид ке 7 (фиг.1), формирующем оценку при О, = 1, а Б (С) - оценка сигнала при условии, что 6 г= - 1.Учитывая, что обычно время корреляции непрерывно, параметры сигнала будут неизменны, Это позволяет считать,Ф Фчто Б,(С) = -Я(с), а энергии сигналов Я,(с) и Б 1(с) одинаковы, Тогда (2) можно представить в видеПринимаемая смесь сигнала, помехи и 4 луктуационного шума у(с) поступает на первые входы первого 1 и второ го 4 блоков оценки помехи, На вторые входы этих блоков 1 и 4 поступает напряжение оценки сигнала с блока 7 оценки сигнала, причем на вход сумматора первого блока 1 оно поступает через фазовращатель 2 как Бг(с),10 Рассмотрим случай, когда осуществляется прием информационной посылки, которой соответствует сигнал Б (с), Учитывая, что Б,(С) - Б а Б- 15 - -Б,(с), на втором выходе первого блока 1 появится сформированное значение оценки помехи "(с), Второй блок 4 в это время формирует псевдо- оценку помехи, так как в нем компен сации не произошло. Сформированные оценка и псевдооценка(1(с) и (й) поступают на первые входы первого 5 и второго 8 вычитающих блоков, где они вычитаются из принимаемой смеси у(с). 25 В результате этого на выходе второго вычитаюцего блока 8 образуется реализация сигнала на фоне шума без помехи, а на выходе первого вычитающего блока 5 - принимаемая смесь за выче том псевдооценки помехи. Напряжения с выходов первого 5 и второго 8 вычитающих блоков поступают соответственно на первую 6.1 и вторую 6,4 линии задержки блока б выделения оценок (фиг.2), где. происходит задержка35 на время, равное длительности информационной посылки. Напряжение с выхода второй линии 6.4 задержки поступает непосредственно, а с выхода первой линии 6.1 задержки - через второй инвертор 6.7 на входы соответственно первого 6,3 и второго 6.5 аналоговых ключей, а с них - на сумматор б,б и далее с выхода блока 6 на вход блока 7. В любой момент времени открыт один из аналоговых ключей 6.3 или 7,5. Управляющий блок 13 в зависимости от переданного символа открывает либо второй аналоговый ключ 6,5, либо через первый инвертор 6,2 первый аналоговый ключ 6.3. В результате этого на вход блока 7 попадает сигнал той ветви, которая соответствует передаваемому информационному символу и представляет собой сигнал на фоне шума без помехи. Второй инвертор 6,7 устраняет информационную манипуляцию при приеме противоположной посылки,Блок 7 оценки сигнала представляетсобой измерительный фильтр либо схему фаэовой автоподстройки час:"оты сосхемой оценки амплитуды сиг 1;ла, Иа выходе блока 7 формируется опорное квазикогерентное напряжение Б,(с), амплитуда и фаза которого соответствуют аналогичным параметрам принимаемогосигнала. Постоянная времени такогоизмерительного фильтра выбирается с учетом времени корреляции запиранийсигнала в канале связи.Решение о знаке принимаемой информационной посылки принимается по выражению (3), Последнее слагаемое из него х(С) формируется согласно выражению (4) и в вычислительном блоке 14 на первый вход которого поступает напряжение с выхода втж;ого блока 4, а на второй вход - с ьыхода первого блока 1. Вычислительный блок 14 реализован на базе квадраторов, формирующих величины "(с) и ф(с) соответственно блоков вычитания, аттенюатора, на выходе которого формируется напряжение 1/2 ф+,(с) - " (сЛи перемножителя не лсказанных на фигурах, осуществляющего формирование напряжения у(ЕЕ 1(С) - ." (с) 1,Образование величины 2 у(с) - (.) - ",(с) происходит в первом сумматоре 9, умножение на Б,(с) - в перемножителе 10, суммирование результата с величиной х(О во втором сумматоре 11, интегрирование - в интеграторе 12. Решение о дискретном параметре принимается в решающем блоке 13, представляющем собой компаратор, который в момент подачи на него импульса с блока 15 синхронизации вырабатывает на выходе положительный перепад напряжения +и , если напряжение на его входе положительное, и соответственно отрицательный перепад - Б , если напряжение на его входе отрицательное, Положительные перепад напряжения соответствует принятию решения 0" = 1, а отрицательный - принятию решенчя 6+ = -1. Блок 15 тактовой синхронизации,на вход которого поступает входная смесь у(с), осуществляет оценку границ элементов сигнала и на своем выходе формирует тактовые импульсы, соответствующие моментам границ. Далее тактовые импульсы пос-. ступают на управляюший вход интегратора 12 и на .решающий блок 13. Эти импульсы в интеграторе 12 задают начало и конец интегрирования в решающем блоке 13 - момент принятия решения о дискретном параметре принимае-мого сигнала. Блок 3 управления предназначен для задания начальных условии в первый 1 и второй 4 блоки к нан5чалу очередного к-го интервала обработки информационной посылки,В течение (к)-го тактового интервала приема 3-го варианта сигнала=1,. интеграторы контуров Фазовойавтоподстройки в первом 1 и втором 4блоках оценки помехи работают в режиме интегрирования, В одном из нихформируются напряжения, соответствующие оценке помехи ,(г.), а в другом -3псевдооценке. При этом на выходахформирователя импульсов 3.7 блока 3управления (Фиг.3) напряжение отсутствует, с первого по четвертый коммутаторы 3,2-3.8 закрыты, а коммутаторы (не показаны) первого 1 и второго 4 блоков открыты управляющими напряжениями первого 3,1 и второго 3,10инверторов. В момент окончания 25(1-1)-й посылки, в зависимости от решения о значении дискретного параметра 0;, принятого в решающем блоке 13 (Фиг,1), на вход Формирователя 3,7 импульсов блока блока 3 поступает положительный или отрицательныйперепад напряжения, Если значениедискретного параметра 6 (положитель 1ный перепад, блок 3 Формирует управляющий импульс на своем втором выхо 35де), в этом случае оценка помехи Формируется в первом блоке 1, а псевдооценка - во втором блоке 4, если Я(отрицательный перепад, управляющийимпульс формируется на первом выхо- . 40де блока 3), в этом. случае оценка помехи Формируется во втором блоке 4,а псевдооценка - в первом блоке 1.Предположим, что оценка помехи формируется первым блоком 1(С), Тогда 45в начале 1-й посылки управляющийимпульс с второго выхода Формирователя3.7 импульсов поступает на входы четвертого 3,8 и второго 3.2 коммутаторов и второго инвертора 3,10, в результате чего соответствующий коммутатор первого блока закрывается, ацепи четвертого 3,8 и второго 3.3коммутаторов блока 3 открываются.Приэтом информация о среднем значении па-.)5раметров помехи в виде напряжения соответственно интегратора первого блока 1 через открытый четвертый коммутатор 3,8 переприсваивается в соответствующий интегратор второго блока. 4.Синхронизация начальной Фазы сигналов в первом 1 и втором 4 блоках,оценки помехи осуществляется с помощью воздействия напряжения с выходафазового детектора 3.9 через усилитель 3,5, фильтр 3.б нижних частоти второй коммутатор 3.3 на вход управления второго блока 4, Таким образом, прием новой информационной посылки начинается в условиях, когда впервом 1 и втором 4 блока, оценкипомехи устанавливаются истинные значения параметров помехи, т,е, происходит переприсвоение мгновенных и средних значений параметров помехи в тотканал, где была сформирована ее псевдооценка. Это позволяет полностьюиспользовать накопленную о помехе информацию для повышения помехоустойчивости приема фазоманипулированных сигналов,Формула изобретения1, Демодулятор фаэоманипулированных сигналов с компенсацией помех, содержащий первый блок оценки помехи, первый вход которого соединен с первым входом второго блока оценки помехи, с вторым входом первого вычитающего блока, выход которого подключен к первому входу первого сумматора, с вторым входом второго вычитающего блока, выход которогоподключен к второму входу первогосумматора, с третьим входом вычислительного блока, выход которого нодключен к второму входу второго сумматора и с входом блока синхронизации,выход которого подключен к тактовымвходам интегратора и решающего блока, сигнальный вход которого соеди нен с выходом интегратора, к сигнальному входу которого подключен выход второго сумматора, первый вход которого соединен с выходом перемножителя, первый и второй входы которого соединены соответственно с выходом первого сумматора и выходом блока оценки сигнала, который подключен к второму входу второго блока оценки помехи и входу фазовращателя, выход которого соединен с вторым входом первого блока оценки помехи, первый вход которого является входом демодулятора, выходом которого является выход решающего блока, прнцем вторье выхо 1545332ды первого и второго блоков оценки помехи соединены соответственно с вторым входом вычислительного блока,который подключен,к первому входу второго вычитающего блока, и с первым входом вычислительного блока, который подключен к первому входу первого вычитающего блока, о т л и ч а ющ и й с я тем, что, с целью повышения помехоустойчивости при воздействии аддитивных помех с быстрыми имедленными изменениями параметров, введены блок выделения оценок и блок управления, первый, второй, третий и 15 четвертый выходы которого соединены соответственно с третьим и четвертым входами первого блока оценки помехи, первый и второй выходы которого подключены к первому и второму входам 20 блока управления, и с третьим и четвертым входами второго блока оценки помехи, первый и второй выходы которого подключены к третьему и четвертому входам блока управления, пятый 25 вход и пятый и шестой выходы которого соединены соответственно с выходом решающего блока,которьп подключен к третьему входу блока выделения оценок, и с пятыми входами первого и второ го блоков оценки помехи, при этом выходы первого и второговычитающих блоков подключены соответственно к первому и второму входам блока выделения оценок, выход которого подключен к входу блока оценки сигнала,2. Демодулятор по п.1, о т л ич а ю щ и й с я тем, что блок выделения оценок содержит первый инвертор, последовательно соединенные первую линию задержки, второй инвертор, первый аналоговый ключ, к второму входу которого подключен выход первого инвертора, сумматор и послеловател;носоединенные вторую линию задержки нвторой аналоговый ключ, второй входи выход которого соединены со,.тнетственно с входом первого иннертора ивторым входом сумматора, выход которого является выходом блока выделенияоценок, первым, вторьсч и третьим входами которого являются соответственновходы первой и второй линий задержкии вход первого инвертора,3. Демодулятор по и.1, о т л ич а ю щ и й с я тем, что блок управления содержит два инвертора, четырекоммутатора, Формирователь импульсови последовательно соединенные Фазовыйдетектор, усилитель и Фильтр нижнихчастот, выход которого подключен ксигнальным входам первого и второгокоммутаторов, управляющие входы которых соединены соответственно с управляющим входом третьего коммутатораи одним выходом Формирователя импульсов, который подключен к входу первого инвертора, и с управляющим входом четвертого коммутатора и другимвыходом Формирователя импульсов, который подключен к входу второго инвертора, при этом выходы первого коммутатора, первого и второго инверторов, второго,. третьего и четвертого коммутаторов являются соответственно первым, вторым, третьим, четвертым, пятым и шестым выходами блока управления, первым, вторым, третьим, четвертым и пятым входами которого являются соответственно сигнальный вход четвертого коммутатора,первый вход Фазового детектора, сигнальный вход третьего коммутатора,второй вход Фазового детектора ивход формирователя импульсов.54 Подп а по изобретениям Ж, Раушская на исноеоткрытиям б д, 4/5

СмотретьЗаявка

4284743, 13.07.1987

ВОЕННАЯ КРАСНОЗНАМЕННАЯ АКАДЕМИЯ СВЯЗИ ИМ. С. М. БУДЕННОГО

ЧЕСНОКОВ МИХАИЛ НИКОЛАЕВИЧ, ГУСЕЛЬНИКОВ ЮРИЙ АЛЕКСЕЕВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, компенсацией, помех, сигналов, фазоманипулированных

Опубликовано: 23.02.1990

Код ссылки

<a href="https://patents.su/6-1545332-demodulyator-fazomanipulirovannykh-signalov-s-kompensaciejj-pomekh.html" target="_blank" rel="follow" title="База патентов СССР">Демодулятор фазоманипулированных сигналов с компенсацией помех</a>

Предыдущий патент: Волоконно-оптическая измерительная система

Следующий патент: Электродинамический громкоговоритель

Случайный патент: Воздухонагреватель