Цифровой демодулятор сигналов относительной фазовой манипуляции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

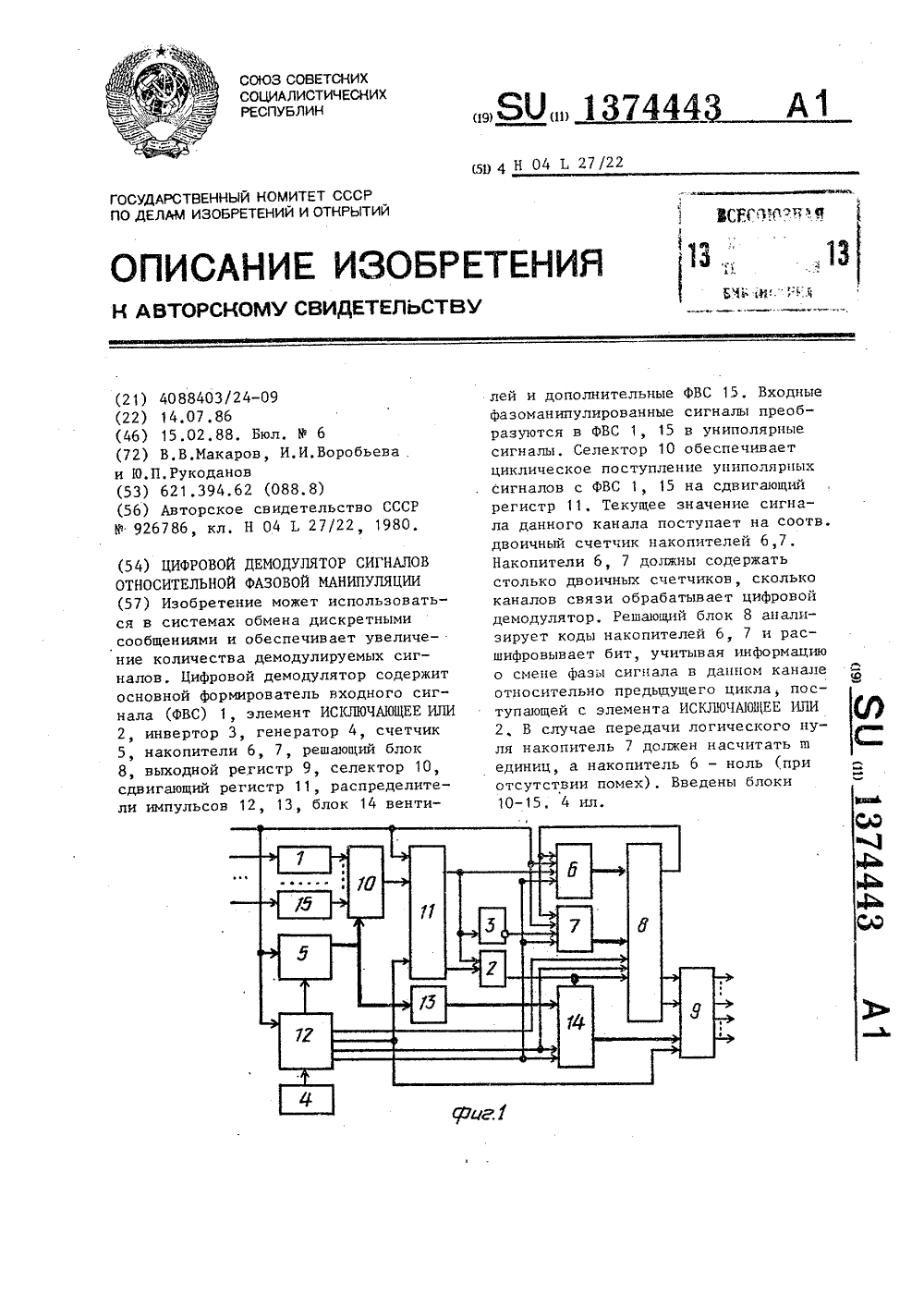

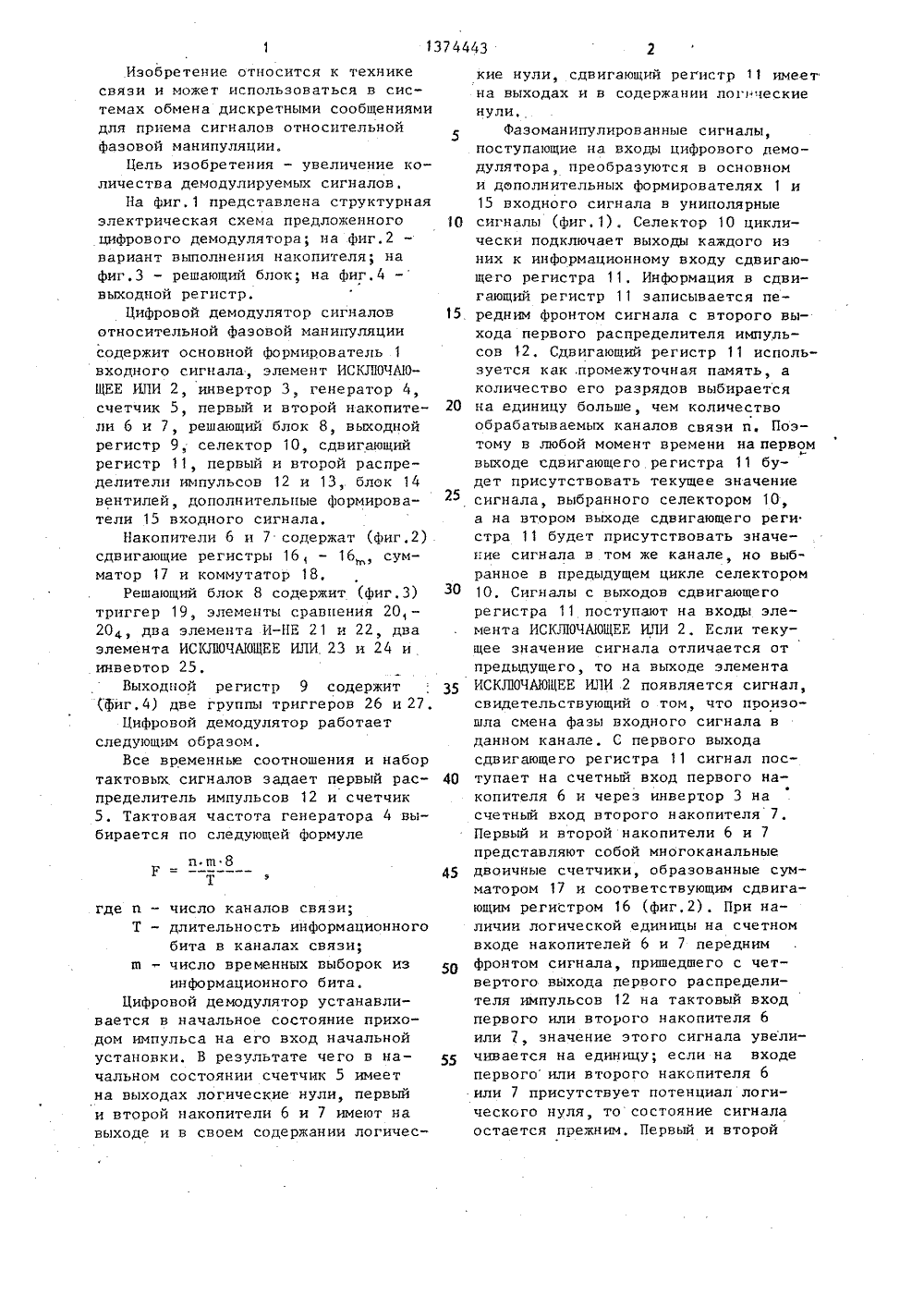

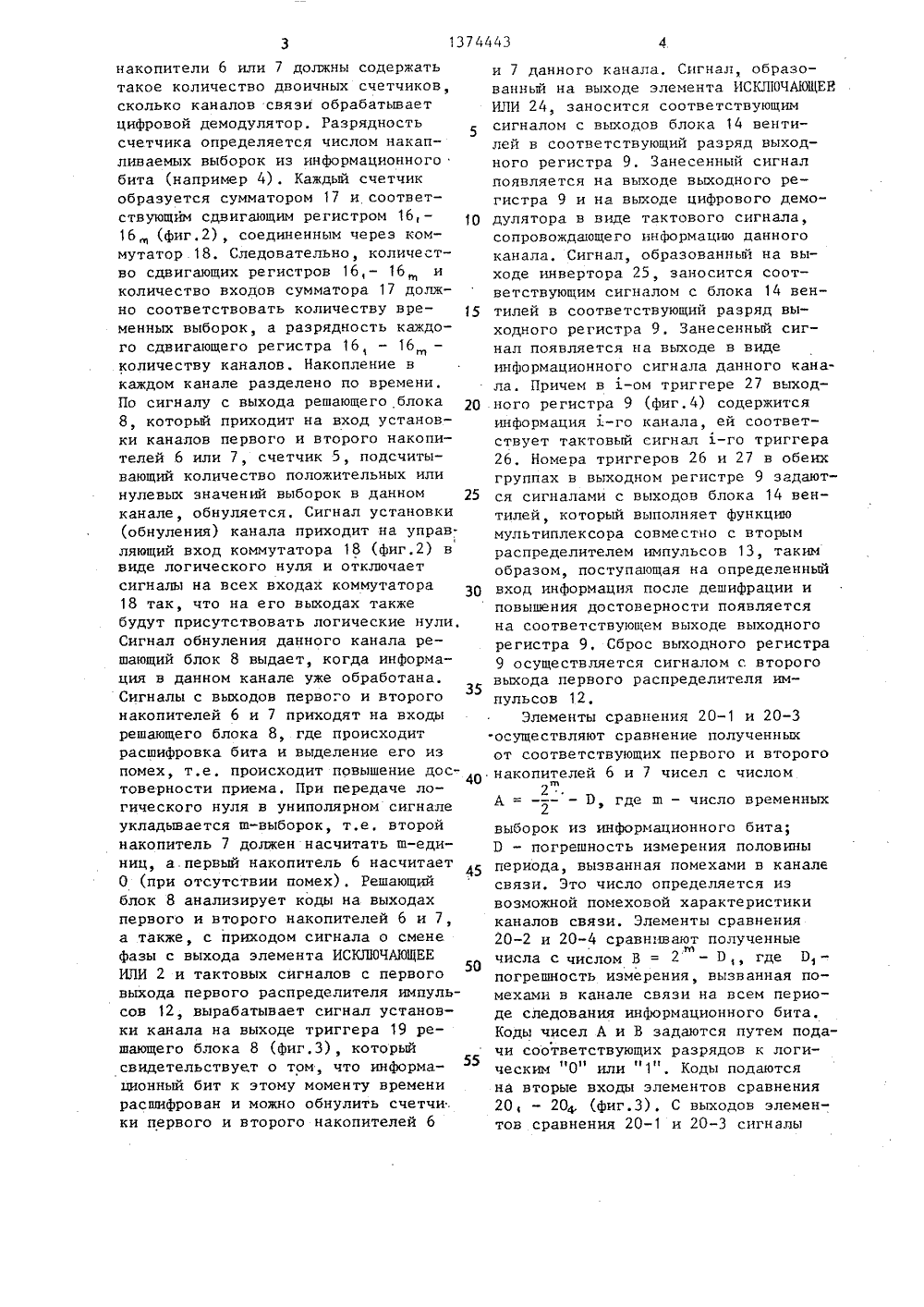

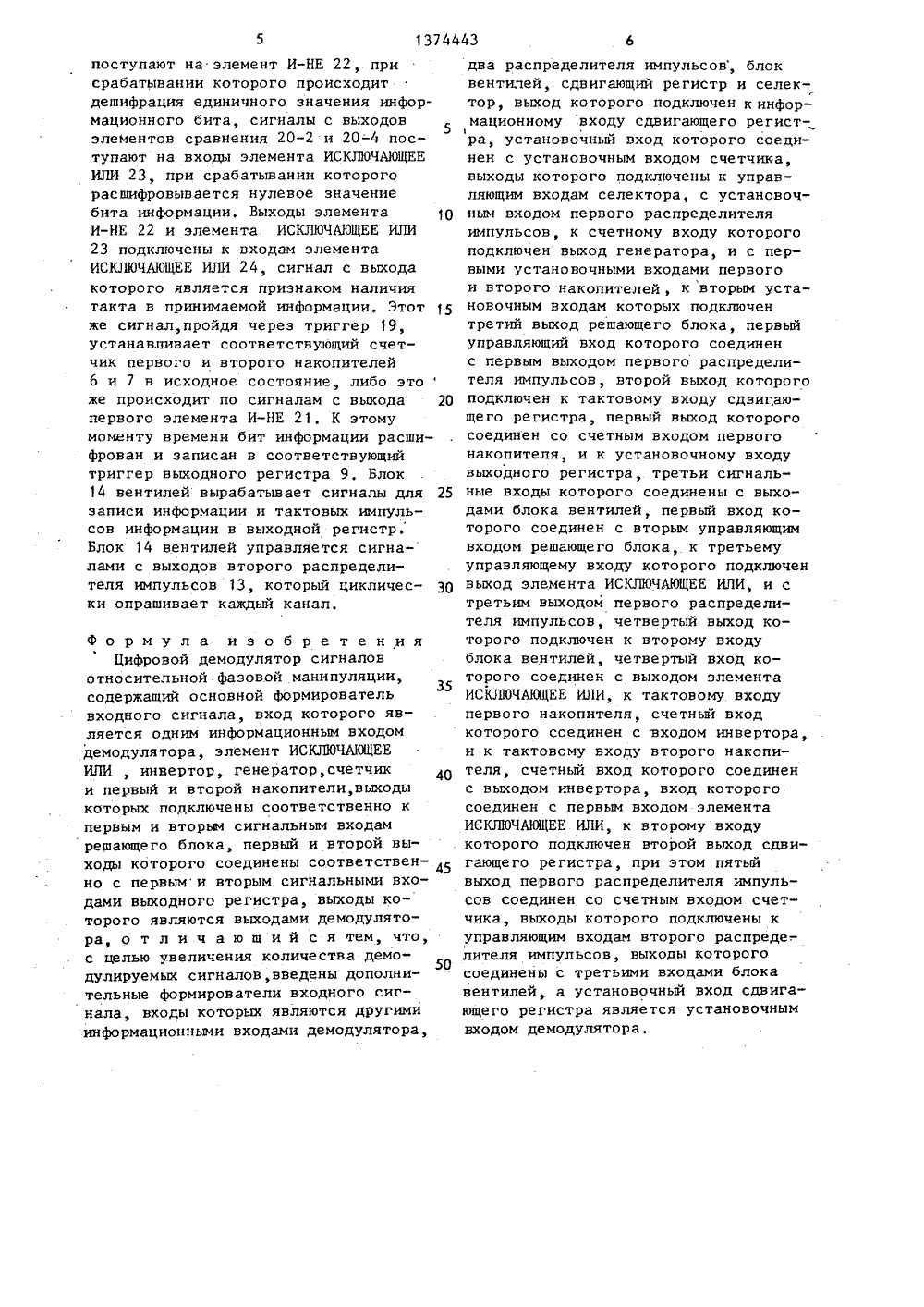

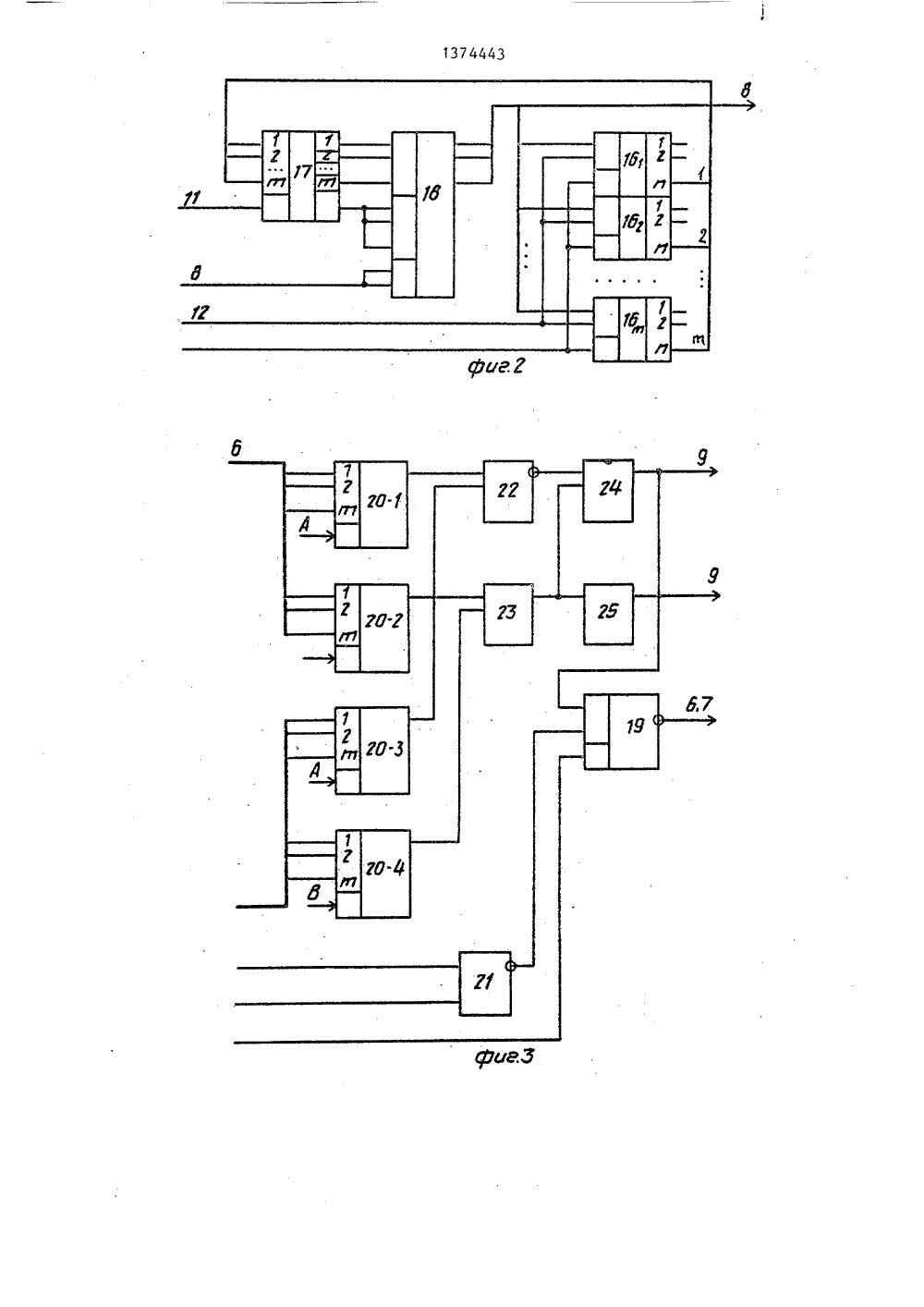

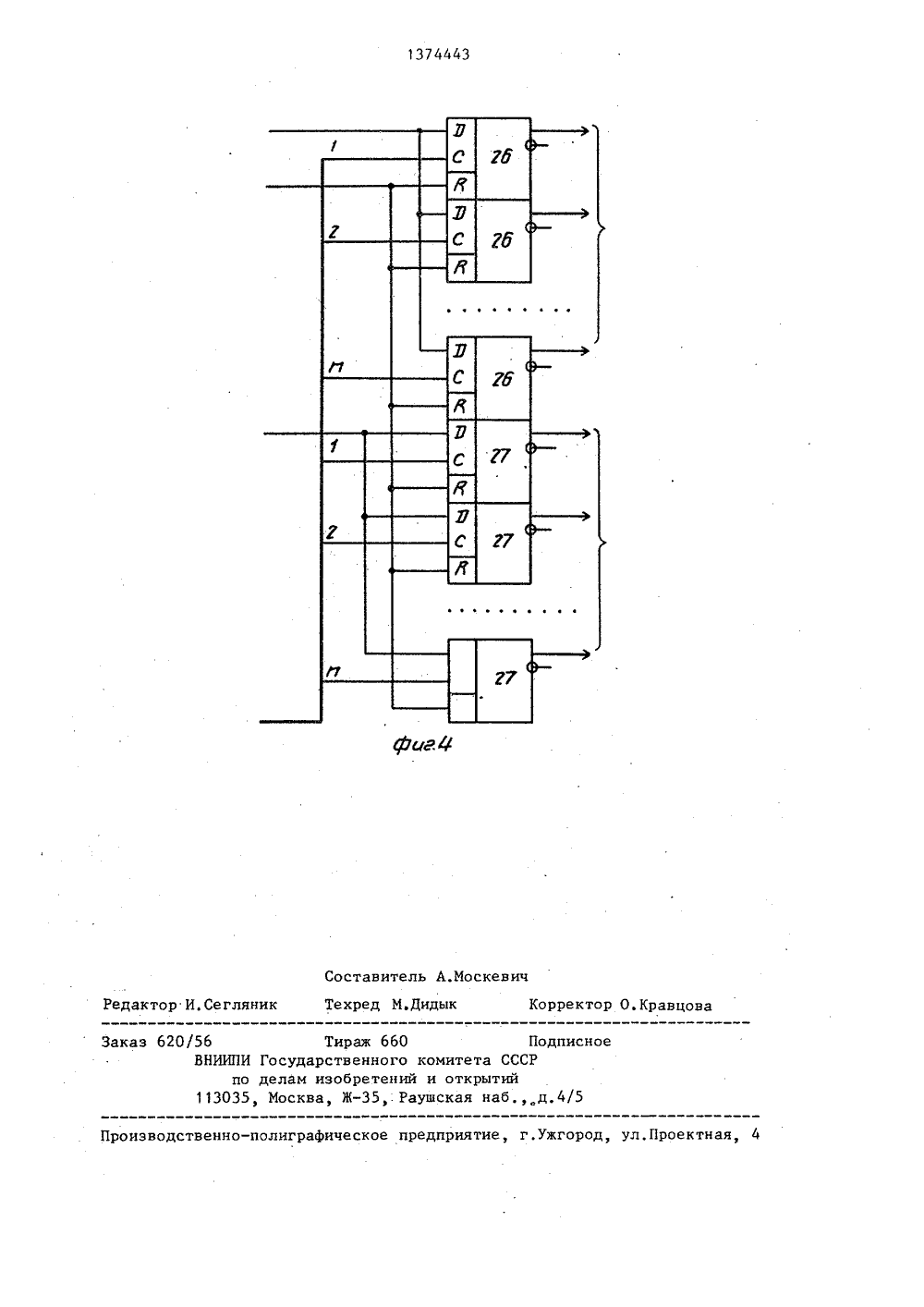

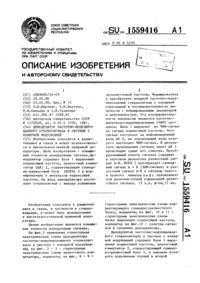

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСНИРЕСПУБЛИН О 1 З 7444 З т. 27/ ОСУДАРСТВЕННЫЙ НОМИТ ПО ДЕЛАМ ИЗОБРЕТЕНИЙ И СССРНРЫТИЙ ОПИСАНИЕ ИЗОБРЕТЕНИЯН АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) Авторское свидет9 926786, кл, Н 04 Ь оробьева ьство СССР /22, 1980,о т(54) ЦИФРОВОЙ ДЕМОДУЛЯТОР СИГНАЛОВОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МАНИПУЛЯЦИИ(57) Изобретение может использоваться в системах обмена дискретнымисообщениями и обеспечивает увеличе -ние количества демодулируемых сигналов, Цифровой демодулятор содержитосновной формирователь входного сигнала (ФВС) 1, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ2, инвертор 3, генератор 4, счетчик5, накопители 6, 7, решающий блок8, выходной регистр 9, селектор 10,сдвигающий регистр 11, распределители импульсов 12, 13, блок 14 вентилей и дополнительные ФВС 15, Входные фазоманипулированные сигналы преобразуются в ФВС 1, 15 в униполярные сигналы. Селектор 10 обеспечивает циклическое поступление униполярных сигналов с ФВС 1, 15 на сдвигающий регистр 11, Текущее значение сигнала данного канала поступает на соотв. двоичный счетчик накопителей 6,7, Накопители б, 7 должны содержать столько двоичных счетчиков, сколько каналов связи обрабатывает цифровой демодулятор. Решающии блок 8 анализирует коды накопителей б, 7 и расшифровывает бит, учитывая информацию о смене фазы сигнала в данном каналетносительно предыдущего цикла, посупающей с элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2, В случае передачи логического нуля накопитель 7 должен насчитать ш единиц, а накопитель б - ноль (при отсутствии помех). Введены блоки 10-15. 4 ил.п ш8РТ9 50 Изобретение относится к техникесвязи и может использоваться в системах обмена дискретными сообщениямидля приема сигналов относительнойфазовой манипуляции.Цель изобретения - увеличение количества демодулируемых сигналов,На фиг.1 представлена структурнаяэлектрическая схема предложенногоцифрового демодулятора; на фиг,2вариант выполнения накопителя; нафиг.З - решающий блок; на фиг,4 -выходной регистр.Цифровой демодулятор сигналовотносительной фаэовой манипуляциисодержит основной формирователь 1входного сигнала, элемент ИСКЛЮЧЖОЩЕЕ ИЛИ 2, инвертор 3, генератор 4,счетчик 5, первый и второй накопители 6 и 7, решающий блок 8, выходнойрегистр 9, селектор 10, сдвигающийрегистр 11, первый и второй распределители импульсов 12 и 13, блок 14вентилей, дополнительные формирователи 15 входного сигнала.Накопители 6 и 7 содержат (фиг,2)сдвигающие регистры 16, - 16, сумматор 17 и коммутатор 18,Решающий блок 8 содержит (фиг.З)триггер 19, элементы сравнения 20, -204, два элемента И-НЕ 21 и 22, дваэлемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 и 24 иинвертор 25,Выходной регистр 9 содержит(фиг,4) две группы триггеров 26 и 27,Цифровой демодулятор работаетследующим образом,Все временные соотношения и набортактовых сигналов задает первый распределитель импульсов 12 и счетчик5. Тактовая частота генератора 4 выбирается по следующей формуле где и - число каналов связи;Т - длительность информационногобита в каналах связи;ш - число временных выборок изинформационного бита,Цифровой демодулятор устанавливается в начальное состояние приходом импульса на его вход начальной установки. В результате чего в начальном состоянии счетчик 5 имеет на выходах логические нули, первый и второй накопители 6 и 7 имеют на выходе и в своем содержании логичес 5 10 15 20 25 30 35 40 45 кие нули, сдвигающий регистр 11 имеетна выходах и в содержании логическиенули,Фазоманипулированные сигналы,поступающие на входы цифрового демодулятора, преобразуются в основноми деполнительных формирователях 1 и15 входного сигнала в униполярныесигналы (фиг.1), Селектор 10 циклически подключает выходы каждого изних к информационному входу сдвигающего регистра 11, Информация в сдвигающий регистр 11 записывается передним фронтом сигнала с второго выхода первого распределителя импульсов 12, Сдвигающий регистр 11 используется как,промежуточная память, аколичество его разрядов выбираетсяна единицу больше, чем количествообрабатываемых каналов связи и, Поэтому в любой момент времени на первомФвыходе сдвигающего регистра 11 будет присутствовать текущее значениесигнала, выбранного селектором 10,а на втором выходе сдвигающего регистра 11 будет присутствовать значение сигнала в том же канале, но выбранное в предыдущем цикле селектором10. Сигналы с выходов сдвигающегорегистра 11 поступают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 2. Если текущее значение сигнала отличается отпредыдущего, то на выходе элементаИСКЛЮЧАЮЩЕЕ ИЛИ 2 появляется сигнал,свидетельствующий о том, что произошла смена фазы входного сигнала вданном канале, С первого выходасдвигающего регистра 11 сигнал поступает на счетный вход первого накопителя 6 и через инвертор 3 насчетный вход второго накопителя 7,Первый и второй накопители 6 и 7представляют собой многоканальныедвоичные счетчики, образованные сумматором 17 и соответствующим сдвигающим регистром 16 (фиг,2). При наличин логическои единицы на счетномвходе накопителей 6 и 7 переднимфронтом сигнала, пришедшего с четвертого выхода первого распределителя импульсов 12 на тактовый вход первого или второго накопителя 6 или 7, значение этого сигнала увеличивается на единицу; если на входе первогоили второго накопителя 6 или 7 присутствует потенциал логического нуля, то состояние сигналаостается прежним. Первый и второй45 50 55 накопители 6 или 7 должны содержатьтакое количество двоичных счетчиков,сколько каналов связи обрабатываетцифровой демодулятор, Разрядностьсчетчика определяется числом накапливаемых выборок из информационногобита (например 4). Каждый счетчикобразуется сумматором 17 и соответствующим сдвигающим регистром 16 -16 (фиг.2), соединенным через коммутатор 18. Следовательно, количество сдвигающих регистров 16, - 16 иколичество входов сумматора 17 должно соответствовать количеству временных выборок, а разрядность каждого сдвигающего регистра 16, - 16количеству каналов, Накопление вкаждом канале разделено по времени,По сигналу с выхода решающего блока8, который приходит на вход установки каналов первого и второго накопителей 6 или 7, счетчик 5, подсчитывающий количество положительных илинулевых значений выборок в данномканале, обнуляетсяСигнал установки(обнуления) канала приходит на управляющий вход коммутатора 18 (фиг.2) ввиде логического нуля и отключаетсигналы на всех входах коммутатора18 так, что на его выходах такжебудут присутствовать логические нули,Сигнал обнуления данного канала решающий блок 8 выдает, когда информация в данном канале уже обработана.Сигналы с выходов перво."о и второгонакопителей 6 и 7 приходят на входырешающего блока 8, где происходитрасшифровка бита и выделение его изпомех, т.е. происходит повышение достоверности приема, При передаче логического нуля в униполярном сигналеукладывается ш-выборок, т,евторойнакопитель 7 должен насчитать ш-единиц, а первый накопитель 6 насчитает0 (при отсутствии помех), Решающийблок 8 анализирует коды на выходахпервого и второго накопителей 6 и 7,а также, с приходом сигнала о сменефазы с выхода элемента ИСКЛЮЧАЮЩЕЕИЛИ 2 и тактовых сигналов с первоговыхода первого распределителя импульсов 12, вырабатывает сигнал установки канала на выходе триггера 19 решающего блока 8 (фиг,З), которыйсвидетельствует о том, что информационный бит к этому моменту временирасшифрован и можно обнулить счетчики первого и второго накопителей 6 и 7 данного канала, Сигнал, образованный на выходе элемента ИСКЛЮЧАЮЩЕЕИЛИ 24, заносится соответствующимсигналом с выходов блока 14 вентилей в соответствующий разряд выходного регистра 9. Занесенный сигналпоявляется на выходе выходного регистра 9 и на выходе цифрового демо 10 дулятора в виде тактового сигнала,сопровождающего информацпо данногоканала. Сигнал, образованный на выходе инвертора 25, заносится соответствующим сигналом с блока 14 вен 15 тилей в соответствующий разряд выходного регистра 9, Занесенный сигнал появляется на выходе в видеинформационного сигнала данного канала. Причем в- ом триггере 27 выход 20 ного регистра 9 (Фиг,4) содержитсяинформация -го канала, ей соответствует тактовый сигнал -го триггера26, Номера триггеров 26 и 27 в обеихгруппах в выходном регистре 9 задают 25 ся сигналами с выходов блока 14 вентилей, который выполняет функциюмультиплексора совместно с вторымраспределителем импульсов 13, такимобразом, поступающая на определенный30 вход информация после дешифрации иповышения достоверности появляетсяна соответствующем выходе выходногорегистра 9, Сброс выходного регистра9 осуществляется сигналом с. второго35 хда первго расрд импульсов 12,Элементы сравнения 20-1 и 20-3.осуществляют сравнение полученныхот соответствующих первого и второго40 накопителей 6 и 7 чисел с числом2А = --- П где ш - число временных2 фвыборок из информационного бита; П - погрешность измерения половиныпериода, вызванная помехами в каналесвязи, Это число определяется извозможной помеховой характеристикиканалов связи. Элементы сравнения20-2 и 20-4 сравнивают полученныечисла с числом В = 2 - П , где О, -погрешность измерения, вызванная помехами в канале связи на всем периоде следования информационного бита,Коды чисел А и В задаются путем подачи соответствующих разрядов к логическим "0" или "1", Коды подаютсяна вторые входы элементов сравнения20, - 204, (фиг.З), С выходов элементов сравнения 20-1 и 20-3 сигналы1374443поступают на элемент И-НЕ 22, при срабатывании которого происходит дешифрация единичного значения информационного бита, сигналы с выходов элементов сравнения 20-2 и 20-4 поступают на входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23, при срабатывании которого расшифровывается нулевое значение бита информации, Выходы элемента И-НЕ 22 и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23 подключены к входам элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24, сигнал с выхода которого является признаком наличия такта в принимаемой информации. Этот же сигнал, пройдя через триггер 19, устанавливает соответствующий счетчик первого и второго накопителей 6 и 7 в исходное состояние, либо этоже происходит по сигналам с выхода 20 первого элемента И-НЕ 21, К этому моменту времени бит информации расшифрован и записан в соответствующий триггер выходного регистра 9, Блок 14 вентилей вырабатывает сигналы для 25 записи информации и тактовых импульсов информации в выходной регистр. Блок 14 вентилей управляется сигналами с выходов второго распределителя импульсов 13, который цикличес ки опрашивает каждый канал.Формула и з о б р е т е н и яцифровой демодулятор сигналов относительной фазовой манипуляции,35 содержащий основной формирователь входного сигнала, вход которого является одним информационным входом демодулятора, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ , инвертор, генератор, счетчик и первый и второй накопители, выходы которых подключены соответственно к первым и вторым сигнальным входам решающего блока, первый и второй выходы которого соединены соответствен но с первыми вторым сигнальными входами выходного регистра, выходы которого являются выходами демодулятора, о т л и ч а ю щ и й с я тем, что, с целью увеличения количества демодулируемых сигналов, введены дополнительные формирователи входного сигнала, входы которых являются другими информационными входами демодулятора, 13744431374443 Составитель А.Москевичдактор И.Сегляник Техред М.Дидык Корректор О. Кравцо писно Производственно-полиграфическое предприятие, г.ужгород, ул,Проектна Заказ 620/56 Тир ВНИИПИ Государств по делам изоб 113035, Москва, Жаж 660 Поднного комитета СССРетений и открытий35,. Раушская наб ,.д,4/5

СмотретьЗаявка

4088403, 14.07.1986

ПРЕДПРИЯТИЕ ПЯ А-3706

МАКАРОВ ВЛАДИМИР ВАСИЛЬЕВИЧ, ВОРОБЬЕВА ИРИНА ИВАНОВНА, РУКОДАНОВ ЮРИЙ ПЕТРОВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, манипуляции, относительной, сигналов, фазовой, цифровой

Опубликовано: 15.02.1988

Код ссылки

<a href="https://patents.su/6-1374443-cifrovojj-demodulyator-signalov-otnositelnojj-fazovojj-manipulyacii.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой демодулятор сигналов относительной фазовой манипуляции</a>

Предыдущий патент: Устройство для приема частотно-манипулированных сигналов

Следующий патент: Устройство для приема дискретных сигналов

Случайный патент: Приспособление для очистки чешуи и разделки рыбы