Многофункциональный логический модуль

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

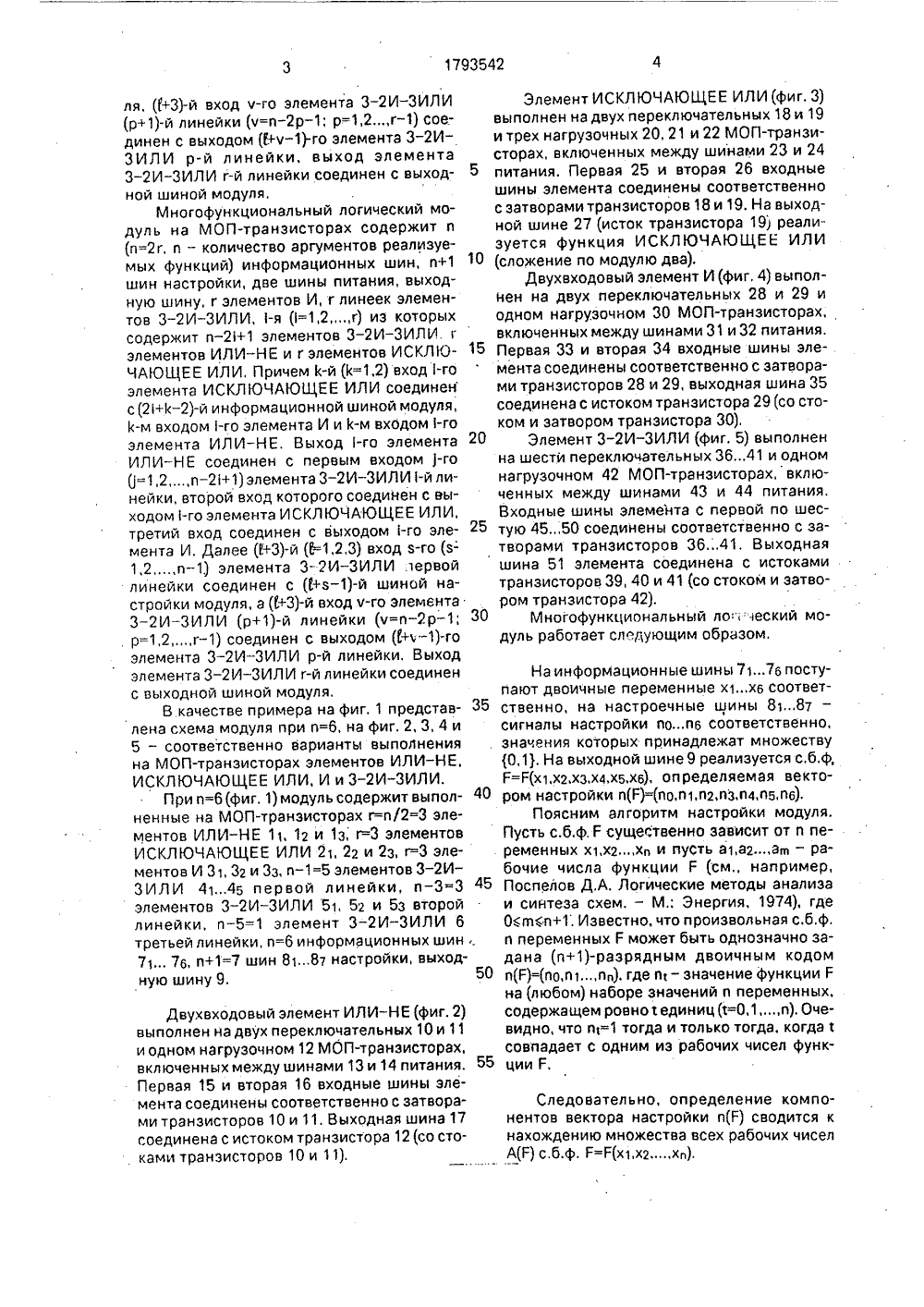

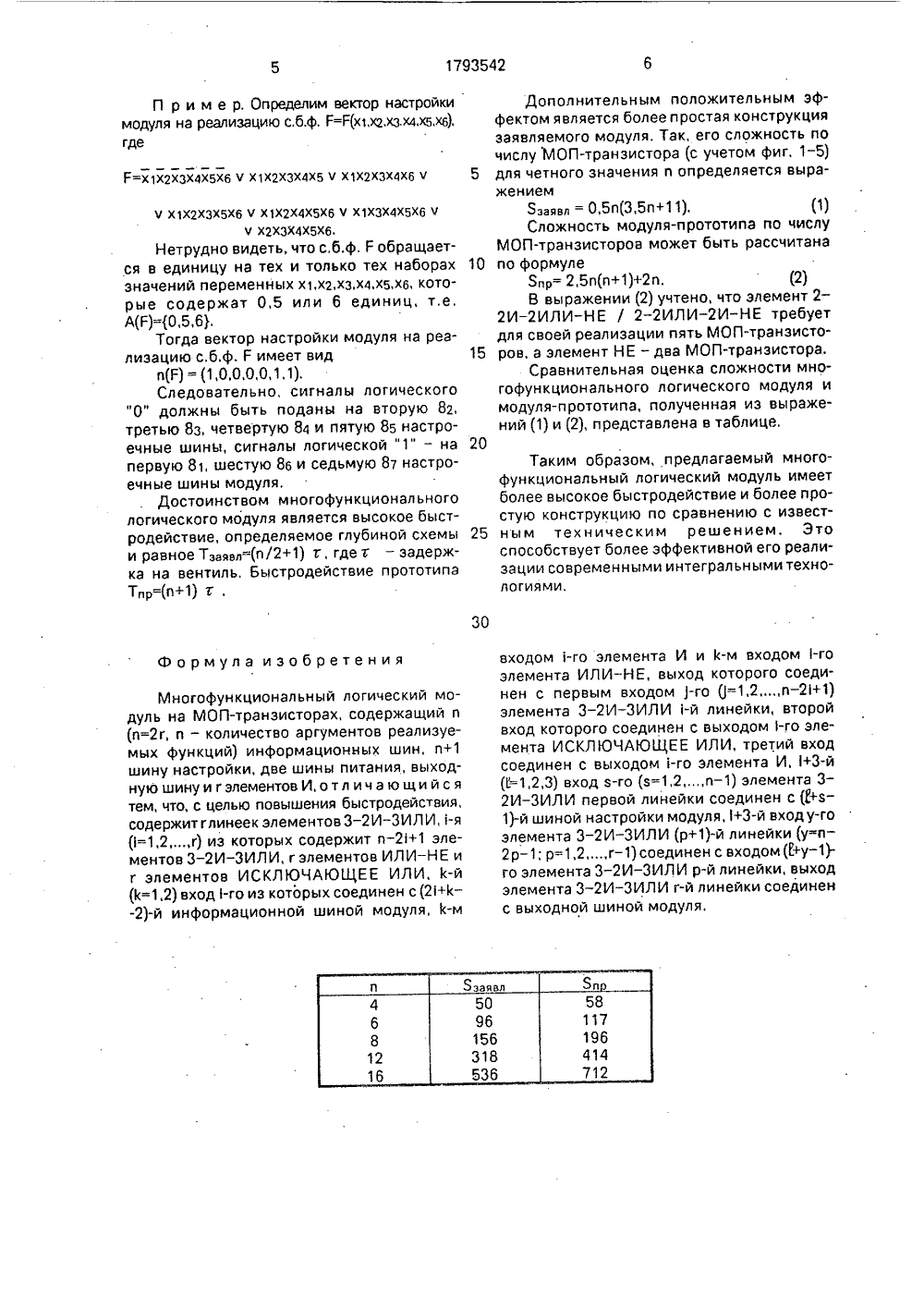

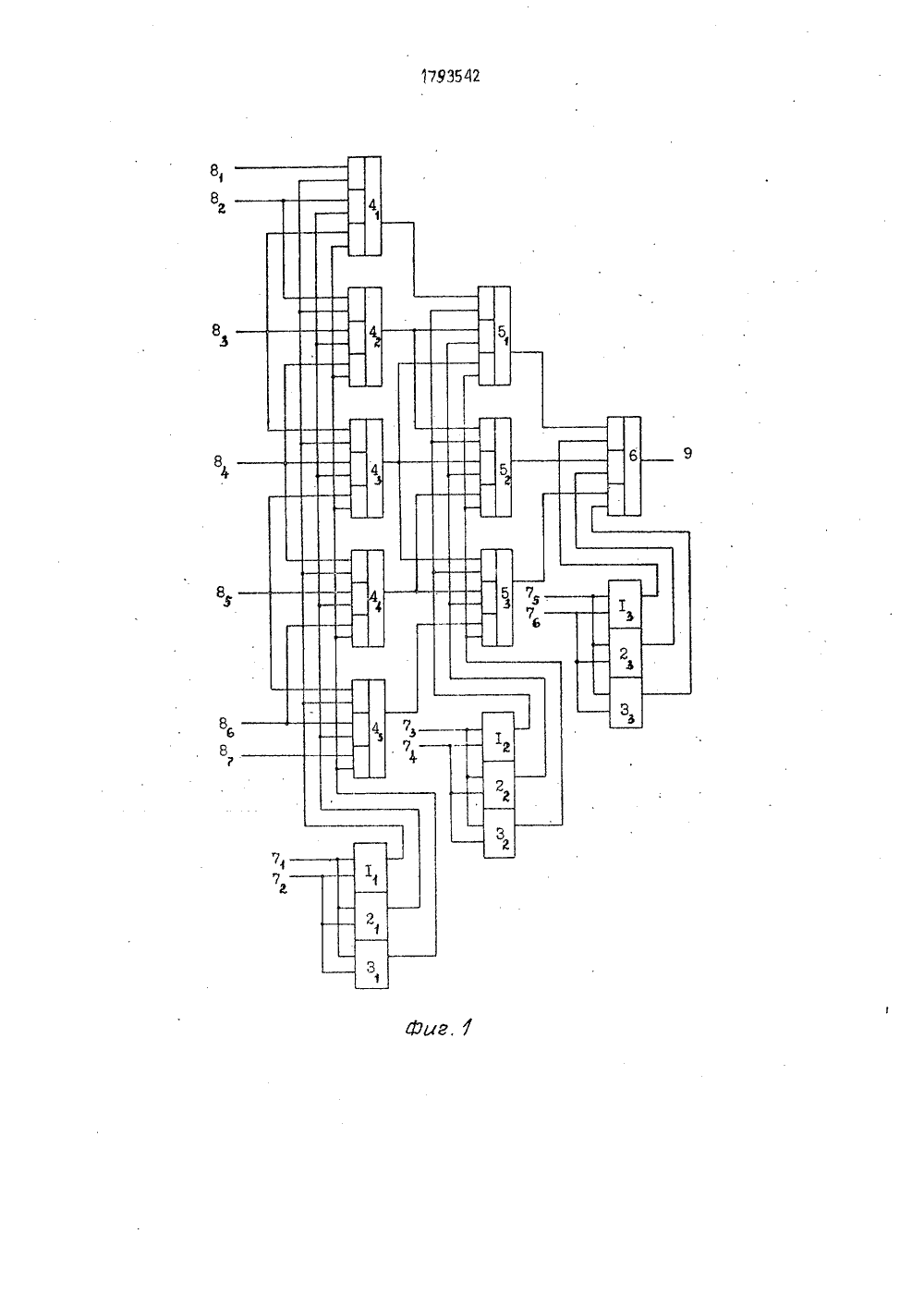

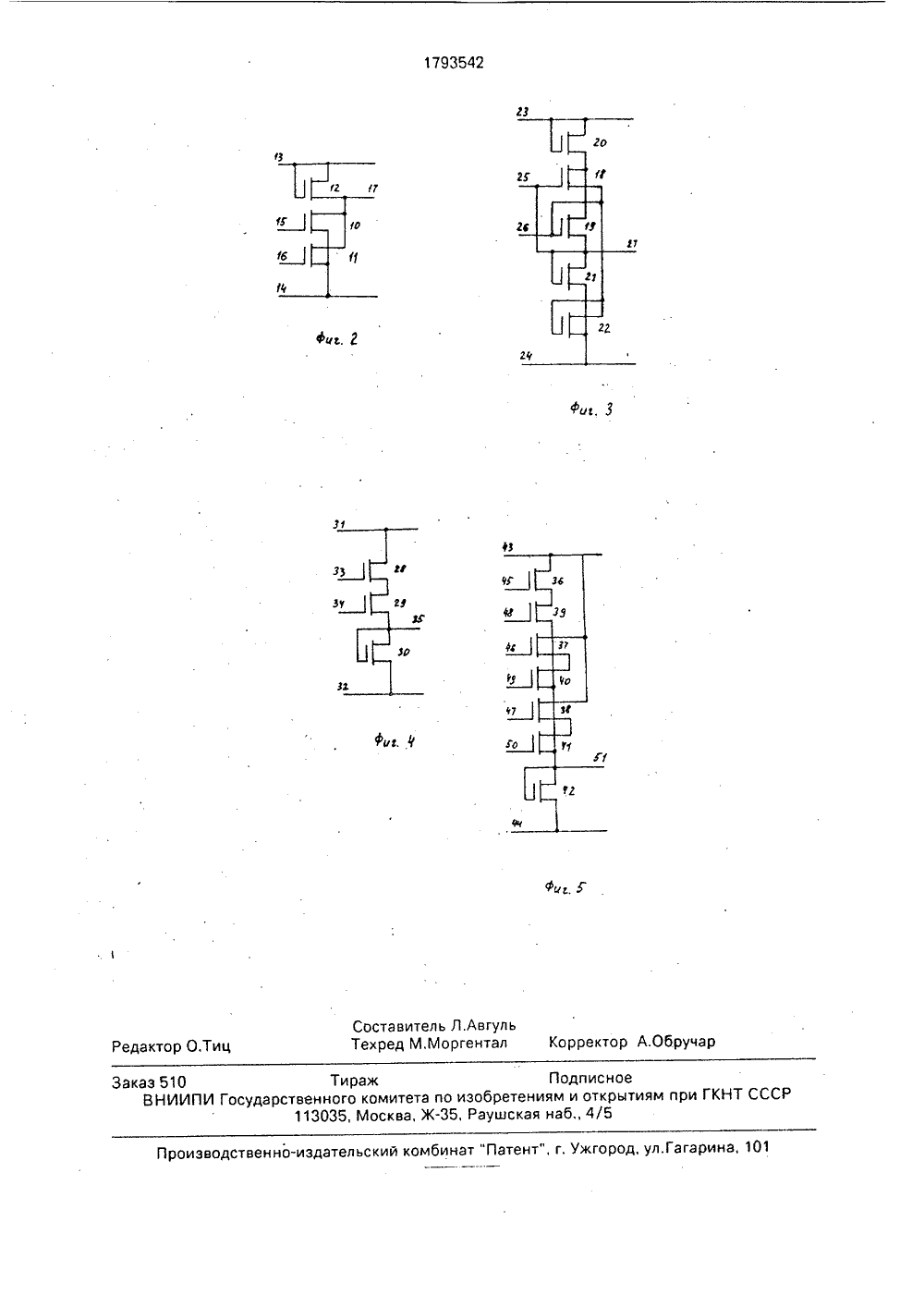

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 9) 3 К 19 094 53)5 ЕТЕН ИЯ ОБР ОПИСАН тво СССР4, 1989,тво СССР4, 1990.ЬНЫЙ ЛОГИЧЕя к импульсной ке и предназнатрических булеГОСУДАРСТВЕННОЕ ПАТЕНТНОВЕДОМСТВО СССР(54) МНОГОФУН КЦИОНАЛСКИЙ МОДУЛЬ(57) Изобретение относитстехнике и микроэлектроничено для реализации симме Изобретение относится к импульснойтехнике и микроэлектронике и предназначено для вычисления симметрических булевых функций (с,б.ф) и переменных,Известен многофункциональный логический модуль на МОП-транзисторах, содержащий и линеек элементов И и и линеек элементов ИСКЛЮЧАЮЩЕЕ ИЛИ (1.Недостатками модуля являются высокая конструктивная сложность (по числу МОП-транзисторов) и нйзкое быстродействие, определяемое глубиной схемы и равное 2 и г, где т - задержка на вентиль.Наиболее близким по функциональным возможностям и конструкции техническим решением к предлагаемому является многофункциональный логический модуль, реализующий с.б.ф и переменных и содержащийвыполненные на МОП-транзисторах и элементов НЕ и и линеек элементов 2 - 2 ИЛИ - 2 И-НЕ/2-2 ИИЛИ - НЕ 2.Недостатком известного модуля является низкое быстродействие, определяемое глубиной схемы и равное (и+1) г Ж 1793542 А вых функций и переменных. Сущность изобретения: цель достигается тем, что многофункциональный логический модуль содержит г(и=2 г, и - количество переменных реализуемых функций) элементов ИЛИ-НЕ, г элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, г элементов И, г линеек элементов 3-2 И - ЗИЛИ, и информационных шин, и+1 шин настройки, две шины питания и выходную шину. Сложность модуля по числу МОП-транзисторов составляет 0;5 и(3,5 п+11), а быстродействие, определяемое глубиной схемы, равно и/2+1. 1 табл., 5 ил.ШВЦель изобретения - повышение быстродействия многофункционального логического модуля.Цель достигается тем, что в многофункциональный логический модуль на МОП- .транзисторах, содержащий п (и=2 г, и - количество аргументов реализуемых функций) информационных шин, и+1 шин настройки, две шины питания, выходную шину и г элементов И, введены г линеек элементов 3 - 2 И - ЗИЛИ, 1-я (1=1,2 г) из которых (А содержит и+1 элементов 3 - 2 И-ЗИЛИ, г СЛ элементов ИЛИ-НЕ и г элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, Е-й (1=1,2) вход 1-го из которых соединен с (21+1 - 2)-й информационной шиной модуля, 1-м входом 1-го элемента И и К-м входом 1-го элемента ИЛИ - НЕ, выход которого соединен с первым входом )-го (=1,2и - 21+1) элемента 3-2 И-ЗИЛИ 1-й линейки, второй вход котброго соединен с выходом 1-гр элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход соединен с выходом 1-го элемента И, (Е+3)-й (1,2,3) вход 3-го (з=1,2и- -1) элемента 3 - 2 И - ЗИЛИ первой линейки соединен с (1+э+1)-й шиной настройки модуДвухвходовый элемент ИЛИ-НЕ (фиг. 2) содержащем ровно т единвыполнен на двух переключательных 10 и 11 видно, что п=1 тогда и тои одном нагрузочном 12 МОП-транзисторах, совпадает с одним из равключенных между шинами 13 и 14 питания. 55 ции Р,Первая 15 и вторая 16 входные шины элемента соединены соответственно с затворами транзисторов 10 и 11, Выходная шина 17соединена с истоком транзистора 12 (со стоками транзисторов 10 и 11), А(Р) с,б.ф. Е=Р(х 1,хгхп),ля, (0+3)-й вход ч-го элемента 3-2 И-ЗИЛИ (р+1)-й линейки (ч=пр - 1; р=1,2,г - 1) сое.- динен с выходом (Г+ч)-го элемента 3-2 ИЗИЛИ р-й линейки, выход элемента 3 - 2 И-ЗИЛИ г-й линейки соединен с выходной шиной модуля,Многофункциональный логический модуль на МОП-транзисторах содержит и (п=2 г, и - количество аргументов реализуемых функций) информационных шин, и+1 шин настройки, две шины питания, выходную шину, г элементов И, г линеек элементов 3-2 И-ЗИЛИ, 1-я (1=1,2,г) из которых содержит и - 21+1 элементов 3 - 2 И - ЗИЛИ. г элементов ИЛИ - НЕ и г элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, Причем К-й (1=1,2) вход 1-го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с (2+М)-й информационной шиной модуля, М-м входом 1-го элемента И и М-м входом 1-го элемента ИЛИ-НЕ. Выход 1-го элемента ИЛИ-НЕ соединен с первым входом )-го Ц=1,2,п+1) элемента 3 - 2 И - ЗИЛИ 1-й линейки, второй вход которого соединен с выходом 1-го элемента И СКЛ ЮЧАЮЩЕЕ ИЛИ, третий вход соединен с выходом 1-го элемента И, Далее (1+3)-й ф 1,2,3) вход з-го (з,2 п - 1) элемента 3-2 И - ЗИЛИ первой линейки соединен с (+з - 1)-й шиной настройки модуля, а (1+3)-й вход ч-го элемента 3 - 2 И - ЗИЛИ (р+1)-й линейки (ч=п - 2 р - 1, . р=1,2 г - 1) соединен с выходом (+-1)-го элемента 3-2 И - ЗИЛИ р-й линейки, Выход элемента 3 - 2 И - ЗИЛИ г-й линейки соединен с выходной шиной модуля.В качестве примера на фиг. 1 представлена схема модуля при п=6, на фиг, 2, 3, 4 и 5 - соответственно варианты выполнения на МОП-транзисторах элементов ИЛИ - НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, И и 3 - 2 И-ЗИЛИ.При п=б(фиг. 1) модуль содержит выполненные на МОП-транзисторах г=п/2=3 элементов ИЛИ-НЕ 11, 12 и 1 з, г=З элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 2, 22 и 2 з, 3 элементов И 31, 32 и Зз, и - 1=5 элементов 3-2 ИЗИЛИ 41.4 ь первой линейки, и-З-З элементов 3 - 2 И-ЗИЛИ 51, 52 и 5 з второй линейки, п - 5=1 элемент 3 - 2 И - ЗИЛИ 6 третьей линейки, п=6 информационных шин 71 76, и+1=7 шин 818 т настройки, выходную шину 9,Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ (фиг, 3)выполнен на двух переключательных 18 и 19и трех нагрузочных 20,21 и 22 МОП-транзисторах, включенных между шинами 23 и 245 питания, Первая 25 и вторая 26 входныешины элемента соединены соответственнос затворами транзисторов 18 и 19, На выходной шине 27 (исток транзистора 19 реализуется функция ИСКЛЮЧАЮЩЕЕ ИЛИ10 (сложение по модулю два),Двухвходовый элемент И (фиг, 4) выполнен на двух переключательных 28 и 29 иодном нагрузочном 30 МОП-транзисторах,включенных между шинами 31 и 32 питания.15 Первая 33 и вторая 34 входные шины элемента соединены соответственно с затворами транзисторов 28 и 29, выходная шина 35соединена с истоком транзистора 29 (со стоком и затвором транзистора 30),20 Элемент 3 - 2 И - ЗИЛИ (фиг. 5) выполненна шести переключательных 3641 и одномнагрузочном 42 МОП-транзисторах,включенных между шинами 43 и 44 питания,Входные шивы элемента с первой по шес 25 тую 45,50 соединены соответственно с затворами транзисторов 36.;.41, Выходнаяшина 51 элемента соединена с истокамитранзисторов 39, 40 и 41 (со стоком и затвором транзистора 42).30 Многофункциональный ло еский модуль работает следующим образом. На информационные шины 77 ь поступают двоичные переменные х.хв соответ ственно, на настроечные шины 8181 -сигналы настройки попб соответственно,. значения которых принадлежат множеству(0,1), На выходной шине 9 реализуется с,б,ф, Е=Р(х 1,Х 2,хз,х 4,хь,хб), определяемая векто ром, настройки п(Р)=(по,п 1,п 2,пз п 4 пб,пб).Поясним алгоритм настройки модуля.Пусть с,б.ф. Г существенно зависит от и переменных х,х 2.,х и пусть а 1,аг,а - рабочие числа функции Р (см., например, 45 Поспелов Д,А. Логические методы анализаи синтеза схем. - М.: Энергия, 1974), где 0 ап+1. Известно, что произвольная с,б.ф, и переменных Г может быть однозначно задана (и+1)-разрядным двоичным кодом 50 п(Р)=(по,п 1,п), где пс- значение функции Ена (любом) наборе значений и переменных,иц (1=0,1.п). Очелько тогда. когда с бочих чисел функСледовательно, определение компонентов вектора настройки п(Р) сводится к нахождению множества всех рабочих чисел1793542 30 П р и м е р. Определим вектор настройкимодуля на реализацию с,б.ф. Г=Р(Х 1,Х 2,хз,х 4,хб,хб),где Е=х 1 х 2 хзх 4 х 5 хб ч хх 2 хзх 4 х 5 ч х 1 х 2 хзх 4 хб ч Ч Х 1 Х 2 ХЗХ 5 Х 6 ч Х 1 Х 2 Х 4 Х 5 Хб Ч Х 1 ХЗХ 4 Х 5 Х 6 ЧЧ Х 2 ХЗХ 4 Х 5 Х 6.Нетрудно видеть, что с,б.ф. Р обращается в единицу на тех и только тех наборах значений переменных х 1,х 2,хз,х 4,х 5,хб, которые содержат 0,5 или 6 единиц, т,е, А(Р)=(0,5,6),Тогда вектор настройки модуля на реализацию с,б.ф. Р имеет види(Е) = (1,0,0.0,0,1,1).Следовательно, сигналы логического "0" должны быть поданы на вторую 82, третью 8 з, четвертую 84 и пятую 85 настроечные шины, сигналы логической "1" - на первую 81, шестую 86 и седьмую 87 настроечные шины модуля,Достоинством многофункционального логического модуля является высокое быстродействие, определяемое глубиной схемы и равное Тзвявл=(и/2+1) т, где г - задержка на вентиль, Быстродействие прототипа Тпр=(и+1) т . Формула изобретения Многофункциональный логический модуль на МОП-транзисторах, содержащий и (и=2 г, и - количество аргументов реализуемых функций) информационных шин, п+1 шину настройки, две шины питания, выходную шину и г элементов И, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия, содержит глинеек элементов 3-2 И - ЗИЛ И, -я (=1,2г) из которых содержит и - 2+1 элементов 3 - 2 И - ЗИЛИ, г элементов ИЛИ - НЕ и г элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, К-й (=1,2) вход -го из которых соединен с (2+с - -2)-й информационной шиной модуля, К-м Дополнительным положительным эффектом является более простая конструкция заявляемого модуля. Так, его сложность по числу МОП-транзистора (с учетом фиг, 1-5) 5 для четного значения и определяется выражениемЯзаявл = 0,5 п(3,5 и+11). (1) Сложность модуля-прототипа по числуМОП-транзисторов может быть рассчитана 10 по формулеЯп р= 2,5 п(и+1)+2 и. (2) В выражении (2) учтено, что элемент 22 ИИЛИ-НЕ / 2-2 ИЛИИ-НЕ требует для своей реализации пять МОП-транзисто ров, а элемент НЕ - два МОП-транзистора.Сравнительная оценка сложности многофункционального логического модуля и модуля-прототипа, полученная из выражений (1) и (2), представлена в таблице.20 Таким образом, предлагаемый многофункциональный логический модуль имеет более высокое быстродействие и более простую конструкцию по сравнению с извест ным техническим решением. Этоспособствует более эффективной его реализации современными интегральными технологиями,входом -го элемента И и 1-м входом -го элемента ИЛИ-НЕ, выход которого соединен с первым входом )-го (=1,2 и - 2+1) элемента 3 - 2 И - ЗИЛИ -й линейки, второй вход которого соединен с выходом -го элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход соединен с выходом -го элемента И, +3-й (1=1,2,3) вход э-го (э=1,2,и - 1) элемента 3- 2 И-ЗИЛИ первой линейки соединен с (+з)-й шиной настройки модуля, +3-й входу-го элемента 3-2 И-ЗИЛИ (р+1)-й линейки (у"п р; р=1,2 г) соединен с входом (1+у)- го элемента 3 - 2 И - ЗИЛИ р-й линейки, выход элемента 3-2 И - ЗИЛИ г-й линейки соединен с выходной шиной модуля,1193542 Составитель Л,АвгульТехред М.Моргентал Корректо Редактор О,Ти ар оизводственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 аз 510 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб 4/5

СмотретьЗаявка

4917425, 07.03.1991

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ, БЕЛОРУССКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ИМ. В. И. ЛЕНИНА

АВГУЛЬ ЛЕОНИД БОЛЕСЛАВОВИЧ, СУПРУН ВАЛЕРИЙ ПАВЛОВИЧ

МПК / Метки

МПК: H03K 19/094

Метки: логический, многофункциональный, модуль

Опубликовано: 07.02.1993

Код ссылки

<a href="https://patents.su/5-1793542-mnogofunkcionalnyjj-logicheskijj-modul.html" target="_blank" rel="follow" title="База патентов СССР">Многофункциональный логический модуль</a>

Предыдущий патент: Коммутирующее устройство

Следующий патент: Управляемый делитель частоты следования импульсов

Случайный патент: 83721