Устройство селекции информационных импульсов на фоне помех

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1167718

Автор: Будько

Текст

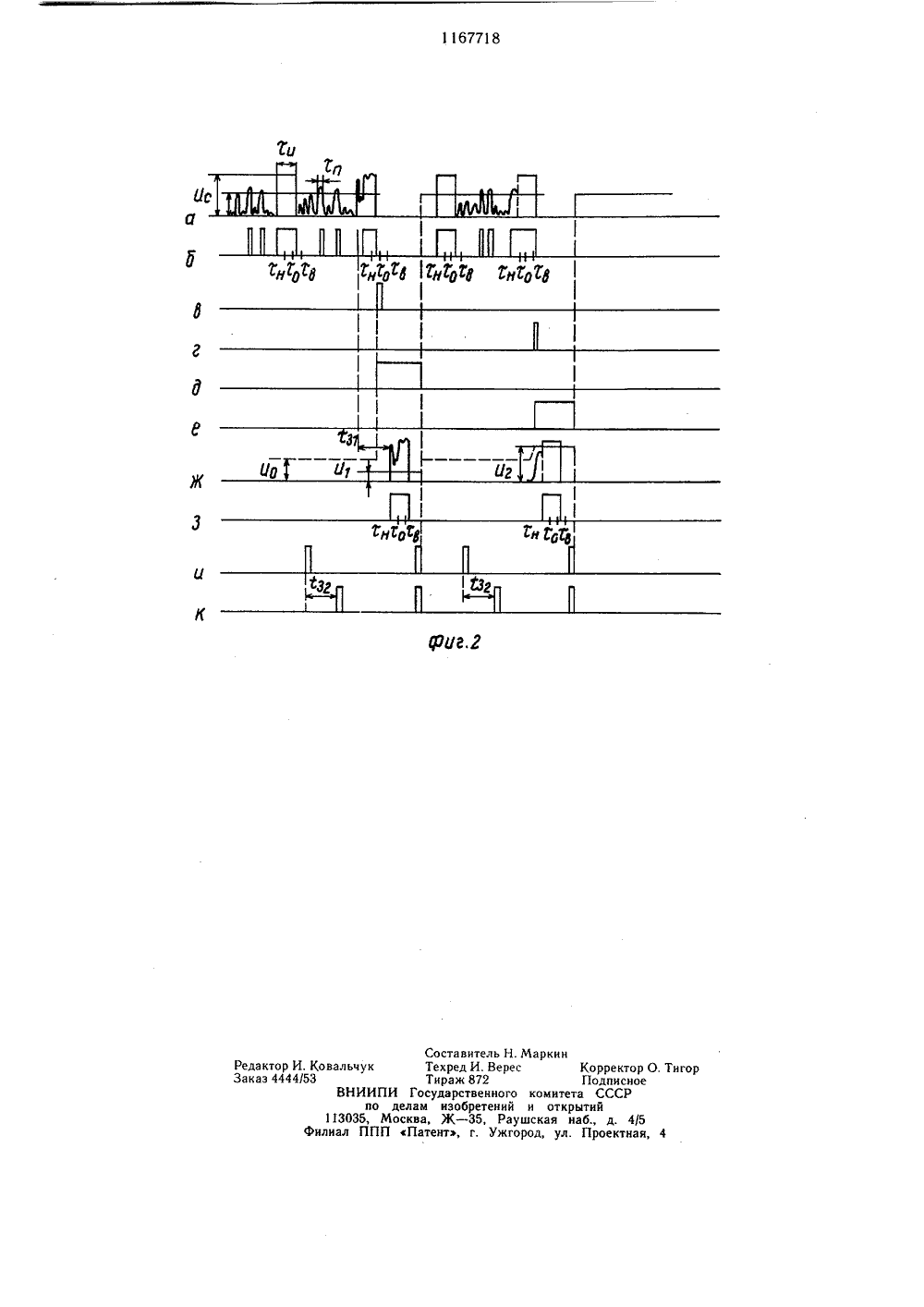

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИН 11677 Н 03 К 5/26 л1 1 ИСАНИЕ ИЗОБРЕТЕН КОМ ЕТЕЛЬСТВ НА ОСУДАРСТВЕННЫЙ НОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(56) 1. Венедиктов М. Д., Марков В. В., Эйдус. Асинхронные адресные системы связи. М., Связь, 1968, с. 83, рис. 3,21.2. Авторское свидетельство СССР584433, кл. Н 03 К 5/26, 28.06.76 (прототип).(54) (57) УСТРОЙСТВО СЕЛЕКЦИИ ИНФОРМАЦИОННЫХ ИМПУЛЬСОВ НА ФОНЕ ПОМЕХ, содержащее последовательно соединенные амплитудный компаратор и селектор импульсов по длительности, источник опорного напряжения, отличающееся тем, что, с целью повышения надежности селектирования, в него введены первый и второй блоки задержки, один из которых включен между входной шиной и первым входом амплитудного компаратора, а второй - между первым выходом селектора импульсов по длительности и выходной шиной, формирователь импульсов, первый и второй триггеры, единичные входы которых подключены соответственно ко второму и третьему выходам селектора импульсов по длительности, а нулевые входы объединены и через формирователь импульсов подключены к выходной шине, три аналоговых ключа, выходы которых объединены и подключены к второму входу амплитудного компаратора, а входы - соответственно к первому, второму и третьему выходам источника опорного напряжения, управляющие входы первого и второго аналоговых ключей соединены соответственно с прямыми выходами первого и второго триггеров, элемент ИЛИ, входы которого подключены к инверсным выходам триггеров, а выход - к объединенным управляющим входам третьего аналогового ключа и первого блока задержки, дополнительный инвертор, выход которого подключен к управляющему входу второго блока задержки, а вход - к выходу элемента ИЛИ, при этом каждый из блоковзадержки содержит линию задержки, вход которой соединен с входом блока задержки, фф четвертый и пятый аналоговые ключи, выхо- Ъф У ды которых объединены и подключены к выходу блока задержки, вход четвертого аналогового ключа подключен к входу линии р задержки, а вход пятого - к ее выходу, инвертор, выход которого соединен с управляющим входом пятого ключа, а вход объединен с управляющим входом четвертого аналогового ключа и подключен к управ- фф ляющему входу блока задержки.Изобретение относится к импульсной технике и может быть использовано в устройствах связи и телеметрии при передаче дискретной информации по каналам с аддитивными помехами.5Известно устройство селекции информационных импульсов на фоне помех, содержащее последовательно соединенные амплитудный дискриминатор (пороговый элемент),селектор им пульсов по длительности 1 .В данном устройстве недостаточная на- Одежность селектирования, обусловленнаяфиксированным значением порога дискриминаций импульсов по амплитуде и по длительности, что приводит к пропуску информационных импульсов при действии в канале связи аддитивных импульсных помех.Наиболее близким по технической сущности к предлагаемому является устройство длявыделения информационных импульсов нафоне помех, содержащее последовательносоединенные амплитудный компаратор и селектор импульсов по длительности, источникопорного напряжения, сумматор, соединенный с одним из входов амплитудного компаратора, интегратор, второй селектор по длительности, входом подключенный к выходупервого селектора по длительности и входу 25интегратора, выход которого подключен к другому входу амплитудного компаратора, приэтом выход второго селектора импульсовпо длительности соединен с управляющимвходом источника опорного сигнала 2.Недостаток известного устройства - низкая надежность выделения информационныхимпульсов на фоне помех вследствие того,что при случайном совпадении информационного импульса с импульсом помехи и пересечения результирующим импульсом порогана выходе компаратора может сформировать- З 5ся импульс укороченной (или увеличенной)длительности. Если при этом его длительность окажется меньше (или больше) порога срабатывания селектора импульсов подлительности, то на выход устройства этотимпульс не пройдет, т. е. произойдет 40пропуск информационного импульса,Цель изобретения - повышение надежности селектирования.Поставленная цель достигается тем, что вустройство селекции информационных им пульсов на фоне помех, содержащее последовательно соединенные амплитудный компаратор и селектор импульсов по длительности, источник опорного напряжения, введены первый и второй блоки задержки, один из которых включен между входной шиной и первым входом амплитудного компаратора, а второй - между первым выходом селектора импульсов по длительности и выходной шиной, формирователь импульсов, первый и второй триггеры, единичные входы которых подключены соответственно к второму и третьему выходам селектора импульсов по длительности, а нулевые входы объединены и через формирователь импульсов подклюцены к выходной шине, три аналоговых ключа, выходы которых объединены и подключены к второму входу амплитудного компаратора, а входы - соответственно к первому, второму и третьему выходам источника опорного напряжения, управляющие входы первого и второго аналоговых ключей соединены соответственно с прямыми выходами первого и второго триггеров, элемент ИЛИ, входы которого подключены к инверсным выходам триггеров, а выход - к объединенным управляющим входам третьего аналогового ключа и первого блока задержки, дополнительный инвертор, выход которого подключен к управляющему входу второго блока задержки, а вход - к выходу элемента ИЛИ, при этом каждый из блоков задержки содержит линию задержки, вход которой соединен с входом блока задержки, четвертый и пятый аналоговые ключи, выходы которых обьединены и подключены к выходу блока задержки, вход четвертого аналогового ключа подключен к входу линии задержки, а вход пятого - к ее выходу, инвертор, выход которого соединен с управляющим входом пятого ключа, а вход объединен с управляющим входом четвертого аналогового ключа и подключен к управляющему входу блока задержки.На фиг. 1 приведена структурная схема предлагаемого устройства селекции информационных импульсов на фоне помех; на фиг. 2 - временные диаграммы, поясняющие работу устройства, где а - входной сигнал, б - сигнал на выходе амплитудного компаратора, о и г - сигналы на выходах ( и ) селектора импульсов по длительности соответственно д и е сигналы на выходах триггеров, ж - сигнал на выходе блока задержки, з - сигнал на выходе амплитудного компаратора при анализе задержанного импульса, а - выходной сигнал селектора импульсов по длительности, к - сигнал на выходе устройства.Устройство содержит элемент 1 согласования с каналом связи, первый и второй блоки 2 и 3 задержки, каждый из которых состоит из линии 4 задержки, аналоговых ключей 5 и 6, инвертора 7, при этом выходы аналоговых ключей 5 и 6 объединены и соединены с выходом блока задержки, вход аналогового ключа 5 объединен с входом линии 4 задержки, соединенного с входом блока задержки, вход аналогового ключа 6 соединен с выходом линии 4 задержки, а управляющий вход -- с выходом инвертора 7, вход которого соединен с управляющим входом аналогового ключа 5 и соединен с управляющим входом блока задержки, последовательно соединенные амплитудный компаратор 8 и селектор 9 импульсов по длительности, при этом первый вход амплитудного компаратора 8 соединен с выходом блока 2 задержки, а выход селектора 9 импульсов по длительности соединен с входом блока 3 задержки, источник Оопорного напряжения, аналоговые ключи 11 - 13, выходы которых соединены и подключены к второму входу амплитудного компаратора 8, а входы - соответственно к первому, второму и третьему входам источника 10 опорного напряжения, триггеры 14 и 15, единичные входы которых соединены соответственно с вторым и третьим выходом селектора 9, а нулевые входы объединены и через формирователь 16 импульсов подключены к выходу блока 3 задержки, прямые выходы соединены соответственно с управляющими входами аналоговых ключей 12 и 13, элемент ИЛИ 17, входы которого соединены с инверсными выходами триггеров 14 и 15, а выход - с объединенными управляющими входами аналогового ключа 11 и блока 2 задержки, дополнительный инвертор 18, вход которого подключен к выходу элемента ИЛИ 17, а выход - к управляющему входу блока 3 задержки. Выход элемента 1 согласования соединен с входом блока 2 задержки, а вход подключен к входной шине 19, а выходная шина 20 - к выходу второго блока 3 задержки.Устройство работает следующим образом.В исходном состоянии триггера 14 и 15 находятся в нулевом состоянии и на их инверсных выходах действует напряжение логической 1, которое поступает на входы элемента ИЛИ 17, и, следовательно, на его выходе также действует напряжение логической 1, Это напряжение поступает на управляющие входы аналогового ключа 11 и блока 2 задержки, при этом ключи 11 и 5 будут открыты, а ключ 6 закрыт напряжением логического О с выхода инвертора 7. Через инвертор 18 выходное напряжение элемента ИЛ.И 17 подается на управляющий вход блока 3 задержки, в результате этого его ключ 5 будет закрыт, а ключ 6 открыт напряжением логической 1 с выхода инвертора 7. Аналоговые ключи 12 и 13 будут закрыты напряжением логического О с прямых выходов триггеров 14, 15 и с выхода источника 10 через открытый ключ 11 на первый вход амплитудного компаратора 8 поступает напряжение 1)о, которое является начальным порогом срабатывания компара тора, Устройство готово к работе. С входной шины 19 сигнал, содержащий импульсы помехи, информационные импульсы и информационные импульсы, искаженные помехами, через элемент 1 согласования, например эмиттерный повторитель для согласования выходного сопротивления канала со входным сопротивления устройства, поступает на вход первого блока 2 задержки. Информационные импульсы характеризуются длительностью ти амплитудой 1.; импульсы помехи - длительностью ти случайной амплитудой 11. Через открытый аналоговый ключ 5 сигнал поступает на второй вход амплитудного компаратора 8 (фиг. 2 а) и од овременно на вход линии 4 задержки пер 5 1 О 15 20 25 30 35 40 45 50 55 вого блока 2 задержки, с выхода которой подается на вход аналогового ключа 6. Однако на выход первого блока 2 задержки сигнал не проходит, поскольку аналоговый ключ 6 закрыт. При этом возможны следующие случаи.На вход амплитудного компаратора 8 поступает информационный импульс, не искаженный на уровне порога 11 о помехой фиг. 2 а, позиция 1). В этом случае на выходе компаратора появляется импульс длительностью Ги стандартной амплитуды (фиг. 2 б), который поступает на вход селектора 9 импульсов по длительности. Селектор 9 имеет три порога селекции по времени - нижнийноминальный то и верхний т., установленные с учетом изменения длительности импульсов помехи и возможных изменений длительности информационных импульсов под действием помехи (фиг, 2 б). Поскольку в данном случае длительность импульса, анализируемого селектором 9, находится в заданном диапазоне длительностей, т. е. между порога мии Е, то на выходе селектора формируется выходной импульс (фиг. 2 и), который поступает на вход линии 4 задержки второго блока 3 задержки. Через время задержки (з, = 1 з, выходной импульс селектора 9 через открытый аналоговый ключ 6 поступит на выходную шину 20 (фиг. 2 к).Допустим, что следующий информационный импульс искажен импульсом помехи так, как показано на фиг. 2 а, позиция 2. В этом случае на выходе амплитудного компаратора 8 появится импульс укороченной длительности (т - т), (фиг. 26), который, как и в.предыдущем случае, будет анализироваться селектором 9. Поскольку сейчас длительность анализируемого импульса меньше заданной, т. е. находится между порогами тн, то (фиг. 2 б), то на выходе селектора 9 импульс будет отсутствовать, а на его выходе ( появится сигнал (фиг. 2 в), который переключит триггер 15 в единичное состояние (фиг. 2 д). Напряжение логической 1 с прямого выхода триггера 15 откроет аналоговый ключ 12, а напряжение логического О с инверсного выхода через элемент ИЛИ 17 закроет аналоговые ключи 11 и 5, а через инвертор 7 откроет ключ 6 второго блока 3 задержки. В результате этого на первый вход амплитудного компаратора 8 с источника 10 через ключ 12 поступит напряжение порога ЦБ,а на второй вход с блока 2 задержки - информационный импульс с задержкой 1 з, которая определяет время предварительного анализа импульса. Поскольку сейчас амплитудный компаратор 8 имеет порог срабатывания 1.1 значительно меньше амплитуды искажений (провала) импульса (фиг. 2 ж), то на его выходе появится импульс нормальной длительности (фиг. 2 з), и, следовательно, на выходе селектора 9 импульсов по длительности сформируется выходной импульс (фиг. 2 и, пози 1167718ния 2). С выхода селектора 9 импульс поступает на вход блока 3 задержки и через его аналоговый ключ 5, открытый напряженнем логической 1 с выхода дополнительного инвертора 18, инвертирующий выходной сигнал элемента ИЛИ 17 без задержки поступает на выход устройства. При этом ключ 6 второго блока 3 задержки закрыт выходным напряжением логического 0 инвертора 7.Таким образом, устраняется искажение временного интервала между информационными импульсами на выходе устройства, что важно для последующей их обработки (фиг. 2 к. По заднему фронту выходного импульса формирователь 16 формирует короткии импульс (не показан), который поступает на нулевой вход триггера 15 и устанавливает его в нулевое состояние (фиг. 2 д), в результате чего устройство возвращается в исходное состояние и готово к анализу следукщего импульса, (например, на фиг. 2 а, позиция 3).Пусть под действием импульса помехи с амплитудойпроизошло искажение информационного импульса (фиг. 2 а, позиция 4), т. е. произоИло совпадение импульса помехи с информационным импульсом на временном интервале разрешано,цей способности амплитудного компаратора 8, в агом сл, ае на его выходе сформируется импульс, длительность (т+т) которого булибольше порога селектора 9 импульсов по длительности (фиг. 26). Следовательно, как и в предыдущем случае, импульс на его выходе будет отсутствовать, а на выходепоявится сигнал (фиг. 2 г), который установит триггер 4 в единичное состояние (фиг. 2 е).Напряжение логической 1 с прямоговыхода триггера 15 откроет аналоговый ключ, и на вход амплитудного компаратора 8 с источника 1 О поступит напряжение порога2.)о (фиг, 2 ж). В дальнейшем работа устройства будет происходить аналогично рассмотренной в предыдущем случае (фиг. 2 з, и, к).На вход устройства поступают импульсыпомехи. Если амплитуда импульсов меньше порога )о амплитудного компаратора 8, то отклика на.эти импульсы на выходе компара тора не будет. На импульсы, амплитуда которых превышает порог )о, на выходе компаратора 8 появятся отклики (фиг. 2 б), однако на выходную шину 20 они пройдут, так как их длительность меньше порога тн селектора 9 импульсов по длительности, и 15 устройство останется в исходном состоянии.Таким образом, предлагаемое устройствоселекции информационных импульсов на фоне помех в отличие от известных устройств, обеспечивает выделение информационных импульсов, искаженных импульсами помехи.что повышает надежность селектирования.Значение начального порога Б амплитудного компаратора определяется статистическими свойствами дискретного сигнала - вероятностями появления нулей и единиц на по зициях кода и распределением амплитуд сигнала и помехи. При равновероятном появлении нулей и единиц в коде или в случае использования для передачи информации балансного кода с равным числом нулей и единиц выбирается Ьп= - 0,5 Ь,.З 0 Значение порогов Б 1 и Ь 2 определяетсяс учетом максимально возможных выбросов амплитуды импульсов помехи или заранее выбираются близкими к нулевому уровню и амплитудному значению информационного импульса соответственно. В последнем случае устройство обеспечивает выделение информационных импульсов при соотношении сигнал/помеха = .1 167718 ЦРиг,Сост Техр Тира ПИ Госуда о делам из Москва, П Патент авитель Н.Маркинед И. Вересж 872рственного комитеобретений и открЖ - 35, Раушская

СмотретьЗаявка

3687500, 09.01.1984

ПРЕДПРИЯТИЕ ПЯ Г-4493

БУДЬКО ЛЕОНИД МИХАЙЛОВИЧ

МПК / Метки

МПК: H03K 5/26

Метки: импульсов, информационных, помех, селекции, фоне

Опубликовано: 15.07.1985

Код ссылки

<a href="https://patents.su/5-1167718-ustrojjstvo-selekcii-informacionnykh-impulsov-na-fone-pomekh.html" target="_blank" rel="follow" title="База патентов СССР">Устройство селекции информационных импульсов на фоне помех</a>

Предыдущий патент: Устройство для выделения отдельных полупериодов переменного напряжения

Следующий патент: Частотный компаратор

Случайный патент: Способ получения циклогексана