Цифровой формирователь манипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1019663

Авторы: Комаров, Мусулманкулова, Никифорова, Савватеев

Текст

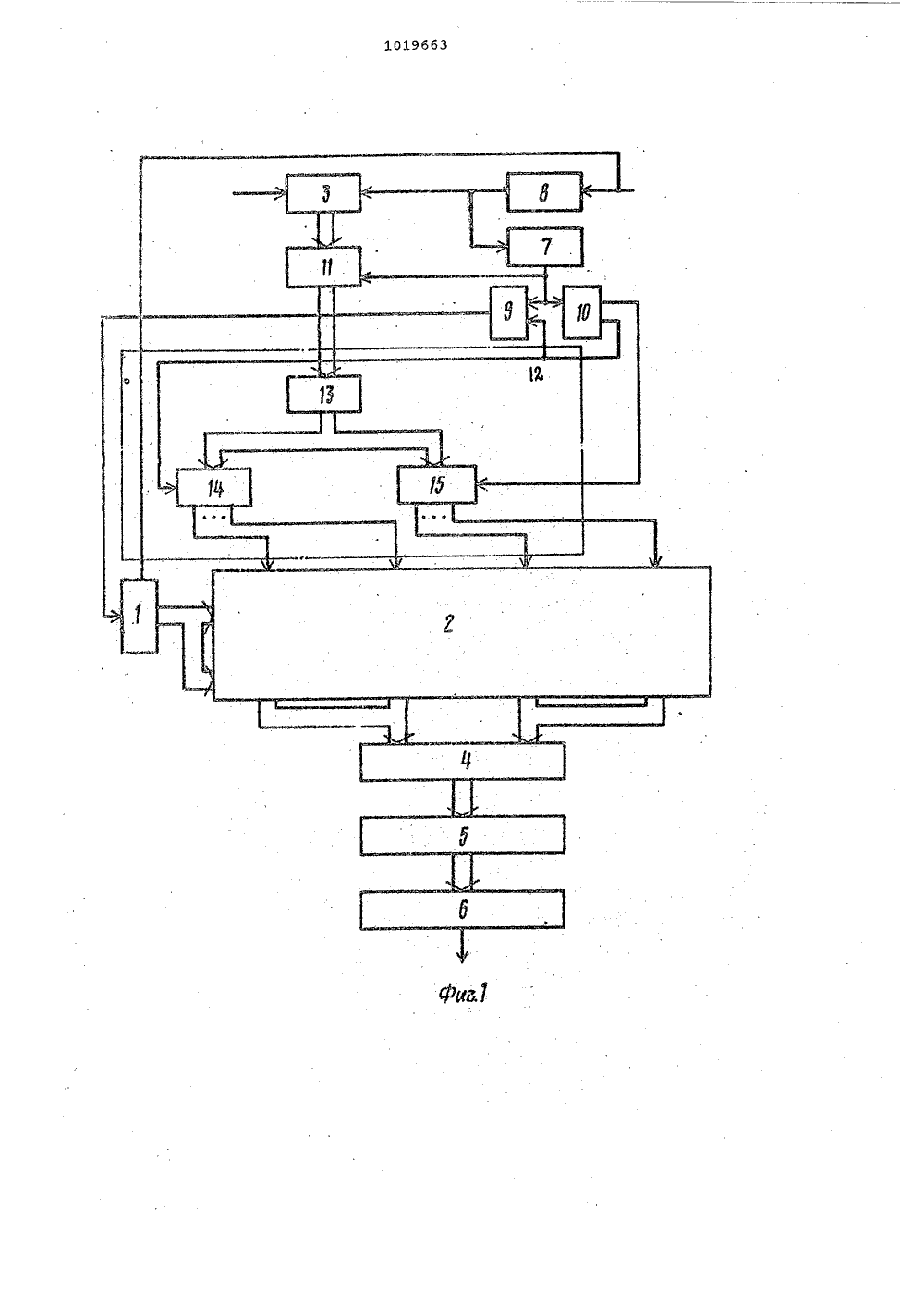

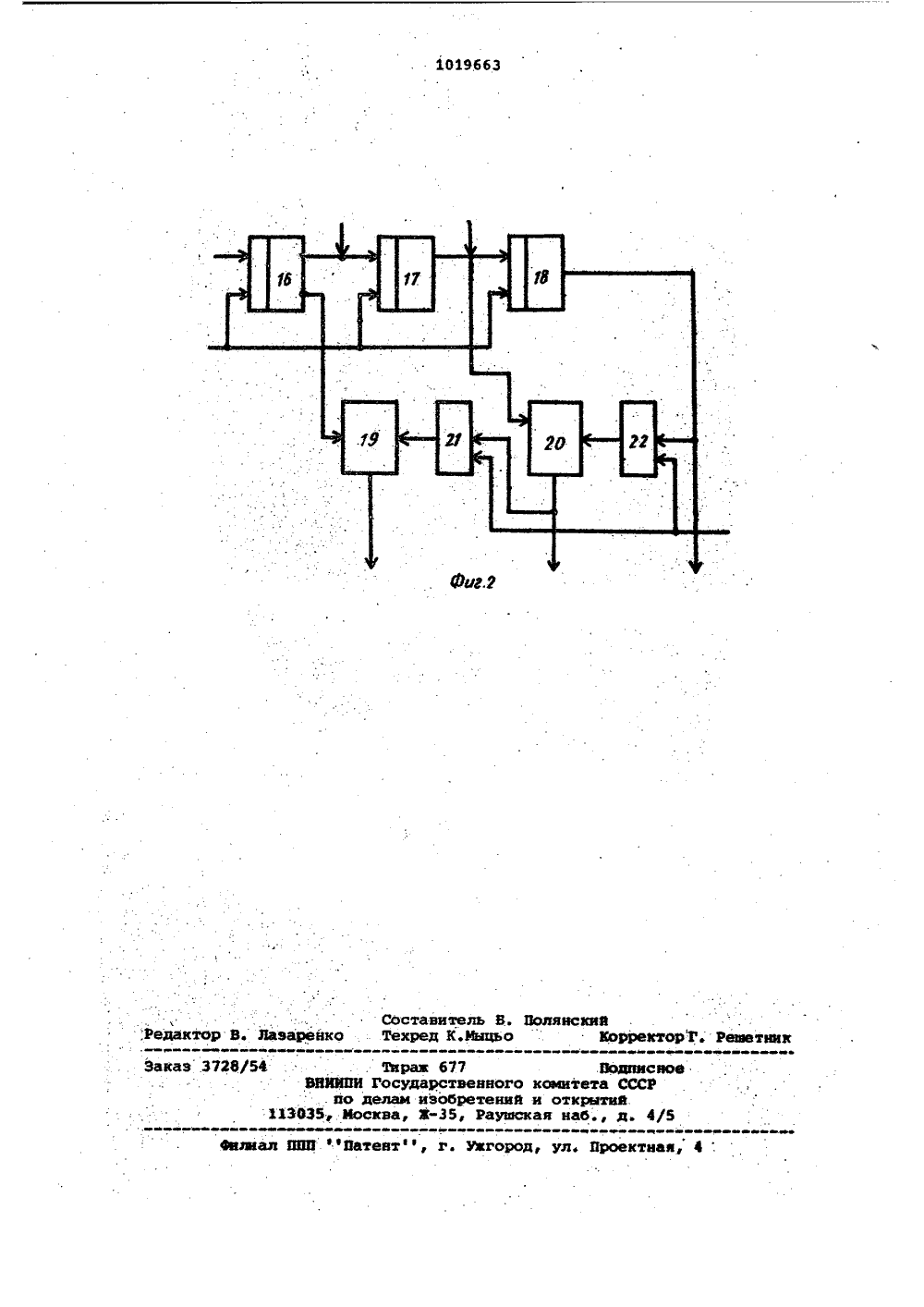

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН 66 1 27/26 АРСТВЕННЫЙ КОМИТЕТ СССРЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(56) 1. Авторское свидетельство СССРР 653764, кл. Н 04 Ь 27/20, 1976(54)(57) 1. ЦИФРОВОЙ ФОРИИРОВАТРЛЬМАНИПУЛИРОВАНИЯ СИГНАЛОВ, содержащий два делителя частогы, накапливающий сукчатор, блок памяти, дешифратор, сумматор и фильтр нижнихчастот, о т л и ч а ю щ и й с ятем, что с целью повышения точностипри формировании"сигналов с многопозиционной амплитудной, частотнойи фазовой манипуляцией, введеныраспределитель, цифроаналоговый преобразователь, триггер, элемент Иикодер, выходы которого подключенык информационным входам накапливающего сумматора, управляющий входкоторого соединен.с входом триггера:,с Первым входом элемента И и,с выходом первого делитвля частоты,вход которого соединен с входом кодера и с выходом второго делителя частоты, вход которого соединен с пер, вым входом распределителя, выходыкоторого подключены к одним входам,блока памяти, другие входы и выходыкоторого соединены. соответственнос выходами дешифратора и со входамисумматора, выходы которого черезцифроаналоговый преобразователь подключены ко входам Фильтра нижнихчастот, при этом первый выход триггера соединен с вторым входом элемента И, выход которого подключенко второму входу распределителя, и с первым входом деьыфратора, к вто=рому входу которого подключен второй выход триггера, а выходы накал" лнвающего сумматора соединены с соответствующими входами дезвфратора,2. Устройство по п.1,о т л и ч а ю щ е е с я тем, что деввфратор содержит два регистра и распредели." тель, выходы которого подключены к одним входам регистров, выходы которых являются выходами деоифратора, входами которого являются входы распределителя и другие входы регистров.3, Устройство по п, 1, о т л ич а ю щ е е с я тем," что кодер содержит три триггера, два сумматора по модулю два и два элемента И, при этом первый выход первого тригге ра подключен к первому входу второго триггера, второй вход которого соединен с вторым входом первого триггера, второй выход которого подключен к первому входу первого сум" матора по модулю два, второй вход " которого соединен с выходом первого элемента И, первый вход которого соединен с выходом второго суммато" ра по модулю два, первый вход кото." рого соединен с выходом второго триггера и с первым входом третьего :триггера, второй вход и выход которо го соединены соответственно с вторым входом второго триггера и с пер вым входом второго элемента И, второй вход и выход которого соединены соответственно с вторым входом пере вого элемента И и с вторьв входомвторого сумматора по модулю дваю прчем выходы сумматоров по модулю два и выход третьего триггера являются выходами кодера, входаьщ которого являются первые входы триггеров и вторые входы элюеентов И.входом третьего триггера, второйвход и выход которого соединены соответственно с вторым входом второго10 триггера и с первым входом второгоэлемента И, второй вход и.выход которого соединены соответственно совторым входом первого элемента И ис вторым входом второго сууМатора 15 по модулю два, причем выходы .сумматоров пс модулю два и выход третьеготриггера являются выхсцщии кодера,. входы триггеров и вторые входы эле ментов И.На фиг. 1 п.представлена структурная электрическая схема предложенного цифровогоФормирователя; нафиг. 2 - вариант выполнения кодера.25 ЦиФровой фоРмирователь манипулиР рованных сигналов содержит распределитель 1, блок 2 памяти, кодер 3,суьеаатор 4, цифроаналоговый преобразователь 5, фильтр б нижних частот,первый и второй делители частоты7 и 8 соответственно, элемент И 9,триггер 10, канапливающий сумматор11, дешифратор 12, состоящий иэ распределителя 13 и двух регистров 14,и 15. При этом кодер состоит иэ(фиг, 2) первого 1 б, второго 17 итретьего 18 триггеров, первого ивторого сумматоров помодулю два 19и 20 соответственно и первого ивторого элементов И 21 22 соответ ственно.Цифровой формирователь манипулированных сигналов работает следующим образом.От источника сообщения (не пока вано) на первый вход циФрового формирователя, а именно на первыйвход кодера З,.каждые Тс поступают данные, соответствующие вариан"там. разностей Фаз при относительной 5 О Фаэовой манипуляции или частоте амплитуды передаваемой посылки при.частотной .амплитудной манипуляции .На второй вход цифрового формирователя одновременно с данными посту 5;пает последовательность импульсовс частотой, .равной частоте отсчетовпосылки. Передаваемые данные послеперекодирования иэ относительногокода в двоичный с выхода кодера 3поступают на накапливающий сумматор 6 О 11, где происходит сложение значений этих данных с .результатом оуммирования всех предыдущих кодов данных. Ийменение бита передаваемыхданным соответствует скачку Фазы 65 или частоты. амплитуды передаваемой Изобретение относится к технике .связи и может использоваться дляпередачи дискретной информации поканалам связи,Известен цифровой Формировательманипулированных сигналов, содержащий два делителя частоты, накапли.вающий сумматор, блок памяти, де"шиФратор, сумматори Фильтр нижнихчастот 1),Однако известный цифРваой 4 И 93 жВ-.рователь имеет низкую точность приФормировании сигналов с многопозиционной амплитудой, частотной и Фазовой манипуляцией.Цель изобретения - повышение.точности при Формировании сигналовс многопоэиционной амплитудной,частотной и Фаэовой манипуляцией.Поставленная цель достигаетсятем, что в цифровой формировательманипулированных,сигналов, содержа"щий два делителя частоты, накапли"вающий сумматор, блок памяти, дешифратор,:сумматор и фильтр нижнпх.частот, введены распределитель цифроаналоговый преобразователь, триггеэлемент И и кодер, выходЫ которогоподключены кинформационным входамнакапливающего .сумматора, управляющий вход которого соединен с входомтриггера, с первым входом элементаИ и с выходом первого делителя час-тоты, вход которого соединен с.входом кодера и с выходом второго делителя частоты, вход которого соедииецс первым входом распределителя, выходы которого подключены к одним входам блока памяти, другие входы ивыходы которого соединены соответственно с выходами деьжФратора и совходами сумматора, выходы которогочерез цифроаналоговый преобразователь подключены ко входам Фильтранижних частот, при этом первый выходтриггера соединен со вторым входомэлемента И, выход которого нодклвчен ко второму входу распределителя,и с первым входом дешифратора, к второму входу которого подключен второй выход триггера, а .выходы накапливающего сумматора соединены с соответствующими входами дешифратора.При этом дешифратор содержит дварегистра и распределитель,. выходыкоторого подключены к однйм входамрегистров, выходы которых являются.выходами дешифратора, выходами которого являются .входы распределителя .и другие входы регистров.Причем кодер содержит три триггера, два сумматора по модулю два идва элемента И, при этом первый выход первого триггера подключен. кпервому входу второго триггера,второй ввод которого соединен с вторым входом первого триггера, второй.выход которого подключен к первому входу первого сумматора по модулю два, второй вход которого соединен с выходом первого элемента И, первый вход которого соединен с выходом второго сумматора по модулю два, первый вход которого соединен с выходом второго триггер и с первымпосылки. Результат суммирования подается на вход распределителя 13 де-..шифратора 12, который производитпреобраЗОвания поступающего двоичного кода,в позиционный и по соответ"ствующему входу подает его в блок 2,памяти. Затем происходит запись сигнала логической 11 ф с выхода распределителя 13 в одну из ячеек регистров 14 или 15, причем запись прОизводитсяпередним Фронтом импульса,поступакщего с выхода. триггера 10.. Сигнал логической 1 ф с выходоврегистров 14 или 15 поступает на соответствующий вход блока 2 памятии являетсясигналом разрешения на 15считывание ивформации, записаннойв данном блоке памяти. На каждуюстроку блока 2:памяти поступают импульсы считывания с выхода распределителя 1 на второй вход которого :20поступают.импульсы с частотой Р отсчета. Распределитель 1 обнуляетсясигналом.с выхода элемента И 9,Импульсы считывания с. блока памятиподаются со сдвигом, .равным 1/2 Т ,. 25посылки (из-за Формирования посылокс перекрытием). Считйванйе отсчетов.эталонов .производится параллельнона .сумматор 4, В цифроаналоговомпреобразователе 5 цифровые посылкипреобразуются в аналоговые и Фильтрнижних. частот 6 отфильтровывает по"лученный аналоговый сигнал.Рассмотренный пеийцип реализациицифроаналогового Формирования сигналов с относительной Фазовой манипуляцией:приемлем и для сигналов самплитудной и частотной манипуляцией,при этом данные с кодера поступают.непосредственно .на групповой входдешифратора. 46Использование нового принципаФормирования манипулированного сиг-.нала, реализуемого с помощью блокапамяти, дешифратора и. цифроаналогово"го преобразователя, по сравнению с 45известным позволяет обеспечить в предложенном цифровом формирователе требуемую точность Формирования сигнала, Для Формирования любого манипулированного сигнала достаточ-. но записать соответствующую ему копию эталона перекрывающихся иоеылок, сформированного с учетом огибающих, а именно коды отсчетов эталона .в блок памяти, считывая их соответственно передаваемому символу и суммируя, можно получить. нижний сигнал.Таким образОм, по сРажнениЮ С Известным предложенный. цифровой Форми" рователь позволяет повысить точность Формирования сигнала, которая опре-. деляется.количеством разрядов в кодах отсчетов, разрядностью цифроаналогового преобразователя, частотой Формирования отсчетов и избирательностью Фильтра нижних частот. Разряд- ность отсчетов Формируемых сигналов можетеуыть выбрана любой что обеспечивает необходимую точность Форми" роваиия манипулированного сигнала.Кроме того, известный цифровой Формирователь и другие аналогичные устройства позволяют Формировать без изменения.их схем только один. из видов манипуляции. В то время, как предложенный цифровой Формирователь . позволяет формировать сигналы любого вида манипуляции, что существенно расширяет его Функциональные возмож-, ности.Помимо повышения точности Формирования передаваемых сигналов и. рас" шнрения Функциональных возможностеЯ преддоженный цифровой Формирователь обеспечивает более высокую всравнении с известным надежность, так как реализуется на высоконадежных типовых функциональных узлах вычислительной техники, выпускаемых или намеченных в будущем к серийному выпуску, это .же обстоятельство опре-, деляет низкую стоимость предложенно-. го цифрового Формирователя..2 в СоставительТехред К.Мыць вский Лазаре Редак Г Реаетннк ЮЭ. до делам изобретени13635, Москва, З, Раувск комитетаи открытийан наб.,

СмотретьЗаявка

3434575, 04.01.1982

ПРЕДПРИЯТИЕ ПЯ В-2655

САВВАТЕЕВ ВЛАДИМИР СЕРГЕЕВИЧ, МУСУЛМАНКУЛОВА АЙГУЛЬ КЫДЫРМАЕВНА, НИКИФОРОВА ТАТЬЯНА МИХАЙЛОВНА, КОМАРОВ НИКОЛАЙ ИВАНОВИЧ

МПК / Метки

МПК: H04L 27/26

Метки: манипулированных, сигналов, формирователь, цифровой

Опубликовано: 23.05.1983

Код ссылки

<a href="https://patents.su/5-1019663-cifrovojj-formirovatel-manipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой формирователь манипулированных сигналов</a>

Предыдущий патент: Демодулятор многоканального модема с амплитудно фазоразностной манипуляцией

Следующий патент: Факсимильный передатчик

Случайный патент: Устройство для разравнивания лесосечных отходов