Устройство для коррекции ошибок приемника факсимильных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 946008

Автор: Ляшевич

Текст

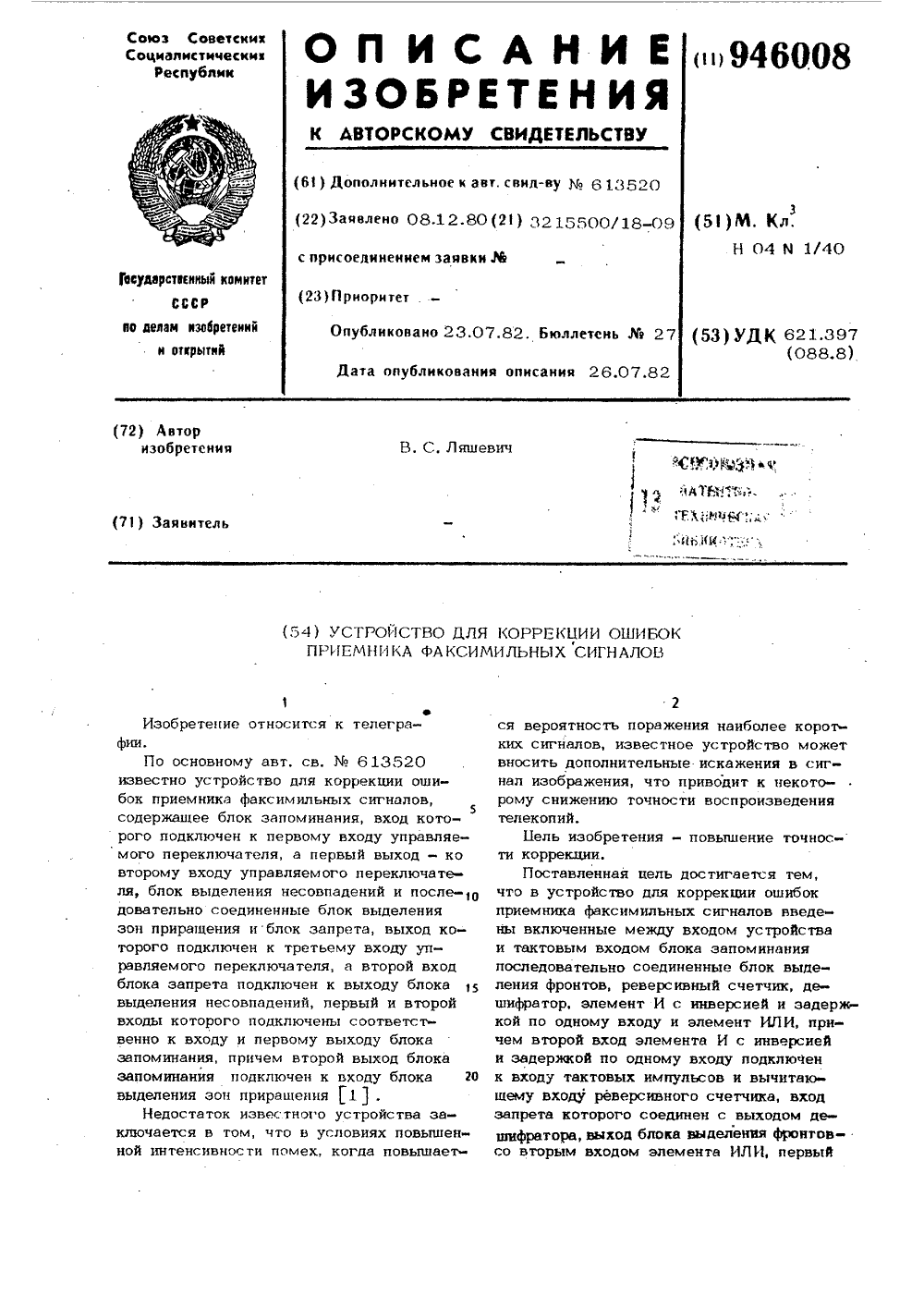

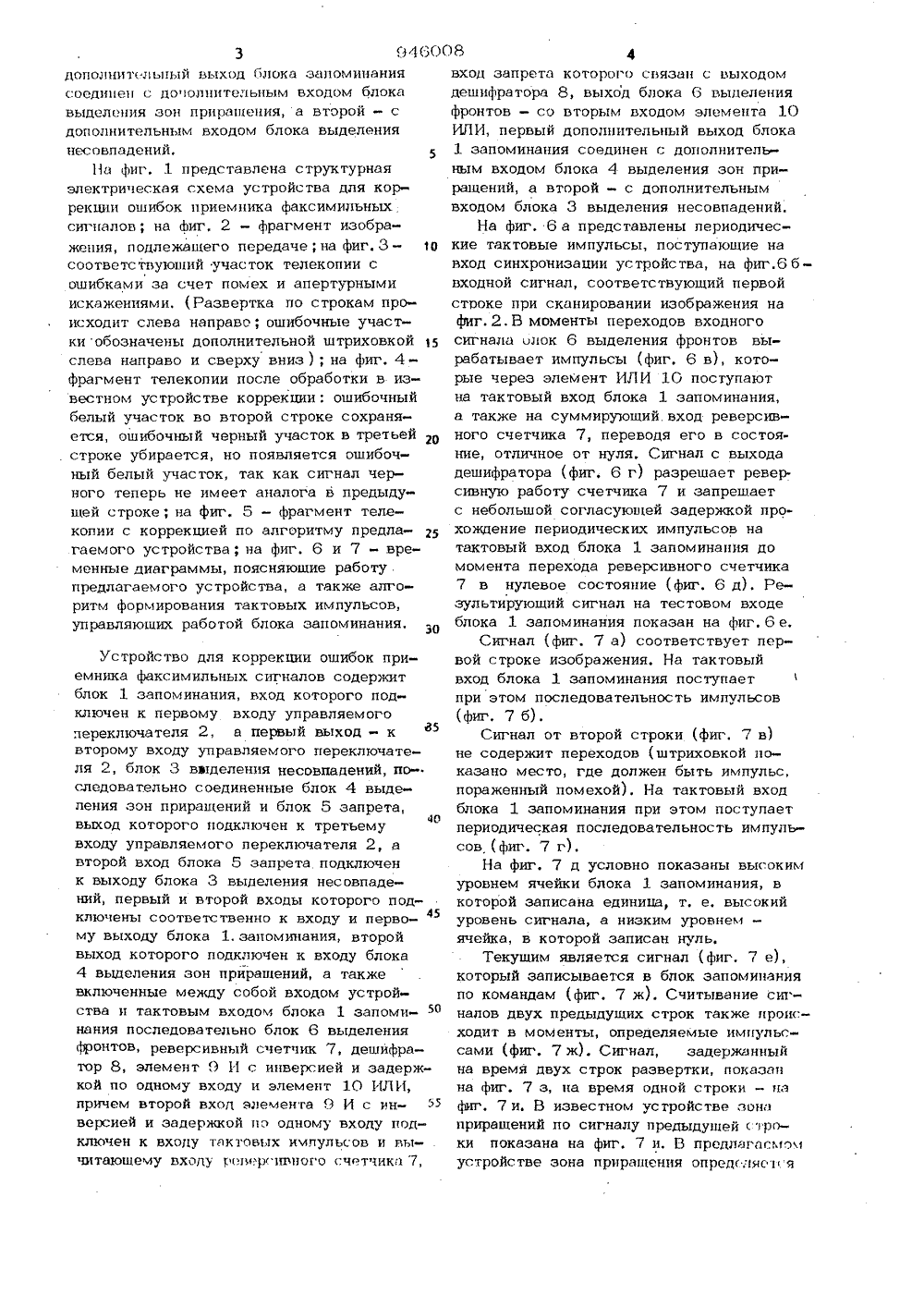

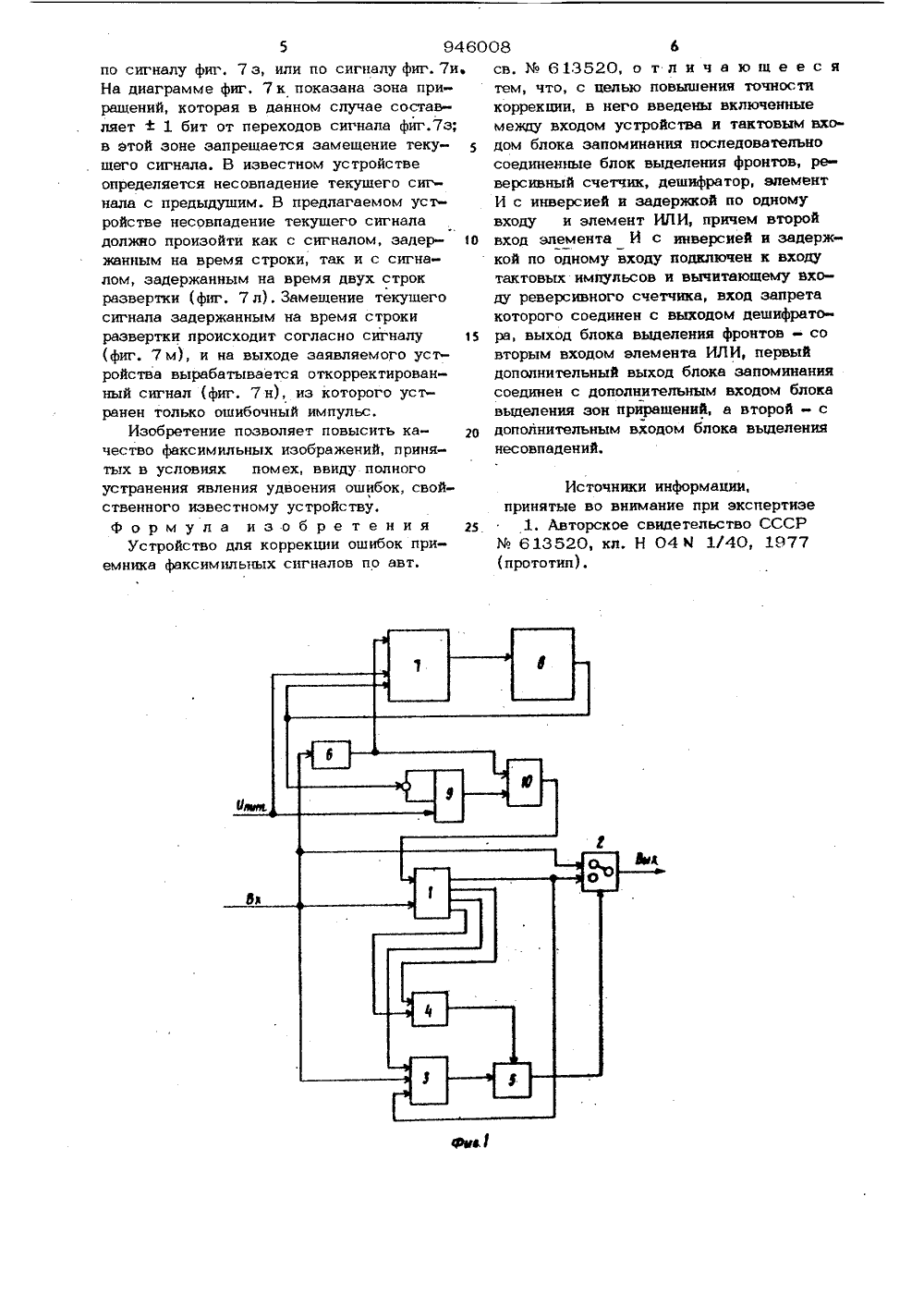

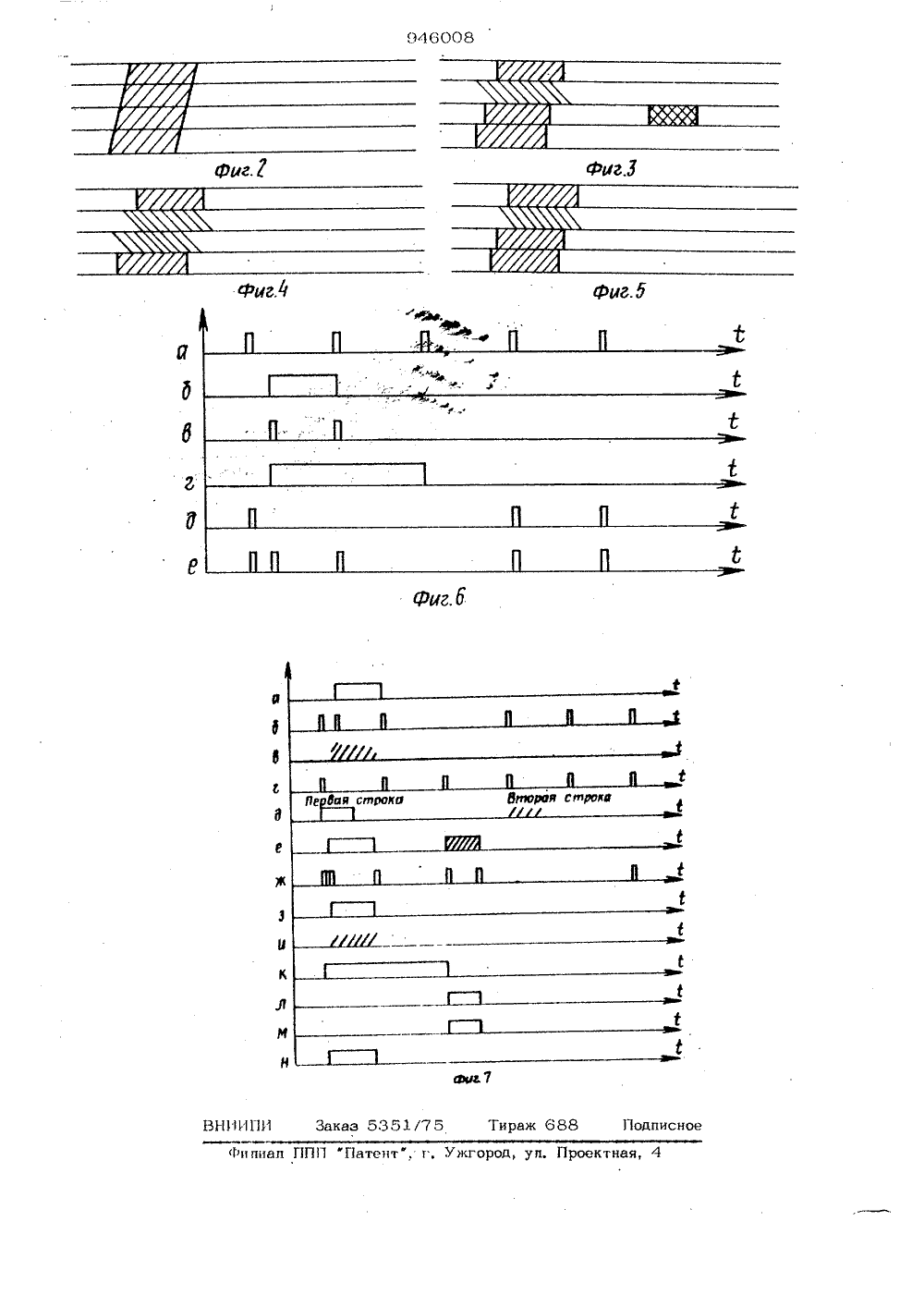

Союз СоветскихСоциалистическихРеспублик ОП ИСАНИЕИ 306 РЕТЕН ИЯК АВТОРСКОМУ СВМДЕТЕЛЬСТВУ п 946008(54 ) УСТРОИ СТВО ДЛЯ КОРРЕ КЦИИ ОШИБОК ПР ЕМНИ КА ФАКСИМИЛЬНЫХ СИГНАЛОВ1ФИзобретение относится к телеграфии,По основному авт, св. % 613520известно устройство для коррекции ошибок приемника факсимильных сигналов,5содержащее блок запоминания, вход которого подключен к первому входу управляемого переключателя, а первый выход - ковторому входу управляемого переключателя, блок выделения несовпадений и после-тодовательно соединенные блок выделениязон приращения и блок запрета, выход которого подключен к третьему входу управляемого переключателя, а второй входблока запрета подключен к выходу блока твыделения несовпадений, первый и второйвходы которого подключены соответственно к входу и первому выходу блоказапоминания, причем второй выход блоказапоминания подключен к входу блока 20выделения зон приращения Е 1 ),Недостаток известнот о устройства заключается в том, что в условиях повышенной интенсивности помех, когда повьпдается вероятность поражения наиболее корот- ких сигналов, известное устройство может вносить дополнительные искажения в сигнал изображения, что приводит к некоторому снижению точности воспроизведения телекопий.Е 1 ель изобретения - повышение точности коррекции.Поставленная цель достигается тем, что в устройство для коррекции ошибок приемника факсимильных сигналов введены включенные между входом устройства и тактовым входом блока запоминания последовательно соединенные блок выделения фронтов, реверсивный счетчик, дешифратор, элемент И с инверсией и задержкой по одному входу и элемент ИЛИ, причем второй вход элемента И с инверсией и задержкой по одному входу подключен к входу тактовых импульсов и вычитающему входу реверсивного счетчика, вход запрета которого соединен с выходом дешифратора, выход блока выделения фронтовсо вторым входом элемента ИЛИ, первый3 9460дОГ 03 Те ты 1 ый выход Ока зсломиациясоединен с дополнительным входом блокавыделения зоц прирапения, а второй - сдополнительным входом блока выделениянесовпадений,5На фиг. 1 представлена структурнаяэлектрическая схема устройства для коррекшп ошибок приемника факсимильныхсигналов; ца фиг. 2 - фрагмент изображения, подлежащего передаче; на фиг. 3- 10соответствующий участок телекопии сошибками за счет помех и апертурнымиискажениями. (Развертка по строкам происходит слева направо; ошибочные участки обозначены дополнительной штриховкой 15слева направо и сверху вниз ); на фиг. 4 фрагмент телекопии после обработки в известном устройстве коррекции: ошибочныйбелый участок во второй строке сохраняется, ошибочный черный участок в третьей остроке убирается, но появляется ошибочный белый участок, так как сигнал черного теперь не имеет аналога в предыдущей строке; на фиг. 5 - фрагмент телекопии с коррекцией по алгоритму предлагаемого устройства; ца фиг. 6 и 7 - временные диаграммы, поясняющие работупредлагаемого устройства, а также алгоритм формирования тактовых импульсов,управляющих работой блока запоминания. Устройство для коррекции ошибок приемника факсимильных сигналов содержит блок 1 запоминания, вход которого подключен к первому входу управляемого переключателя 2, а первый выход - к35 второму входу управляемого переключателя 2, блок 3 вэделения несовпадений, последовательно соединенные блок 4 выделения зон приращений и блок 5 запрета,4 о выход которого подключен к третьему входу управляемого переключателя 2, а второй вход блока 5 запрета подключен к выходу блока 3 выделения несовпадений, первый и второй входы которого подключены соответственно к входу и первому выходу блока 1.запоминания, второй выход которого подключен к входу блока 4 выделения зон приращений, а также включенные между собой входом устройства и тактовым входом блока 1 запоми О нация последовательно блок 6 выделения фронтов, реверсивный счетчик 7, дешифратор 8, элемент 9 И с инверсией и задержкой по одному входу и элемент 10 ИЛИ, причем второй вход элемента О И с ин версией и задержкой цо одному входу подключен к входу тактовх импульсов и вы читающему входу роер ивцого счетчика 7,вход запрета которого связан с выходом дешифратора 8, выход блока 6 выделения фронтов - со вторым входом элемента 10 ИЛИ, первый дополнительный выход блока 1 запоминания соединен с дополнительным входом блока 4 выделения эон приращений, а второй - с дополнительным входом блока 3 выделения несовпадений.На фиг. 6 а представлены периодические тактовые импульсы, поступающие на вход синхронизации устройства, на фиг.6 бвходной сигнал, соответствующий первой строке при сканировании изображения на фиг. 2, В моменты переходов входного сигнала олок 6 выделения фронтов вырабатывает импульсы (фиг, 6 в), которые через элемент ИЛИ 10 поступают на тактовый вход блока 1 запоминания, а также на суммирующий вход реверсивного счетчика 7, переводя его в состояние, отличное от нуля, Сигнал с выхода дешифратора (фиг. 6 г) разрешает ревер. сивную работу счетчика 7 и запрещает с небольшой согласующей задержкой прохождение периодических импульсов на тактовый вход блока 1 запоминания до момента перехода реверсивного счетчика 7 в нулевое состояние (фиг, 6 д). Результирующий сигнал на тестовом входе блока 1 запоминания показан на фиг. 6 е.Сигнал (фиг. 7 а) соответствует первой строке изображения, На тактовый вход блока 1 запоминания поступает при этом последовательность импульсов (фиг, 7 б).Сигнал от второй строки (фиг. 7 в) не содержит переходов (штриховкой показано место, где должен быть импульс, пораженный помехой). На тактовый вход блока 1 запоминания при этом поступает периодическая последовательность импульсов ( фиг. 7 г) .На фиг. 7 д условно показаны высоким уровнем ячейки блока 1 запоминания, в которой записана единица, т. е. высокий уровень сигнала, а низким уровнем - ячейка, в которой записан нуль.Текущим является сигнал (фиг. 7 е), который записывается в блок запоминания по командам (фиг. 7 ж). Считывание сиг - налов двух предыдуших строк также происходит в моменты, определяемые имцульссами (фиг. 7 ж). Сигнал, задержанный на время двух строк развертки, показан ца фиг. 7 з, на время одной строки - цафиг. 7 и. В известном устройстве зона приращений по сигналу предыдущей сроки показана на фиг. 7 и, В предлагаемом устройстве эона приращения опредг;яся5 9460 по сигналу фиг, 7 з, или по сигналу фиг. 7 и, На диаграмме фиг. 7 к показана эона приращений, которая в данном случае составляет Й 1 бит от переходов сигнала фиг.7 з; в этой зоне запрещается замещение текущего сигнала, В известном устройстве определяется несовпадение текущего сигнала с предыдущим. В предлагаемом уст- ройстве несовпадение текущего сигнала должно произойти как с сигналом, эадер о жанным на время строки, так и с сигналом, задержанным на время двух строк развертки (фиг. 7 л). Замещение текущего сигнала задержанным на время строки развертки происходит согласно сигналу 1 Б (фиг. 7 м), и на выходе заявляемого устройства вырабатывается откорректированный сигнал (фиг. 7 н), иэ которого устранен только ошибочный импульс.Изобретение позволяет повысить ка- що чество факсимильных иэображений, принятых в условиях помех, ввиду полного устранения явления удвоения ошибок, свой ственного известному устройству. формула и э о б р е т е н и я дУстройство для коррекции ошибок приемника факсимильных сигналов по авт,08 6св,613520, отличающеесятем, что, с целью повышения точностикоррекции, в него введены включенныемежду входом устройства и тактовым входом блока запоминания последовательносоединенные блок выделения фронтов, реверсивный счетчик, дешифратор, элементИ с инверсией и задержкой по одномувходу и элемент ИЛИ, причем второйвход элемента И с инверсией и задержкой по одному входу подключен к входутактовых импульсов и вычитающему входу реверсивного счетчика, вход запретакоторого соединен с выходом дещифратора, выход блока выделения фронтов - совторым входом элемента ИЛИ, первыйдополнительный выход блока запоминаниясоединен с дополнительным входом блокавыделения зон приращений, а второй - сдополнительным входом блока выделениянесовпадений. Источники информации,принятые во внимание при экспертизе 1, Авторское свидетельство СССР613520, кл. Н 04 Й 1/40, 1977

СмотретьЗаявка

3215500, 08.12.1980

ПРЕДПРИЯТИЕ ПЯ А-1221

ЛЯШЕВИЧ ВЯЧЕСЛАВ СТЕПАНОВИЧ

МПК / Метки

МПК: H04N 1/40

Метки: коррекции, ошибок, приемника, сигналов, факсимильных

Опубликовано: 23.07.1982

Код ссылки

<a href="https://patents.su/4-946008-ustrojjstvo-dlya-korrekcii-oshibok-priemnika-faksimilnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для коррекции ошибок приемника факсимильных сигналов</a>

Предыдущий патент: Демодулятор сигналов с фазоразностной модуляцией

Следующий патент: Устройство для сжатия полосы частот телевизионного сигнала

Случайный патент: Устройство для управления частотно-регулируемым электроприводом