Система для передачи и приема данныхс решающей обратной связью

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

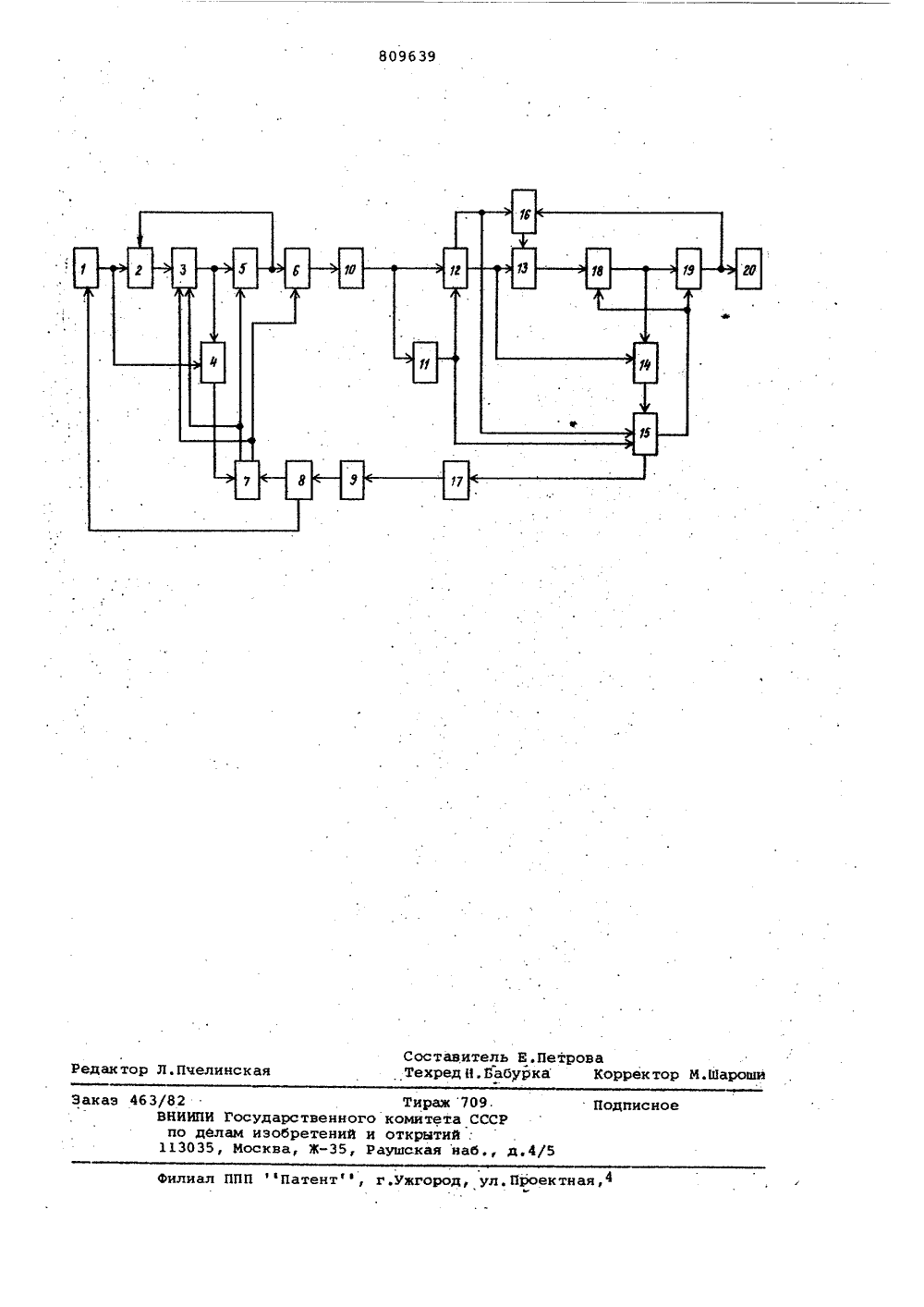

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДВПВПЬСТВУ Союз Советских(53)М. Клз Н 04 Ь 25/40Н 04 Ь 1/16 с присоединением заявки Йо - Ф Государствеииый комитет. СССР по делам изобретеиий и открытийДата опубликования описания 280281 ов, В.Н.Бойко, В.А.нко и С.В.Шпагинк В.И.Глуш.В.федо торыретенмяГ енко нз Заявнтел(54) .СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕиА ДА С РЕШММЦЕИ ОБРАТНОЙ СВЯЗЬЮ мации, при этвания сигнало чен ко входу зи 11 м выход блока фообратной связибратного канала Изобретение относитс я может использоваться, для обмена информацией междуми е к связи и организац двумя пу дклюЯи.та стная система и евысок ю помехо еттой-. и- менИзвестна система для передачи и5Однако изве ме приема данных с решающей обратной сравнительно н у ус связью, содержащая на гередающей сто- чивость.роне последовательно соединенные дат- Цель изобретения - повышение помечик информации; элемент ИЛИ, накопи" хоустойчивости.тель и элемент И, выход которого подк- Поставленная цель достигается тем, лючен ко второму входу элемента ИЛИ, . что на передающей стороне введен ком- и последовательно соединенные канал паратор, входы которого соединены с обратной связи, блок дешифрирования выходами накопителя .и датчика инфорсигналов обратной связи и блок управ" мацин, ко входу которого подключен до- ления, выход которого подключен ко. 5 полнительный выход блока дешифрировторым входам накопителя и элемента вания сигналов обратной связи, а вы- И, а.также кодирующий блок, выход ход компаратора соединен со вторым которого соединен со входом дискрет+входом блока управления, дополньггельного кайала связи; на приемной сто- ный выход которого подключен к третье- роне - декодирующий блок,.первый 20 му"входу накопителя и первому входу .вход которого соединен с выхбдом кодирующего блока, второйвход кото- дискретного канала связи, решаюп(Йй рого соединен с выходом элемента И, блок, выход которого подключен к пер- на приемной стороне введены элемент вому входу блока управления, выходЫ ИЛИ, ключ и компаратор, выход кото- которого соединены со входом блока 25 рого подключен ко второму входу блоформирования сигналов обратной связи ка управления, третий вход которого и первыми входами накопителя и эле- . соединен с первым выходом декодируюмента: И, второй вход и выход которого щего блока и первым входом ключа, соединены соответственно с выходом второй вход и выход которого соед накопителя и входом получателя инфориены соответственно с выходом элета И и первым входом элемента ИЛИ, второй вход которого соединен со вторым выходом декодирующегб блока и первым входом комаратора, ко второму входу которого подключен выход накопителя, вход которого соединен 5 с выходом элемента ИЛИ, причем второй вход декодирующего блока соединен с выходом рещающего блока.На чертеже приведена структурнаяэлектрическая схема предлагаемой сис О темы.Система для передачи и приема данных с решающей обратной связью содержит на передающей стороне датчик 1 информации, элемент 2 ИЛИ, накопитель 3, компаратор 4, элемент 5 И, кодирующий блок 6, блок 7 управления, блок 8 дешифрирования сигнаяов обратной связи, канал 9 обратной связи, дискретный канал 10 связи, а на приемной стороне - решающий блок 11, деко дирующий блок 12, элемент 13 ИЛИ, компаратор 14, блок 15 управления, ключ 16, блок 17 формирования сигналов обратной связи, накопитель 18 элемент 19 И и получатель 20 инфор мацин.Система работает следующим образом.Сообщения от датчика 1 поступают на первый вход элемента 2 ИЛИ и с его выхода - на первый вход накопителя З.Сообщение, поступающее в накопитель З,сдвигает на его выход нулевую (если до этого момента информация в нем отсутствовала) инФормацию, которая приходит на входы компаратора 4 и элемента 5 И.Одновременно на другой вход компаратора 4 с выхода датчика 1 поступает первое сообщение. В результате сравнения компаратор 4 вырабатывает сиг нал несовпадение, поступающий на. второй вход блока 7, Блок 7 по этому сигналу разрешает прохождение первого сообщения из накопителя 3 через эле.мент 5 И в кодирующий блок 6 и через элемент 2 ИЛИ на вход накопителя 3 для перезаписи, Кодирующий блок б преобразует сообщение в кодовую комбинацию, которая поступает в дискретныйканал 10. С выхода дискретного канала 5010 кодовая комбинация поступает на входы декодирующего блока 12 и решающего блока 11. Решающий блок 11 вы-, рабатывает сигналы Верноф илн Неверно, поступающие на первый вход блока 15 и на второй вход декодирующего блока 12.По сигналу фНеверно декодирующий блок 12 стирает принятую кодовую комбинацию, а блок 15 выдает в блок ф) 17 сигнал на формирование и выдачу. в канал 9 комбинации Запросф. Последняя поступает на вход блока 8, с выхода которого сигнал 1 Запрос поступает на вход блока 7, Блок 7 б 5 по сигналу Запрос разрешает повторное прохождение первого сообщенияиз накопителя 3 через соответствующие узлы системы в дискретный канал10.По сигналу Верноф со второговыхода декодирующего блока 12 декодированное сообщение через элемент13 ИЛИ поступает в накопитель 18 ина первый вход компаратора 14. Одновременно на первом выходе декодирующего блока 12 появляетоя сигнал, кото"рый открывает ключ 16, а также поступает на третий вход блока 15,Если до этого момента информацияв накопителе 18 отсутствует, то в результате сравнения на выходе компаратора 14 появляется сигнал Несовпадениеф, который поступает на второй вход блока .15. Последний разрешает по этому сигналу прохождениепервого сообщения через элемент 19 Ик получателю 20 и через ключ 16 и элемент 13 ИЛИ - на перезапись в накопитель 18По сумме сигналов Верно иНесовпадение блоК 15 выдает вблок 17 сигнал на формирование комбинации Подтверждение, которая через канал 9 принимается блоком 8, Свыхода блока 8 сигнал Подтверждениеф поступает в датчик 1, разрешаявыдачу второго сообщения. Второе сообщение выдвигает на вход компаратора4 первое сообщение из накопителя 3в то время, как на другой вход компаратора 4 посТупает второе сообщение непосредственно из датчика 1.Если второе сообщение одинаковое спервым, на выходе компаратора 4, аследовательно, и на втором входе блока 7, появляется сигнал "Совпадениеф,по которому на дополнительном выходе блока 7 формируется сигнал на стирание информации в накопителе 3 и формирование в кодирующем блоке б спе- .циальной кодовой комбинации х изчисла размещенных. Последняя, аналогично предыдущей кодовой комбинации,через дискретный канал 10 поступаетна входы решающего 11 и декодирующего 12 блоков.Таким образом, в результате выдачидатчиком 1 подряд двух одинаковых сообщений в дискретный канал 10 не посылаются подряд две одинаковые кодовые комбинации.Решающий блок 11 и декодирующийблок 12 обрабатывает полученную кодовую комбинацию Х. Если решающийблок 11 выдает сигнал Неверно,то работа системы аналогична ранеерассмотренной ее работе по сигналуНеверно, Если решающий блок 11выдает сигнал Верно, а декодирующий блок 12 выдает сигнал о приемекомбинации Х, то на первом выходедекодирующего блока 12 возникает сигнал, соответствующий сообщению Х,809639 по которому ключ 16 закрывается. Второй выход декодирующего блока 12 посообщению Х остается закрытым. Посигналам Верно и Х блок 15 разрешает прохождение записанного первогосообщения иэ накопителя 18 черезэлемент 19 И получателю 20, Так какключ 16 при этом закрыт, то перезапись информации в накопитель 18 непроисходит. Сигнал ПодтверждениеФормируется и выдается в канал 9 и 1 Ообрабатывается на передающей сторонетак же, как и в рассмотренном вышеслучае. Формула изобре,тения Таким образом, в результате выдачи получателю 20 второго сообщенйя 35 одинакового с первым, приемная часть системы находится в том же состоянии, что и перед выдачей первого сообщения. Если в дальнейшем датчиком 1 выдается третье сообщение, то оно обрабатывает-Щ ся так же,. как и первое, а четвертое, если оно одинаково с третьим, обрабатывается как и второе, и т.д. Любое отличное от предыдущего сообщение обрабатывается, как и первое сообщение . дПри трансформации сигнала .Подтверждение в Запрос с передающей стороны повторно посылается ранее выданная кодовая комбинация,При этом на :;.ервый и второй входы компаратора 14 : оступают одинаковые сообщения и он ь:.сдает в блок 15 сигнал Совпадение. Из решающего блока 11 поступает сюда же сигнал Верно. По этим сигналам блок 15 выдает в блок 17 сигнал на выдачу сигнала подтверж- З 5 дение. На вторые входы накопителя 18.и элемента 19 И сигнал не подается, и сообщение в получатель 20 не поступает, 40 т.е. вставка информации исключается.Предлагаемая система для передачи и приема данных обладает высокой эффективностью, так как при ее испольэовании вероятность ошибочного приема 4 э уменьшается на несколько порядков. Система для передачи и приема данных с решающей обратной связью, содержащая на передающей стороне после" довательно соединенные датчик информации, элемент ИЛИ, накопитель и эле мент И, выход которого подключен ко второму входу элемента ИЛИ, и последовательно соединенные канал обратнойсвязи, блок дешифрирования сигналовобратной связи и блок управления, вы"ход которого подключен ко вторым входам накопителя и элемента И, а такжекодирующий блок, выход которого соединен со входом дискретного каналасвязи; на приемной стороне - декодирующий блок, первый вход которого соединен с выходом дискретного каналасвязи, рещающий блок, выход которогоподключен к первому входу блока управления, выходы которого соединенысо входом блока Формирования сигна-лов обратной связи и первыми входаминакопителя и элемента И, второй входи выход которого соедийены соответственно с выходом накопителя и входомполучателя информации, при этом выход блока формирования сигналов обратной связи подключен ко входу обратного канала связи, о т л и ч а ющ а я с я тем, что, с целью повышения помехоустойчивости, в нее на передающей стороне введен компаратор, входы которого соединены с выходами накопителя и датчика информации, ковходу которого подключен дополнительный выход блока дешифрирования сигналов обратной связи, а выход компаратора соединен со вторым входом блока управления, дополнительный выходкоторого подключен к третьему входунакопителя и первому входу кодирующего блока, второй вход которого соединен с выходом элемента И; на приемной стороне введены элемент ИЛИ, ключи компаратор, выход которого подключен ко второму входу блока управления,третий вход которого соединен с первым выходом декодирующего блока ипервым входом ключа, второй вход ивыход которого соединены соответственно с выходом элемента И и первымвходом элемента ИЛИ, второй вход которого соединен со вторым выходом декодирующего блока и первым входомкомпаратора, ко второму входу которого подключен выход накопителя, входкоторого соединен с выходом элемента ИЛИ,причем второй вход декодирующего блока соединен с выходом решающего блока.Источники информации,принятые во внимание при экспертизе1. Пуртов.Л.П. Элементы теории передачи дискретной информации, И.,Связьф, 1972 с .161-167, 185-191809639 Составитель Е.Петроватор Л.Пчелинская Техред Н. Бабурка Коррек тот Эак Подписи д,4/ илиал ппппатентф ф, г.ужгород, ул, проектная,4ъ 63/82 ВНИИПИ Росударственн по дЕлам изобретены 113035, Москва, Ж

СмотретьЗаявка

2755157, 13.04.1979

ПРЕДПРИЯТИЕ ПЯ М-5156

АНДРУЩЕНКО АНАТОЛИЙ ГРИГОРЬЕВИЧ, ГЛУШКОВ ВАЛЕРИЙ ИВАНОВИЧ, БОЙКО ВЯЧЕСЛАВ НИКОЛАЕВИЧ, ГАВРИЛОВ ВЛАДИМИР АЛЕКСАНДРОВИЧ, ФЕДОРЕНКО ВЛАДИМИР ВАСИЛЬЕВИЧ, ШПАГИН СЕРГЕЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: H04L 25/40

Метки: данныхс, обратной, передачи, приема, решающей, связью

Опубликовано: 28.02.1981

Код ссылки

<a href="https://patents.su/4-809639-sistema-dlya-peredachi-i-priema-dannykhs-reshayushhejj-obratnojj-svyazyu.html" target="_blank" rel="follow" title="База патентов СССР">Система для передачи и приема данныхс решающей обратной связью</a>

Предыдущий патент: Устройство для передачи цифровыхданных по магистральным линиямсвязи

Следующий патент: Устройство автоматического включениярегистрирующей аппаратуры b линияхсвязи c частотной модуляцией

Случайный патент: Ротор явнополюсного синхронного двигателя