Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

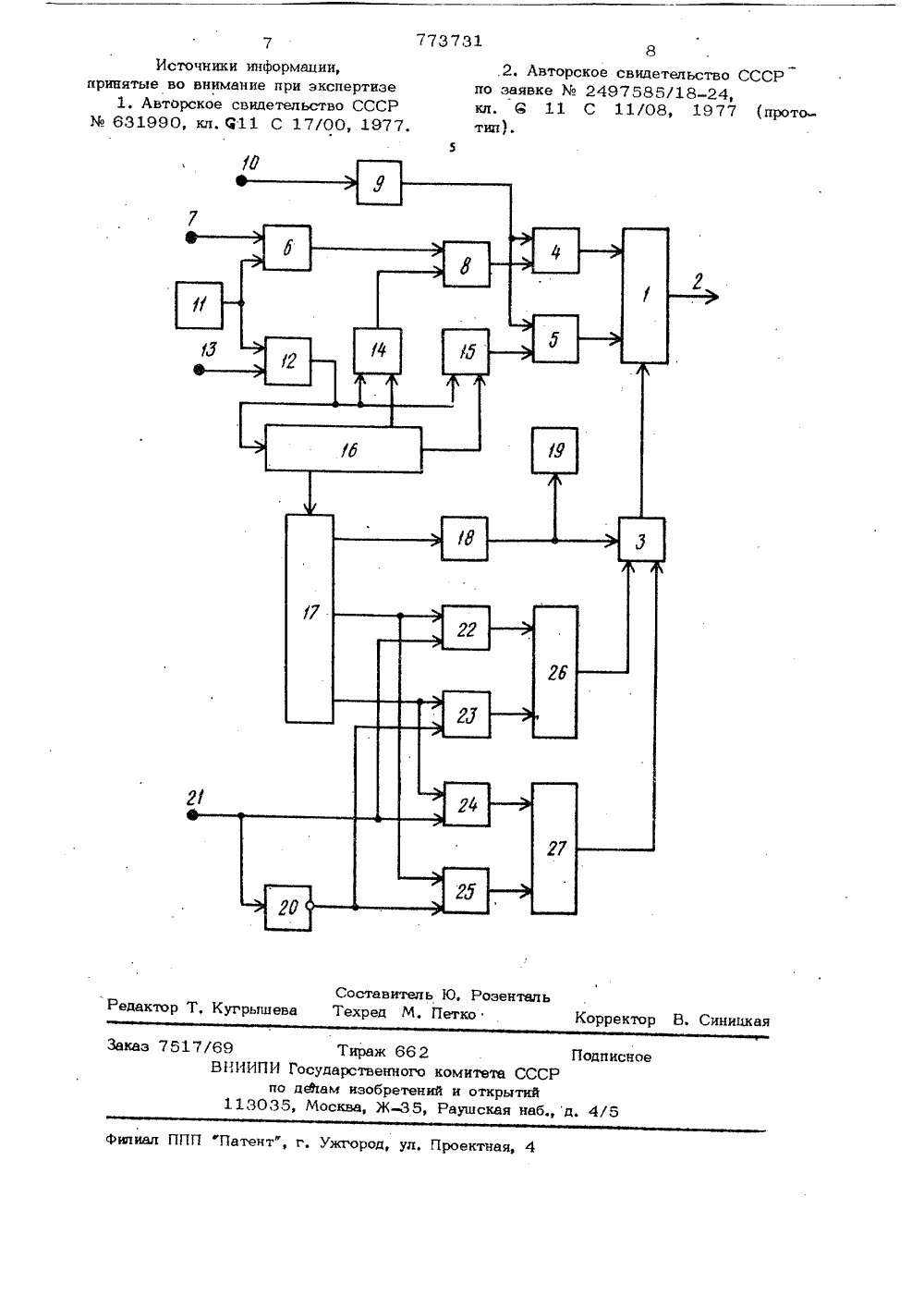

СОюз СоветскинСоциалистическимиРеспублик ОП ИКАНИЕИ,ЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(23) Приоритет -Опубликовано 23. 10.80 Бюллетень Рй 39 ао делен нзобретеннй н атерытнй(53) УДК 681. ,327.66. (088.8) Дата опубликования описания 02,11,80(72) . Авторы изобретения И. В. Гольдберг, В. С. Кулакова, Н. С. Ежо й Я.-44 Будовскийфе т 1) Заявите 54) ЗАПОМИНАЮШЕЕ УСТРОЙСТВО ТИПА 2 Д С НЕРАЗРУШАЮШИМСЧИТЫВАНИЕМ ИНФОРМАЦИИ НА МНОГООЧВЕРСТНЫХфЕРРИТОВЫХ ЭЛЕМЕНТАХ с- счиИзобретение относится к вычислительной технике и может быть использовано при построении устройств хранения ди кретной информации с неразрушающим тыванием.5Известно ЗУ типа 2 Д с неразрушающим считыванием информации на многоотверстных ферритовых элементах (МЭф), содер жащее накопитель, формирователи токов записи и считывания, генераторы импулвсов и логические элементы 11.Недостатком этого ЗУ является невысокая надежность.Наиболее близким по технической сущности к изобретению является ЗУ.типа 2 Д 15 с неразрушающим считыванием информации на МфЭ, которое содержит накопитель, первый вход которого соединен с выходом формирователя разрядных токов записи, второй вход - с выходом формирователя 20 адресных токов .записи, а третий вход - с выходом формирователя адресных токов считыванчя, первый вход которого соединен ,с выходом дешифратора адреса, а второйс выходом первого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, третий элемент И, выход которого соединен со вторым входом формирователя адресных токов записи, первый вход которого подключен к выходу дешифратора адреса, генератор импульсов, подключенный к первым входам первого и четвертого элементов И, счетчик тактов, вход которого соединен с выходом четвертого элемента И и с первыми входами второго и третьего элементов И, а первый, второй и третий выходы, подключены соответственно, ко вторым входам второго и третьего элемента И и входу дешифратора тактов, пятыйшестой и седьмой элементы И, второй элемент ИЛИ 2).Недостатком такого устройства является большое время цикла записи,так, как, в цикле записи производится воздействие на ферритовые элементы адресным током считывания последовательно по всем адресам массива накопителя,7737 охваченного одной разрядной шиной за 15 40 писи.Цель изобретения - повышение быстродействия известного ЗУ типа 2 Д с неразрушаюшим считыванием информа 5 ции на МФЭ.Поставленная цель достигается тем, что устройство содержит третий элемент ИЛИ, восьмой элемент И, элемент НЕ, ключ и блок накопителей энергии, первый выход дещифратора тактов подключен к управляющему входу ключа, выход которого подключен к первому входу формирователя разрядных токов записи и блоку накопителей энергии, а второй и третий выходы дещифрвтора тактов подключены к первым входам пятого, восьмого и шестого, седьмого эле ментов И соответственно, вторые входы шестого и восьмогс элементов И подключены к выходу элемента НЕ, вход которого соединен со вторыми входами пятого и седьмого элементов И, выходы пятого и шестого элементов И подключены соответственно к первому и второму входам второго элемента ИЛИ, выход которого соединен со вторым входом формирователя разрядных токов, третий вход которого подключен к выходу третьего элемента ИЛИ, а первый и второй входы третьего элемента ИЛИ подключены к выходам седьмого и восьмого элементов И соответственно.На чертеже изображена блок-схема предлагаемого ЗУ.Устройство содержит накопитель 1, выходные числовые шины,2, формирователь 3 разрядных токов записи, формирователь 4 адресных токов считывания и формирователь 5 адресных токов записи, первый элемент И 6, управляющую шину "Считывание 7, первый элемент ИЛИ 8, дешифратор 9 адреса, входные адресные шины 10, генератор 11 импульсов, четвертый элемент И 12, управляюцую шину Запись 13, второй элемент 45 И 14, третий элемент И 15, счетчик 16 тактов, дешифратор 17 тактов, ключ 18, блок 19 накопителей энергии (например конденсатор) элемент НЕ 20, входные" числовые шины 21, пятый 22, шестой 23,50 седьмой 24 и восьмой 25 элементы И, второй 26 и третий 27 элементы ИЛИ.Работа устройства происходит следуюцим образом.В режиме считывания инюрмвции при наличии на управляющей шине Считывание" 7 рвзрецвющего потенциала синхроимпульс с генератора 11 импульсов чепез 31первый элемент И 6 и первый элементИЛИ 8 поступает нв вход формирователя4 адресных токов считывания, выбранногодешифратора 9 адреса, в соответствии скодом адреса на шинах адреса 10, В результате, по избранной координате накопителя 1 протекает ток считывания; ина выходных числовых шинах 2 вырабатывается код считанного числа,В режиме записи информации на управляющей шине "Запись" 13 имеется разрешающий потенциал и синхроимпульс с генератора 11 поступает через четвертыйэлемент И 12 на вход счетчика 26 тактов,второй 14 и третий 15 элементы И. Вторые входывторого 14 и третьего 15 элементов И управляются счетчиком 16 такимобразом, что в течение определенного времени синхроимпульс поочередно проходитчерез один из этих элементов И, а, следовательно, поочередно срабатывают формирователи адресных токов записй 5 и считывания 4,Одновременно с этим, дешифратор 17тактов, опирающийся на счетчик 16 тактов, выдает нв первом выходе сигналвключения ключа 18 который подает питание на формирователи 3 разрядных токови заряжает блок 19 накопителей энергии,кроме того, в это время дешифратор 17тактов на своем втором выходе выдаетопрос на пятый 22 и восьмой 25 элементы И, Код числа, присутствуюший на числовых шинах 21, или его инверсия на выходе элемента НЕ 20 разрешает прохождение опроса через пятый 22 или восьмой25 элемент И, затем через второй 26или третий 25 элемент ИЛИ опрос поступает на второй или третий входы формирователя 3 разрядных токов, обеспечиваяформирование соответствующей полярностиразрядного тока накопителя 1,В результате, по разрядным шинам накопителя 1 протекают токи, направлениекаждого из которых соответствует значению кода соответствуюшего разряда числовых шин 21, а по выбранной координатной шине накопителя 1 протекают разиополярные координатные токи, обеспечивая необходимые изменения магнитныхсостояний запоминающих элементов, т.е,происходит зались информации по выбранному адресу. Необходимое для этого время отсчитывается счетчиком 16 тактов,который при достижении определенной кодовой комбинации запрещает прохождениесинхроимпульсов через второй 14 и третий 15 элементы И, звпреп 1 ая тем с мым773731 Формула изобретен ия 5срабатывание формирователей адресных токов считывания 4 и записи 5, Одновременно дешифратор 17 ртов снимает сигнал включения на ключ 18, выдает опрос на своем третьем выходе и снимает опрос со второго выхода. В соответствии с кодом числа на шинах 21 или его инверсии 20, открывается шестой 23 или седьмой 24 элементы И и опрос с дещифратора 17 через третий 27 или второй 26 эле- щ мент ИЛИ поступает на третий или второй вход формирователя 3 разрядных токов, обеспечивая противоположную полярность разрядного тока. В следующий момент времени дешифратор 17 тактов сно ва выдает опрос на своем втором выходе, снимая его с третьего выхода, и так далее, до достижения заданного количества (3 - 7) в зависимости от типа запоминающего элемента раэнополярных импульсов разрядного, тока. Так, как; при прохождении этой пачки разрядных токовых импульсов ключ 18 отключен, амплитуда разрядных токов в пачке определяется потенциалом накопленной энергии в блоке 25 19. (например на конденсаторе), который снижается до нуля по мере расхода энергии при прохождении этих токов. Таким образом, происходит нормализация состояний запоминающих элементов по всем разрядам и адресам, что обеспечивает стабильность выходных сигналов накопителя по первому после цикла записи обращению к любому адресу в ре 35 жиме считывания, кроме выбранного при записи.В последующий промежуток времени, который также определяется кодовой комбинацией счетчика 16 производится известная нормализация магнитного состояния запоминающих элементов выбранного при записи адреса, воздействием на избранную координату накопителя 1 нескацьких токов считывания, путем подачи не скольких опросов со счетчика 16 через второй элемент И 14, первый элемент ИЛИ 8 на формирователь 4 адресных токов считывания. 50На этом цикл записи заканчивается, Предлагаемое запоминающее устройство отличается от известного устройства типа 2 Л ца многоотверстных ферритовых элементах, имеющего стабипь ные параметры выходных сигналов накопителя, существенно меньшим временем цикла записи, что расширяет область применения подобных запоминающих устройств. Запоминающее устройство типа 2 Д с пераэрушающим считыванием информации на многоотверстных ферритовых элементах, содержащее накопитель, первый вход ко- .торого соединен с выходом формирователя разрядных токов записи, второй вход - с выходом формирователя адресных токов записиа третий вход - с выходом формирователя адресных токов считывания, первый вход которого соединен с выходом дещифратора адреса, а второй - с выходом . первого элемента ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и втрого элемента И, третий элемент И, выход которого соединен со вторым входом формирователя адресных токов записи, первый вход которого подключен к выходу дешифратора адреса, генератор импульсов, подключенный к первым входам первого и четвертого элементов И, счетчик тактов, вход которого соединен с выходом четвертого элемента И и с первыми входами второго и третьего элементов И, а первый, второй и третий выходы, подключены соответственно, ко вторым входам второго и третьего элемента И и входу дещифратора тактов, пятый, шестой и седьмой элементы И, второй элемент ИЛИ, о т л и ч а ю щ е е с я тем, что, с целью повышения быстродействия запоминающего устройства, оно содержит третий элемент ИЛИ, восьмой элемент И, элемент НЕ, ключ и блок накопителей энергии, первый выход дешифратора тактов подключен к управляющему входу ключа, выход которого подключен к первому входу формирователя разрядных токов записи и блоку накопителей энергии,. а второйитретийвыходы дешпфратора тактов подключены к первым входам пятого, восьмого и шестого, седьмого элементов И соответственно, вторые входы шестого и восьмого элементов И подключены к выходу элемента НЕ, вход которого соединен со вторыми входами пятого и седьмого элементов И, выходы пятого и шестого элементов И подключены соответственно к первому и второму входам второго элемента ИЛИ, выход которого соединен со вторым входом формирователя разрядных токов, третий вход которого подключен к выходу третьего элемента ИЛИ, а первый и второй входы третьего элемента ИЛ И подключены я выходам седьмого и восьмого элементов И соответственно.773731 Составитель Ю. РозенталКугрышева Техред М. Петко Корректо Редактор Синицка 7517/69ВНИИ писн и откаушска д. 4/ иал ППП Патент", г. Ужгород, ул, Проектная, 4 Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССРТираж 662 ПИ Государственного по дФам изобретений 3035, Москва, Ж, 82. Авторское свидетельство СССР по заявке И 2497585/18-24,кл. Я 11 С 11/08, 1977 (прототип) .

СмотретьЗаявка

2751954, 12.04.1979

ПРЕДПРИЯТИЕ ПЯ Г-4152

ГОЛЬДБЕРГ ИКАР ВЕНИАМИНОВИЧ, КУЛАКОВА ВАЛЕНТИНА СЕРГЕЕВНА, ЕЖОВА НИНА СЕРГЕЕВНА, БУДОВСКИЙ ЯКОВ МОИСЕЕВИЧ

МПК / Метки

МПК: G11C 17/00

Метки: запоминающее, информации, многоотверстных, неразрушающим, считыванием, типа, ферритовых, элементах

Опубликовано: 23.10.1980

Код ссылки

<a href="https://patents.su/4-773731-zapominayushhee-ustrojjstvo-tipa-2d-s-nerazrushayushhim-schityvaniem-informacii-na-mnogootverstnykh-ferritovykh-ehlementakh.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство типа 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах</a>

Предыдущий патент: Ассоциативное запоминающее устройство

Следующий патент: Аналоговое запоминающее устройство

Случайный патент: Устройство для подключения абонентов к общей магистрали