Система обработки данных

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 748433

Авторы: Абражевич, Витер, Овсянников, Шевченко

Текст

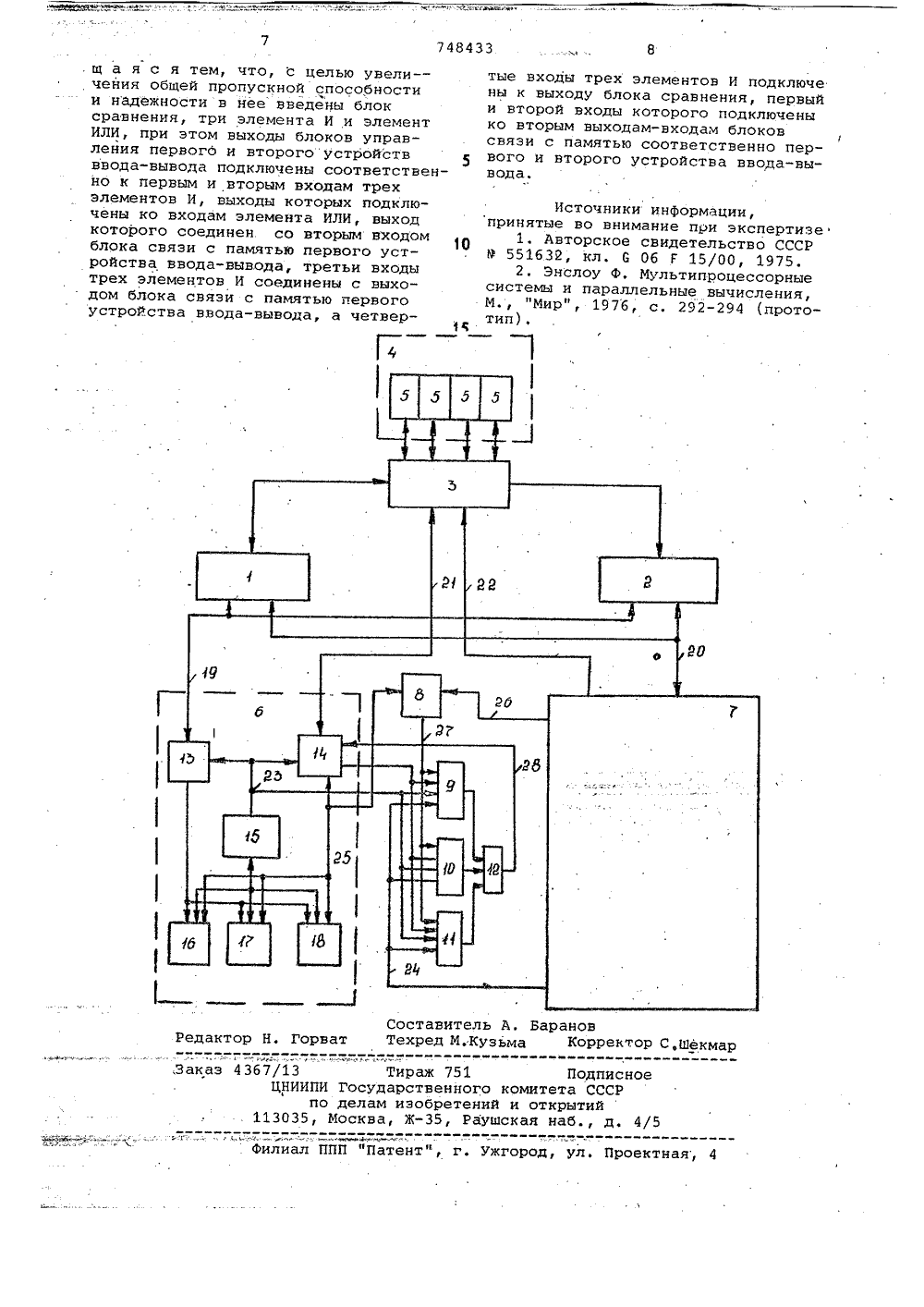

Союз Советских Социалистических Республик(61) Дополнительное к авт, свид-ву(22) Заявлено 280678 (21) 2635230/18-24с присоединением заявки Нов(51)М. Кл.2 С 06 Г 15/00 Государственный комитет СССР по делам изобретений и открытий(54) СИСТЕМА ОБРАБОТКИ ДАННЫХ Изобретение относится к вычислительной технике и может быть использовано при проектировании мультипроцессорных вычислительных систем.Известна система обработки .данных, 5содержащая модули центральных процессоров,.модули ввода-вывода, адресныевыходы и информационные входы и выходы которых подключены к входам и вы-ходам общего поля оперативной памяти И 7.Недостатком такой системы обработки данныхявляется то, что при работе с общей оперативной памятью закаждым модулем ввода-вывода и центрального процессора закреплен жесткий приоритет обслуживания его запросов на память независимо от видазайроса и, следовательно, при большой загрузке модулей ввода-вывода 20возможно переполнение одного из ме "нее приоритетных модулей ввода-вы"вода,Наиболее близким техническим ре.шением к предлагаемой системе являет ся система обработки данных, содержащая первый и второй процессоры,первые входы и выходы которых подключены к первым и вторым входам и выходам блока распределителя сигналов, 30,2третьи, и четвертые входы и выхбды которого подключены к первым входам и выходам"первого"и "второго"модуля ввода-вывода, вторые входы и выходы которых подключены ко вторым и третьим входам и выходам первого и вто- рого процессоров, а пятые входы и вйходы блока распределителя сигналов подключены к входам и выходам общего блока оперативной памяти (21 .Недостатком такой системы обработки данных является сравнительно невысокая надежность системы ввода- вывода при.большой загрузке системы ввода-вывода, так как приоритет при одновременном обращении к одйому блоку оперативной памяти присвоен по жесткому принципу: первому модулю ввода-вывода " самый высокий далее второму модулю ввода-вывода, первому центральному процессору, второму центральному процессору, так как каждый модуль ввода-вывода содержит два селекторных и мультиплексный канал, причем к первому селекторному каналу подключены высокоскоростные внешние устройства типа накопителя на магнитных дисках, ко-" вторб-", му селекторному каналу накопителя на магнитных лентах, а к мультиплексному каналу сравнительно медленнодей ствующие внешние устройства, то большая загрузка вводом-выводом менее скоростных второго селекторного и мультиплексного каналов первого модуля внода-выводаможет вызвать переполнение селекторных каналов второго модуля ввода-вывода, следо- вательнО, надежность системы ввода- вывода данной системы обработки дан. - . ных недостаточно высока.Цель изобретения - увеличение общей пропускной способности и надежности обработки системы данных.Поставленная цель достигается тем, что в систему обработки данных, содержащУю два процессора, блок памяти, распределитель сигналов, дна устройства ввода-вывода, каждое из которых содержит два селекторных канала, один мультиплексный канал, блок управления, блок связи с процессором, блок связи с памятью, при этом входы-выходы распределителя сигналов подключены к соответствующим выходам-нходам блока памяти, первый и второй вход-выход распределителя сигналов соединен с первыми выходами-входами блоков связи с памятью соответственно первого и второго устройств ввода-вывода, а третий и четвертый входы-выходы распределителя сигналов соединены с первыми выходами-входами соответственно первого и второго процессоров, первые входы-выходы обоих процессоров подключены к первому выходу-входу блока связи с процессором первого устройства ввода-вывода, вторые входы- . выходы обоих процессоров соединены с первым выходом-входом блока связи с процессором второго устройства ввода-вывода, вторые входы-выходы блоковсвязи с процессором каждого устройства ввода-вывода соединены с первыми выходами-входами двух селекторного и одного мультиплексного каналов соответствующего устройства ввода-нывода, вторые входы-выходы двух селекторных и одного мультиплексного каналов каждого устройства ввода-вывода подключены к выходу-входу блока управления соответствующего устройства ввода-вывода, третьи входы-выходы двух селектор ных и одного мультиплексного каналов каждого устройства ввода-вывода соединены со вторИм выходом-входомблока связи с памяти соответствующего устройства ввода-вывода, выход блока сравнения каждого из устройствввода-вывода соединен со входом блока связи с процессором и первым входом блока связи с памятью соответствующих устройств ввода-вывода, введены блок сравнения, три элемента Ии элемент ИЛИ, при этом выходы блоков управления первого и второго устройств ввода-вывода подключены1 О ветственно первого и второго устройства ввода-вывода.15 На чертеЖе представлена структу 20 25 30 35 40 45 50 55 60 б 5 соответственно к первым и вторымвходам трех элементов И, выходы которых подключены ко входам элемента ИЛИ, выход которого соединен совторым входом блока связи с памятью первого устройства ввода-вывода,третьи входы трех элементов И соединены с выходом блока связи с памятью первого устройства ввода-вывода, а четвертые входы трех элементов И подключены к выходу блокасравнения, первый и второй входы которого подключены ко вторым выходамвходам блоков связи с памятью соотра системы обработки данных, содержащая первый процессор 1, второйпроцессор 2, распределитель 3 сигналов, блок 4 памяти, содержащую модули .5, первое устройство б вводавывода, второе устройство 7 ввода-вывода, блок 8 сравнения устройств, элементы И 9, 10, 11, ИЛИ 12.Каждый из устройств б, 7 ввода- вывода содержит блок 13 связи с процессором, блок 14 связи с оперативной памятью, блок 15 управления, первый селекторный 16, второй селекторный 17 и мультиплексный 18 канала ввода-вывода.Операция ввода-вывода в канале 16 (17, 18) осуществляется под управлением текущего управляющего слова канала, расположеннрго непосредственно в канале и содержащего всю необходимую информацию для передачи данных: код выполняемой команды, адрес данных, счетчик количества передаваемых байтов и специальные флажки.Ряд управляющих слов канала составляют канальную программу, которая первоначально хранится в блоке 4 памяти. Первое управляющее слово канала извлекается из блока 4 памяти по специальной инструкции процессора 1 (2), которая задает адрес устройства б (7) ввода-вывода, адрес канала 16 (17, 18) и внешнего устройства (последние на чертеже не показаны). Инструкция процессора поступает в устройство 6 (7) ввода-вывода через шины 19 (20) процессора, блок 13 связи с процессором. Получив инструкцию, устройства ввода-вывода освобождают процессор 1 (2) для вйполнения дальнейших инструкций и выбирают иэ блока 4 памяти управляющее слово канала через распределитель 3 сигналов, шины 21 (22) памяти, блок 14 связи с памятью, после чего выбирают внешнее устройство (на чертеже. не показано) и запускают операцию ввода-вывода.После запуска операции нвода-вы-. вода, устройство нвода-вывода настр,.;ивается на передачу данных, т.е.при необходимости каналу 16 (17, 18)принять или передать байт (группубайтов) данных он устанавливаетзапрос на память, поступающий в блок15 управления. Этот блок устанавливает приоритет в работе каналов 16(17, 18), причем при одновременномпоступлении запросов на память изканалов устанавливается следующийприоритет: первый селекторный канал;второй селекторный канал, мультиплексный канал,Сигнал запроса на память выбранного канала 16 (17, 18) поступаетчерез запросные шины 23 (24) памяти, в блок 14 связи с памятью и наэлементы И 9, 10, 11, Одновременнос сигналомзапроса на память, выбранный канал передает на адреснйешины 25 (26) памяти адрес блокапамяти, поступающие в блок 14 связи с памятью и блок 8 сравнения,Если оба устройства 6 (7) вводавывода пытаются обратиться к одномуузлу 5 блока памяти, т,е, адресаданных равны, то на выходе блока 8 25сравнения возбуждается сигнал 27сравнения, поступающий на элементыИ 9, 10, 11. Элементы И 9, 10, 11срабатывают в случае, еслиадреса сравнились, первое устройство 6 установило запрос от второго селекторного 17 канала, второе устройство 7 установило запрос первого селекторного канала и в данный моментвремени первое устройство 6 не рабо- З 5тает с блоком памяти (элемент И 9);адреса сравнились, первое устройство 6 установило запрос от мультиплексного 18 канала, второе устройство7 установило запрос второго селекторного канала и в данный момент времени первое устройство.6 не работаетс блоком памяти (элемент И 10),адреса сравнились, первое устройство6 установило запрос от мультиплексного 18 канала, второе устройство установило запрос от первого селекторного канала и в данный момент временипервое устройство 6 не работает сблоком памяти (элемент И 11),Если обращается менее приоритетный канал 17 (18) первого устройства 6 ввода-вывода и более приоритетный канал 16 (17) второго устройства 7 ввода-вывода к одному узлу 5 блока 55 4 памяти, то срабатывает один из элементов И 9, 10, 11, выходы которых .через элемент ЙЛИ 12 поступают на шину 28 блокировки запроса на память первого устройства, по которому блок 60 14 связи с памятью запрещает формирование сигнала запроса на память первого устройства 6 ввода-вывода. Таким образом распределитель 3 сигналов получает только запрос на память от 5 второго устройства 7 ввода-вывода ипервым его обслужит.Если же устройства 6 (7) вводавывода обращаются к разным узлам 5блока памяти 4, то блок 8 сравненияне срабатывает и сигнал 28 блокировки запроса на память первого устройства ввода-вывода отсутствует,так как распределитель 3 сигналов обслуживает одновременно два процессора 1, 2 и два устройства 6, 7 вводавывода, работающих с разными узлами5 блока 4 памяти,Формула изобретенияСистема обработки данных, содержащая два процессора, блок памяти, распределитель сигналов, два устройства ввода-вывода, каждое из которых содержит два селекторных канала, один мультиплексный канал, блок управления, блок связи с процессором, блок связи с памятью, при этом входы-выходы распределителя сигналов подключены к соответствующим выходам- входам блока памяти, первый и второй вход-выход распределителя сигналов соединен с первыми выходами-входами блоков связи с памятью соответственно первого и второго устройства ввода-вывода, а третий и четвертый входы-выходы распределителя сигналов соединены с первыми выходами-входами соответственно первого и второго процессоров, первые входы-выходы обоих процессоров подключены к первому выходу-входу блока связи с процессором первого устройства ввода-вывода, вторые входы-выходы обоих процессоров соединены с первым выходом-входом блока связи с процессором второго устройства ввода-вывода, вторые входы-ьыходы блоков связи с процессором каждого устройства ввода-вывода соединены с первыми выходами-входами двух селекторного и одного мультиплексного. каналов соответствующего устройства ввода-вывода, вторые входы- выходы двух селекторных и одного мультиплексного каналов каждого устройства ввода-вывода подключены к выходу-входу блока управления соответствующего устройства вводавыводау третьи входы-выходы двух селекторных и одного мультиплексного каналов каждого устройства ввода-вывода соединены со вторым выходом-входом блока связи с памяти со-, ответствующего устройства ввода- вывода, выход блока сравнения каж-. дого из устройств ввода-вывода соединен со входом блока связи с процессором и первым входом блока связи с памятью соответствующих устройств ввода-вывода, о т л и ч а ю"Тираж 751 ПИ Государственного по делам изобретениМосква, Ж, Рау Подписноомитета СССРи открытийкая наб., д. 4 11303 Филиал ППП "Патент", г. Ужгород, ул. Проект 4.щ а я с я тем, что, с целью увели чения общей пропускной способностиь,и надежности в нее введены блок сравнения, три элемента И и элемент ИЛИ, при этом выходы блоков управления первого и второго устройств ввода-вывода подключены соответственно к первым и вторым входам трех элементов И, выходы которых подключены ко входам элемента ИЛИ, выход которого соединен со вторым входом блока связи с память 1 о первого устройства ввода-вывода, третьи входы трех элементов И соединены с выходом блока связи с памятью первого устройства ввода-вывода, а четвертые входы трех элементов И подключены к выходу блока сравнения, первыйи второй входы которого подключеныко вторым выходам-входам блоковсвязи с памятью соответственно первого и второго устройства ввода-вывода. Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 551632, кл. О 06 Г 15/00, 1975,2. Энслоу Ф, Мультипроцессорныесистемы и параллельные вычисления,М., "Мир", 1976, с, 292-294 (прототип),

СмотретьЗаявка

2635230, 28.06.1978

ПРЕДПРИЯТИЕ ПЯ М-5339

АБРАЖЕВИЧ РЕМУАЛЬД ИГНАТЬЕВИЧ, ВИТЕР ВЛАДИМИР ВАСИЛЬЕВИЧ, ОВСЯННИКОВ ВАЛЕРИЙ ИВАНОВИЧ, ШЕВЧЕНКО ТАРАС ГРИГОРЬЕВИЧ

МПК / Метки

МПК: G06F 15/00

Метки: данных

Опубликовано: 15.07.1980

Код ссылки

<a href="https://patents.su/4-748433-sistema-obrabotki-dannykh.html" target="_blank" rel="follow" title="База патентов СССР">Система обработки данных</a>

Предыдущий патент: Устройство для ввода-вывода информации

Следующий патент: Цифровой функциональный преобразователь

Случайный патент: 418802