Устройство для ввода информации от дискретных датчиков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

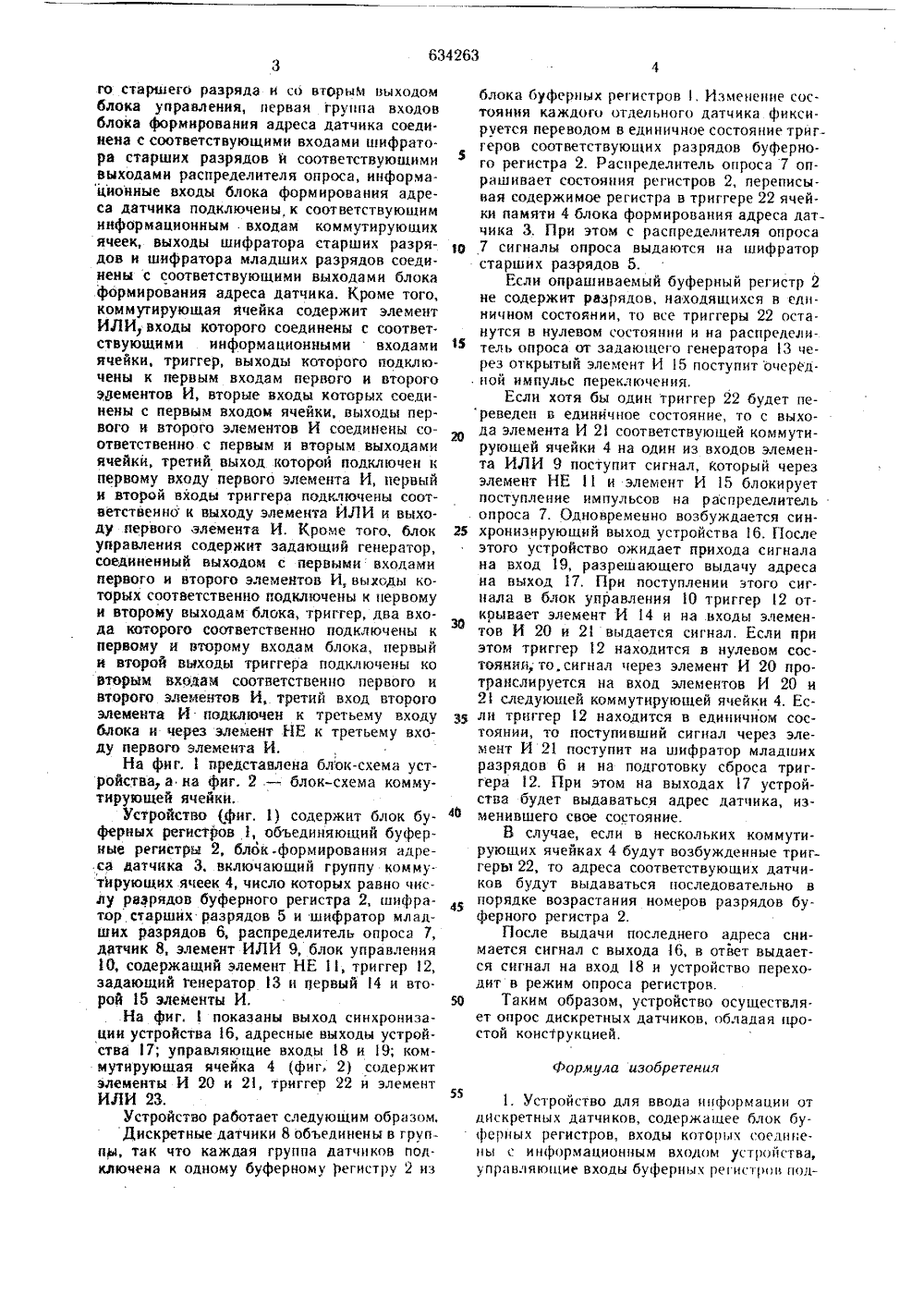

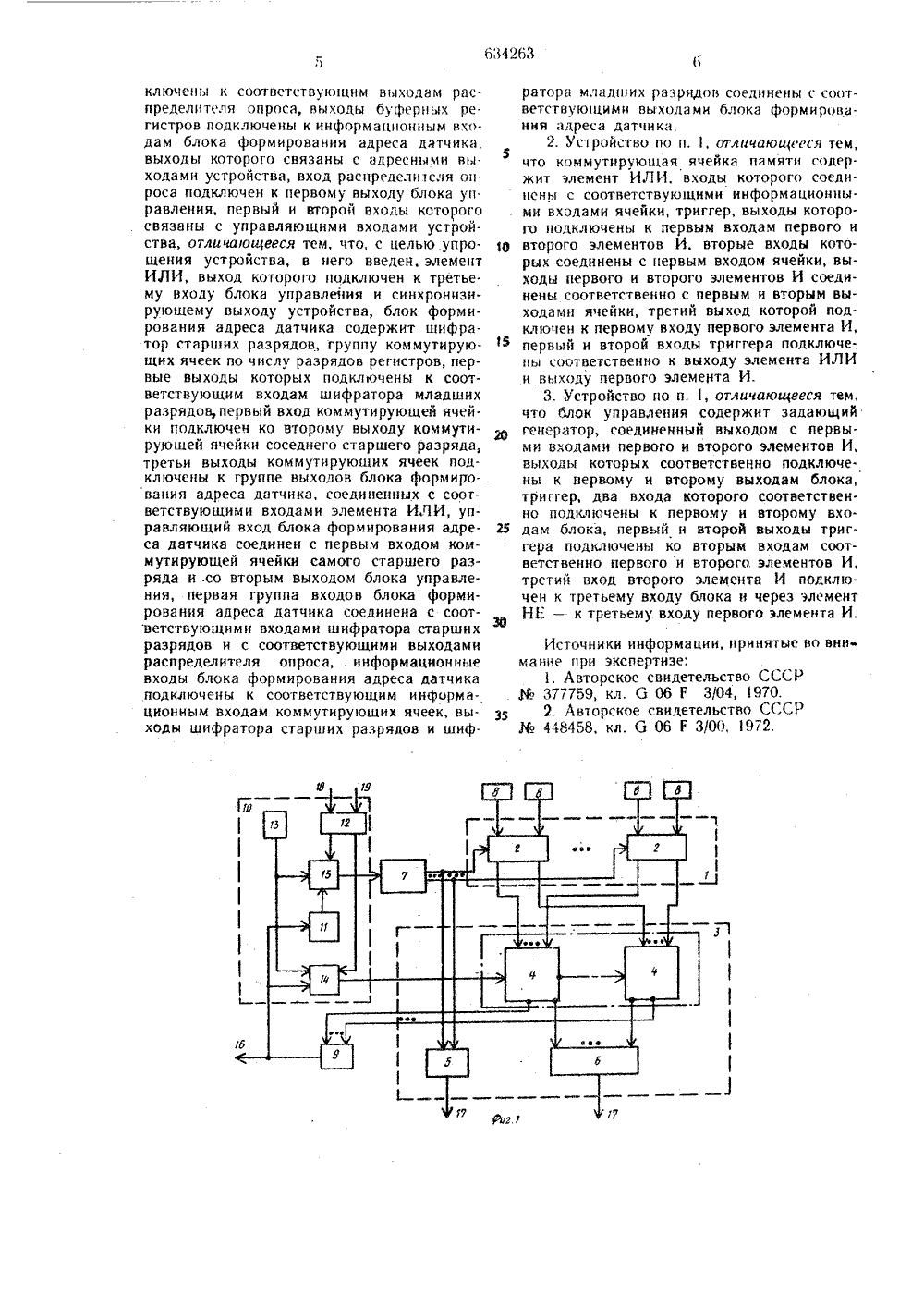

САНИ Е РЕТЕНИЯ Своа Севвтскми Сецналмстмческми Республик(И) Дополнительное к авт, санд. 1) М. Кл. 4 о 6 Г 3 го 4 4.03.76 (21)233961нем заявки рнсоеднн ооудеротввнивб комитетСовета Мииистоов СССоо долам изобрвтвееи открытий(72) Авторы изобретения лорусский филиал Государственного научно-исследовательског энергетического института им. Г, М, Кржижановского) Заявитель стгойство для ВВОДА инфоРмАциОт дискРетных дАтчикОВ Изобретение относится к областн вычнслнтельной техннкн н может быть использовано в вычислительных снстемах для ввода информации от множества дискретных датчиков,Известно устройство дл я ввода н н форм ацнн от дискретных датчиков 1), содержащее устройство запомннанця изменения состояння датчиков, устройство формирования адреса, регнстры н коммутатор н решающее задачу опроса датчиков н ввода в. вычислительную машнну. адреса датчика, состояние которого изменилось.Недостатком такого типа устройств являЕтся их сложность.Наиболее близкнм к данному по сущности технического решения является устройство 2) для ввода ннформацнн, содержащее блок буферных регистров, входы которых соединены с ннфор мацнонны м входом устройства, управляющие входы буферных регистров- подкл очены к соответствующнм выходам распределителя опроса, выходы бу. ферных регнстров подключены к информационным входам блока формирования адреса датчика. выходы которого связаны с ад. реснымн выходамн устройства, вход распределителя опроса подключен к первому выходу блока унравлення, первый н второй входы которого связаны с управлякщнчп входачн устройства.Недостатком этого устройства являет.ся большой объем оборудования.Целью изобретения является упрощениеустройства.Поставленная цель достигается тем, чтов устройство введен элемент ИЛИ, выход которого подключен к третьему входу блока 10 управления и сннхроннзнрчюшему выход 1устройства, блок формирования адреса дат.чика содержит шифратор старшнх разрядов, группу коммутирукнцнх ячеек по числу раз.рядов регистров первые выходы которых подключены к соответствующим входам шнфратора младших разрядов, первый вход ком.мутирующей ячейки подключен ко второму выходу коммутирующей ячейкн соседнегО старшего разряда, третьн выходы ком му.тнрующнх ячеек подключены к группе вы- Ю ходов блока формнровання адреса датчнка,соединенных с соОтветствующими входамн элемента НЛИ, управляющим вход блока формнрования адреса датчика соединен с первым молом коммтнрующей ячейкн самого старшего разряда н со втОрим выходом блока управления, первая группа нходон блока формирования адреса датчика соеди. иена с соответствующими входами шифратора старших разрядов н соответствующими выходамн распределители опроса, информационные входы блока формирования адреса датчика подключены, к соответствующим информационным входам коммутирующих ячеек, выходы шифратора старших разрядов и шифратора младших разрядов соединены с соответствующими выходами блока формирования адреса датчика, Кроме того, коммутирующая ячейка содержит элемент ИЛИ входы которого соединены с соответствующими информационнымивходами ячейки, триггер, выходы которого подключены к первым входам первого и второго элементов И, вторые входы которых соединены с первым входом ячейкивыходы первого и второго элементов И соединены соответственно с первым и вторым выходами ячейки, третий выход которой подключен к первому входу первого элемента И, первый и второй входы триггера подключены соответственно к выходу элемента ИЛИ и выходу первого элемента И. Кроме того, блок управления содержит задающий генератор, соединенный выходом с первыми входамн первого и второго элементов И, выходы которых соответственно подключены к первому и второму выходам блока, триггер, дна входа которого соответственно подключены к первому и второму входам блока, первый и второй выходы триггера подключены ко Вторым входам соответственно первого и второго элементов И, третий вход второго элемента И подключен к третьему входу блока и через элемент НБ к третьему входу первого элемента И.На фиг.представлена блок-схема устройства,а на фиг. 2. - блок-схема коммутирующей ячейки.Устройство (фиг. 1) содержит блок буферных регистров 1, объединяющий буферные регистры 2, блок-формирования адреса датчика 3. включающий группу коммутирующих ячеек 4, число которых равно числу разрядов буферного регистра 2, шифратор старших разрядов 5 и шифратор младших разрядов 6, распределитель опроса 7, датчик 8, элемент ИЛИ 9, блок управления 10, содержащий элемент НЕ 11, триггер2, задающий генератор 13 и первый 14 и второй 15 элементы И.На фиг, 1 показаны выход синхронизации устройства 16, адресные выходы устройства 17; управляющие входы 18 и 19; коммутирующая ячейка 4 фнг, 2) содержит элементы И 20 и 21, триггер 22 н элемент ИЛИ 23.Устройстао работает следующим образом, Дискретные датчики 8 объединены в группы, так что каждая группа датчиков подключена к одному буферному регистру 2 из блока буферных регистров . Изменение состояния каждого отдельного датчика фнкснруется переводом в единичное состояние триггерон соотнетстнуюцнх разрядов буферного регистра 2. Распределитель опроса 7 опрашивает состояния регистров 2, переписывая содержимое регистра в триггере 22 ячейки памяти 4 блока формирования адреса датчика 3. При этом с распределителя опроса10 7 сигналы опроса выдаются на шифраторстарших разрядов 5.Если опрашиваемый буферный регистр 2не содержит разрядов, находящихся н единичном состоянии, то нсе триггеры 22 останутся в нулевом состоянии и на распределитель опроса от задающего генератора 3 через открытый элемент И 5 поступит очеред. ной импульс переключения,Если хотя бы один триггер 22 будет переведен в единичное состояние, то с выхода элемента И 21 соответствующей коммутирующей ячейки 4 на один из входов элемента ИЛИ 9 поступит сигнал, который черезэлемент НЕ 11 и элемент И 15 блокируетпоступление импульсов на распределительопроса 7. Одновременно возбуждается син 25 хронизнрующий выход устройства 16. Послеэтого устройство ожидает прихода сигналана вход 19, разрешающего выдачу адресана выход 17, При поступлении этого сигнала в блок управления О триггер 2 откоывает элемент И 14 и на входы элементов И 20 и 21 выдается сигнал, Если приэтом триггер 12 находится в нулевом состояния, то.снгнал через элемент И 20 протранслируется на вход элементов И 20 и21 следующей коммутирующей ячейки 4, Есз ли триггер 12 находится н единичном состоянии, то поступивший сигнал через элемент И 21 поступит на шифратор младшихразрядов б и на подготовку сброса триггера 12. Прн этом на выходах 17 устройства будет выдаваться адрес датчика, изменившего свое состояние.В случае, если в нескольких коммутирующих ячейках 4 будут возбужденные триггеры 22, то адреса соответствующих датчиков будут выдаваться последовательно ипорядке возрастания номерон разрядов буферного регистра 2.После выдачи последнего адреса снимается сигнал с выхода 16, в ответ выдается сигнал на вход 8 и устройстно переходит н режим опроса регистров.я Таким образом, устройство осуществляет опрос дискретных датчиков, обладая простой конструкцией,Формула изобретения1. Устройство для ввода информации от дискретных датчиков, содержагцее блок буферных регистров, входы которых соединены с информационным входом устройства, упранляющие входы буферных регнс 1 ив под 634263ключены к соответствующим выходам распределителя опроса, выходы буферных регистров подключены к информационным вхо. дам блока формирования адреса датчика, выходы которого связаны с адреснычи выходами устройства, вход распределителя оп. роса подключен к первому выходу блока управления, первый и второй входы которого связаны с управляющими входами устройства, отличающееся тем, что, с целью упрощения устройства, в него введен. элемент ИЛИ, выход которого подключен к третьему входу блока управления и синхронизнрующему выходу устройства, блок формирования адреса датчика содержит шифратор старших разрядов, группу коммутирующих ячеек по числу разрядов регистров, первые выходы которых подключены к соответствующим входам шифратора младших разрядов, первый вход коммутирующей ячей. ки подключен ко второму выходу коммутирующей ячейки соседнего старшего разряда, третьи выходы коммутирующих ячеек подключены к группе выходов блока формирования адреса датчика, соединенных с соответствующими входами элемента ИЛИ, управляющий вход блока формирования адреса датчика соединен с первым входом коммутирующей ячейки самого старшего разряда и.со вторым выходом блока управления, первая группа входов блока формирования адреса датчика соединена с соответствующими входами шифратора старших разрядов и с соответствующими выходами распределителя опроса, . информационные входы блока формирования адреса датчика подключены к соответствующим информационным входам коммутирующих ячеек, выходы шифратора старших разрядов и шифратора младших разрядов соединены с соответствующими выходами блока формирова.ния адреса датчика.32. Устройство по и. 1, отличающееся темФчто коммутирующая ячейка памяти содержит элемент ИЛИ, входы которого соедииены с соответствующими информационными входами ячейки, триггер, выходы которого подключены к первым входам первого и 1 ф второго элементов И, вторые входы которых соединены с первым входом ячейки, выходы первого и второго элементов И соединены соответственно с первым и вторым выходами ячейки, третий выход которой подключен к первому входу первого элемента И, первый и второй входы триггера подключены соответственно к выходу элемента ИЛИ и выходу первого элемента И.3. Устройство по п, 1, отличающееся тем,что блок управления содержит задающий генератор, соединенный выходом с первыми входами первого и второго элементов И, выходы которых соответственно подключе.ны к первому и второму выходам блока, триггер, два входа которого соответствен.но подключены к первому и второму вхо дам блока, первый и второй выходы триггера подключены ко вторым входам соответственно первого и второго элементов И, третий вход второго элемента И подключен к третьему входу блока и через элемент ЗОНЕ - к третьему входу первого элемента Й.Источники информации, принятые во внимание при экспертизе:1. Авторское свидетельство СССР377759, кл, б 06 Г 304, 1970.2. Авторское свидетельство СССР448458, кл. б 06 Г 3/00, 1972.Редактор Д;МепуЭаказ 6762/4611 ИИИПИ Гос 1130 ЭФилиал П Состав рншвнлн Техрея Тираж ударствсиного коми по делай изобрете Москва, Ж.ЗЬ, Р ПП Пвтент, г. У. Луговвя Корректор С. Шеки4 Подписноеетв Сонета Министров СССРФ н открыгн 11ушсквн наб., а. 416город, ул. Проектная, 4

СмотретьЗаявка

2339617, 24.03.1976

БЕЛОРУССКИЙ ФИЛИАЛ ГОСУДАРСТВЕННОГО НАУЧНО ИССЛЕДОВАТЕЛЬСКОГО ЭНЕРГЕТИЧЕСКОГО ИНСТИТУТА ИМ. Г. М. КРЖИЖАНОВСКОГО

АНИЩЕНКО АЛЕКСАНДР ДМИТРИЕВИЧ, КАХАНОВИЧ ВЛАДИМИР СЕМЕНОВИЧ

МПК / Метки

МПК: G06F 3/04

Метки: ввода, датчиков, дискретных, информации

Опубликовано: 25.11.1978

Код ссылки

<a href="https://patents.su/4-634263-ustrojjstvo-dlya-vvoda-informacii-ot-diskretnykh-datchikov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для ввода информации от дискретных датчиков</a>

Предыдущий патент: Бесконтактная клавиша

Следующий патент: Устройство для сопряжения цифровой вычислительной машины с телеграфным каналом связи

Случайный патент: Перегружатель для насыпных грузов