Дискриминатор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 356769

Автор: Дайнаускас

Текст

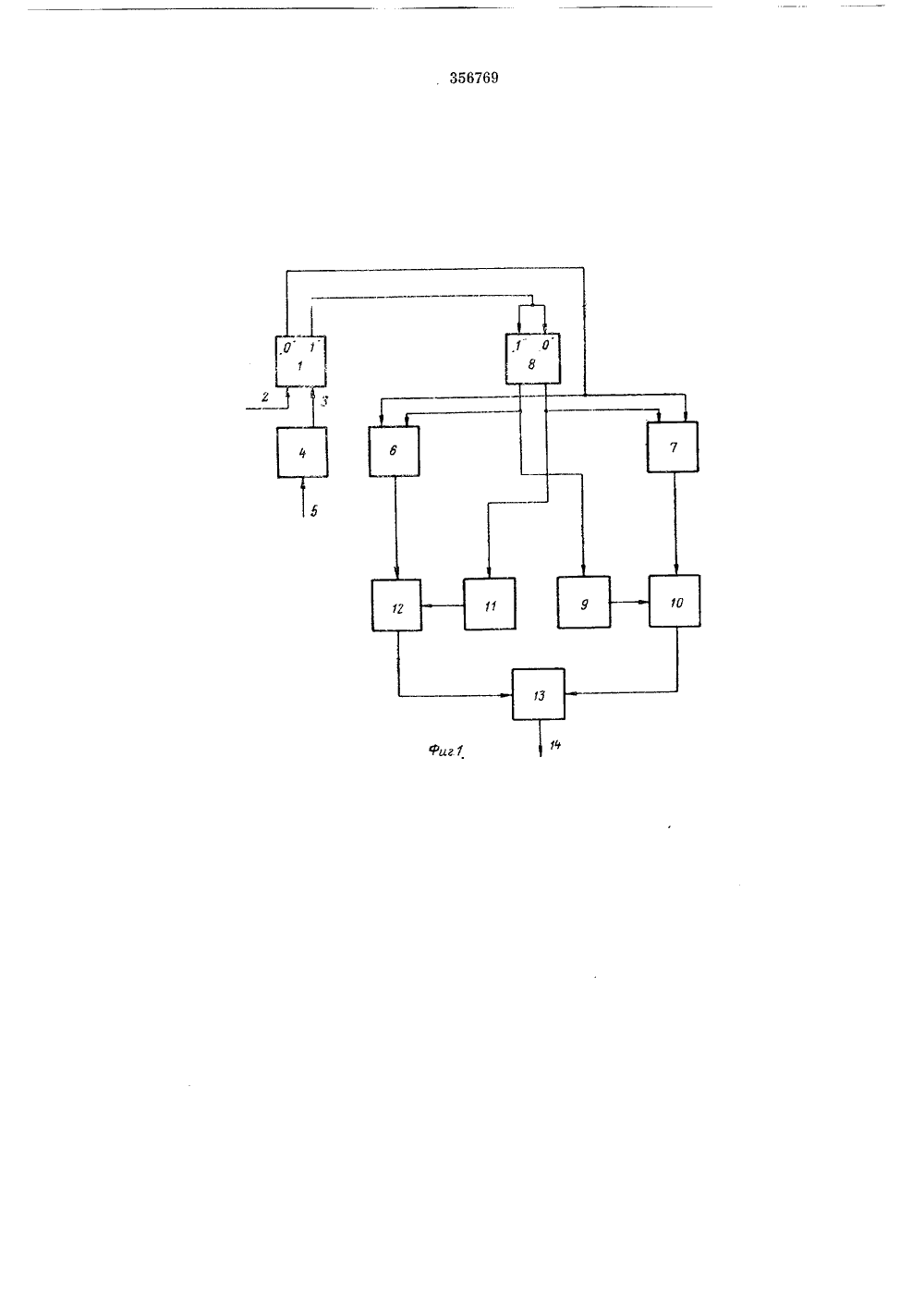

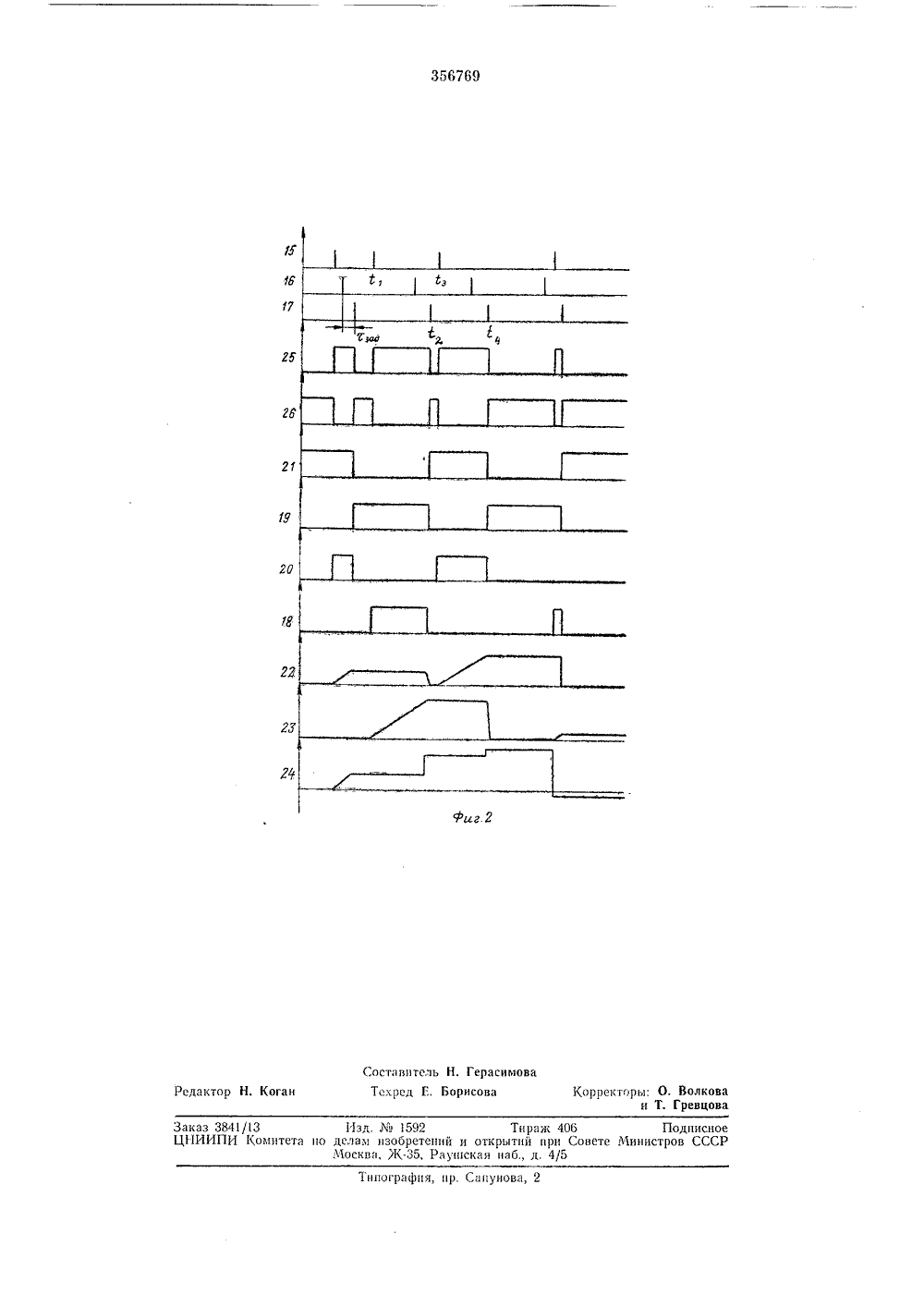

ОП ИИЗОБРЕТЕНИЯ Союз Советских Социалистических РеспуоликК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Зависимое от авт. свидетельства-Заявлено 08.Х.1970 ( 1482281/26-9)с присоединением заявки-Кл. Н 031 5/18 Комитет по делазобретеиий и откр риоритетпубликовано 23.Х.1972. Бюллетень32 ДК 021.374,33(088.8Совете МинистСССР а опубликованн писания 7.ХП.1972 Автор)зобретения И.-А. И. Дайнаускас Каунасский политехнический институЗаявите ДИСКРИМИНАТОР Изобретение относится к области импульсной техники, а именно к дискриминаторам временных рассогласований между двумя и- пульсными последовательностями.Известны временные дискриминаторы, позволяющие различать временное рассогласование импульсов любой величины,Однако известные дискриминаторы не,позволяют получить мгновенной величины временного рассогласования.Цель изобретения - определение мгновенной величины временного рассогласования. Достигается это тем, что в предлагаемом дискриминаторе нулевой выход измерительного триггера соединен с одними из входов схем И, подсоединенных другими входами соответственно к нулевому и единичному выходам дополнительного триггера, счетный вход которого соединен с единичным выходом измерительного триггера, при этом выходы схем И через интеграторы, схемы сброса которых подсоединены перекрестно к выходам дополнительного триггера, подключены к сумматору,На фиг, 1 приведена блок-схема дискриминатора; на фиг, 2 -- временные диаграммы его работы.К нулевому входу измерительного триггера 1 подсоедвнена шина 2 входных импульсов, к единичному входу при помощи шины 8 блок 4 задержки импульсов с подключенной на входе шиной 5 входных импульсов. Величине рассогласования соответствует длительположптельного перепада на(1 якенияна нулевом выходе измерительного триггера,5 который подключен к двум схемам И 6 и 7в двух каналах. Единичный выход измерительного триггера 1 подключен к счетномувходу дополнительного триггера 8, единичныйвыход которого подсоединен и схеме И 6 и10 схеме сброса 9 интегратора 10, Нулевой выходтриггера 8 подключен к схеме И 7 и схемесброса 11 интегратора 12. Выходы схем Иб и 7 подсоединены соответственно к входаминтеграторов 10 и 12, а к выходам последних15 подключен сумматор 1 с выдачей напряжения на шине 14,Устройство работает следующим образом,Входные импульсы 15 (сч. фиг. 2) подводятся к нулевому входу измерительного триг 20 гера 1, к единичному входу которого подключен блок 4 задеркки импульсов со входом импульсов 16. При временном рассогласованииимпульсов 15 и 16 меньше половины периодаследования к едийпчному входу измеритель 25 ного триггера 1 при любом положении импульсов 16 (опережение или отставание поотношению к импульсам 15) поступает серияимпульсов 17, всегда задержанных по отношению к импульсам 15 (для этого подбирается30 время задержки). Таким образом длитель.5 10 15 20 25 30 35 40 45 ность положительного импульса на нулевом выходе измерительного триггера 1 соответствует временному рассогласованию плюс величина задержки. Эта последовательность импульсов поступает к одному из входов схем И б и 7 на другие входы которых приходят соответственно импульсы единичного и нулевого выходов триггера 8.Триггер 8 запускается положительным фронтом единичного выхода триггера 1, что осуществляется, например, дифференцированием его, При совпадении импульсов одинаковой полярности, например, в интервале времени 1, - 1 нулевого выхода измерительного триггера 1 и нулевого выхода триггера 8 схемой И 7 формируется импульс 18, во время которого емкость интегратора 10 заряжается до величины, пропорциональной временному рассогласованию, В интервале времени схема И б закрыта, на выходе интегратора имеется напряжение, пропорциональное временному рассогласованию ранее бывшего периода последовательности серии импульсов.В момент времени 1 отрицательным фронтом импульса 19 на нулевом выходе триггера 8 запускается схема сброса 11, мгновенно разряжающая емкость интегратора 12. К этому времени заканчивается заряд емкости интегратора 10, емкость которого подводится к сумматору 18.В момент времени 1 з срабатывает схема И б и выдает импульс 20, во время которого заряжается емкость интегратора 12 до времени 14. При этом отрицательный фронт импульса 21 на единичном выходе триггера 8 через схему сброса 9 (позиция 22 на фиг. 2) мгновенно разряжает интегратор 10 (позиция 28 на фиг, 2). Сумматор 18 выдает напряжение (позиция 24 на фиг, 2), полярность которого зависит от положения во времени импульсов 15 и 16 (опережение или отставание по взаимному отношению периода). Нулевое значение выходного напряжения на шине 14 соответствует времени задержки блоком 4, так как при нулевом временном рассогласовании на входах триггера 1 из-за задержки блока 4 имеется две последовательности импульсов с взаимной временной задержкой тзад, по которой при калибровке прибора (при закорачивании входных шин 2 и 5 на триггер 1 подается периодическая импульсная последовательность) выходной сигнал на шине 14 устанавливается равным нулю, В практически работающем устройстве установка нуля дискриминатора проводится в блоке сумматора 18, который представляет собой эмиттерный повторитель, к базовой цепи которого подключены выходы интеграторов 10 и 12. Повторитель питается напряжением положительной и отрицательной полярности, так что регулировкой рабочей точки транзистора повторителя можно получить (режим калибровки) выходное напряжение, равное нулю.Сигналы на нулевом и единичном выходах триггера 1 на фиг, 2 соответственно объединены позициями 25 и 2 б,Таким образом, на выходной шине 14 действует напряжение, знак и мгновенное значение которого пропорциональны временному рассогласованию между последовательностями входных импульсов,Предмет изобретения Дискриминатор временных рассогласований между двумя импульсными последовательностями, содержащий входной измерительный триггер с блоком задержки на одном из входов, дополнительный триггер, две схемы И, интеграторы со схемами сброса и сумматор, выход которого является выходом дискриминатора, отлсяаюсчссйся тем, что, с целью определения мгновенной величины временного рассогласования, нулевой выход измерительного триггера соединен с одними из входов схем И, подсоединенных другими входами соответственно к нулевому и единичному выходам дополнительного триггера, счетный вход которого соединен с единичным выходом измерительного триггера, при этом выходы схемы И через интеграторы, схемы сброса которых подсоединены перекрестно к выходам дополнительного триггера, подключены к сумматору.шографпя, пр. Сапунова, 2 аказ 3841/13 Изд. Юц 1592 Тираж 40 Ь ЦИИИПИ Комитета по делам изобретений и открытий прп Сове Москва, )К, Раугнская наб., д. 4/5

СмотретьЗаявка

1482281

И. А. И. Дайнаускас Каунасский политехнический институт

МПК / Метки

Метки: дискриминатор

Опубликовано: 01.01.1972

Код ссылки

<a href="https://patents.su/4-356769-diskriminator.html" target="_blank" rel="follow" title="База патентов СССР">Дискриминатор</a>

Предыдущий патент: Мспределитель сигналов

Следующий патент: Селектор импульсов по длительности

Случайный патент: Регулятор электрической мощности