Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1656685

Автор: Скорняков

Текст

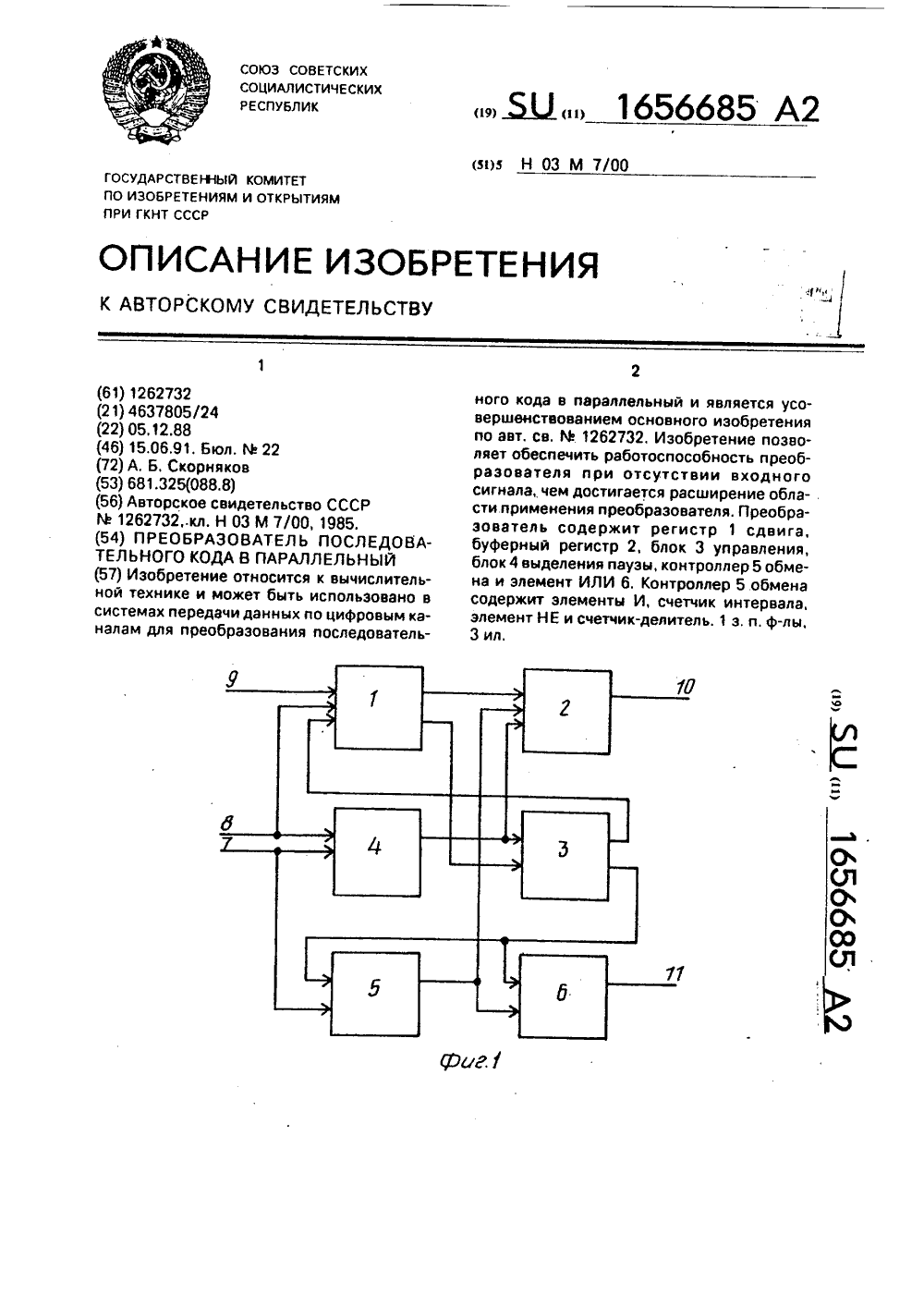

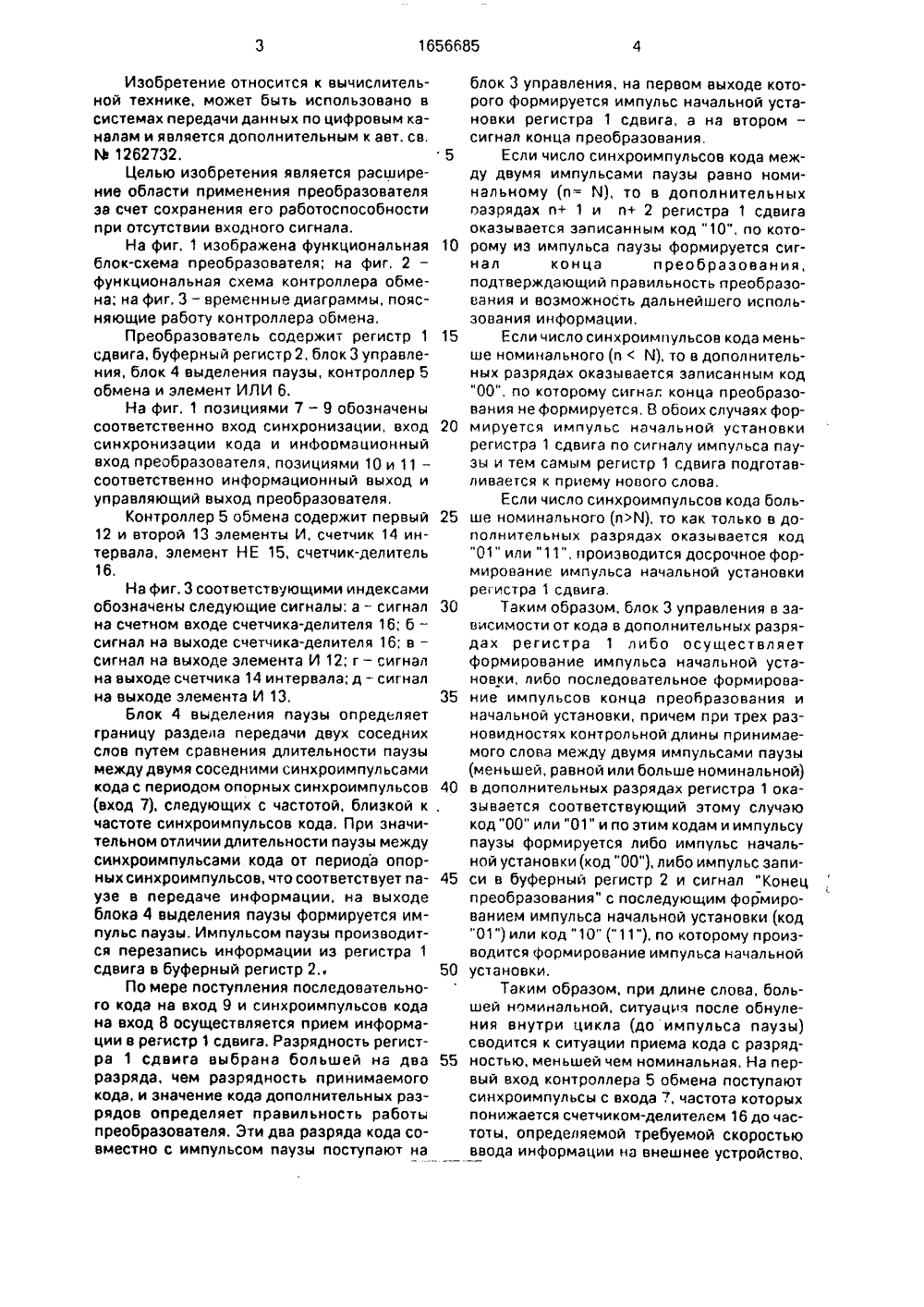

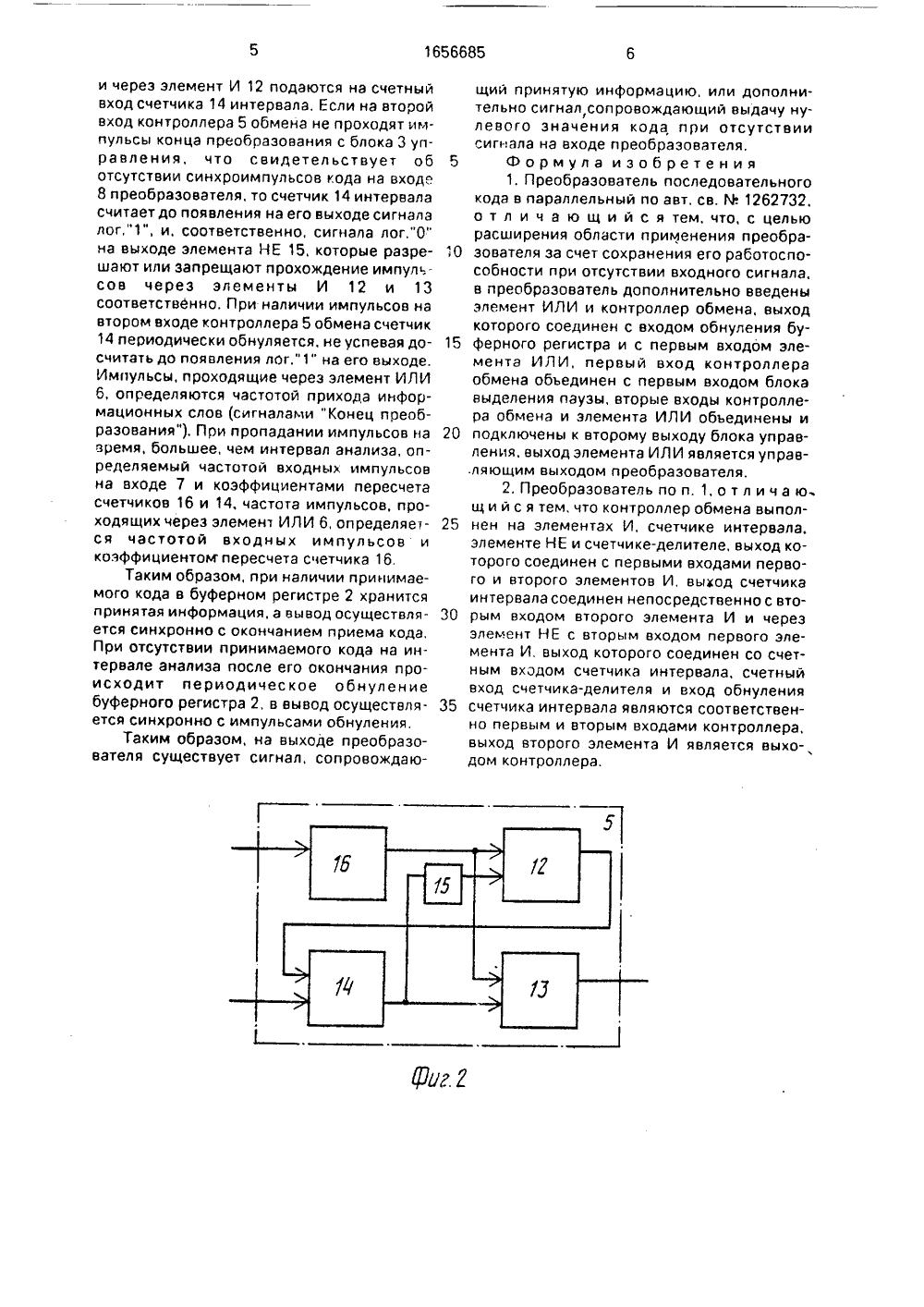

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 16566 9) 03 М 7/ ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКНТ СССР ПИСАНИЕ ИЗОБРЕТЕНИ К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СССРМ 1262732,.кл. Н 03 М 700, 1985.(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ(57) Изобретение относится к вычислительной технике и может быть использовано всистемах передачи данных по цифровым каналам для преобразования последовательного кода в параллельный и является усовершенствованием основного изобретения по авт. св. ЛЬ 1262732. Изобретение позволяет обеспечить работоспособность преобразователя при отсутствии входного сигнала, чем достигается расширение обла- . сти применения преобразователя. Преобразователь содержит регистр 1 сдвига, буферный регистр 2, блок 3 управления, блок 4 выделения паузы, контроллер 5 обмена и элемент ИЛИ 6. Контроллер 5 обмена содержит элементы И, счетчик интервала, элемент НЕ и счетчик-делитель. 1 з, п. ф-лы, 3 ил.Изобретение относится к вычислительной технике, может быть использовано в системах передачи данных по цифровым канвлам и является дополнительным к авт. св, 1 Ф 1262732. 5Целью изобретения является расширение области применения преобразователя эв счет сохранения его работоспособности при отсутствии входного сигнала.На фиг. 1 изображена функциональная 10 блок-схема преобразователя; на фиг, 2 - функциональная схема контроллера обмена; на фиг. 3 - временные диаграммы, поясняющие работу контроллера обмена.Преобразователь содержит регистр 1 15 сдвига, буферный регистр 2, блок 3 управления, блок 4 выделения паузы, контроллер 5 обмена и элемент ИЛИ 6.На фиг, 1 позициями 7 - 9 обозначены соответственно вход синхронизации, вход 20 синхронизации кода и инФоомационный вход преобразователя, позициями 10 и 11 - соответственно информационный выход и управляющий выход преобразователя,Контроллер 5 обмена содержит первый 25 12 и второй 13 элементы И, счетчик 14 интервала, элемент НЕ 15, счетчик-делитель 16.На фиг. 3 соответствующими индексами обозначены следующие сигналы: а - сигнал 30 на счетном входе счетчика-делителя 16; б - сигнал на выходе счетчика-делителя 16; в - сигнал на выходе элемента И 12; г - сигнал на выходе счетчика 14 интервала; д - сигнал на выходе элемента И 13, 35Блок 4 выделения паузы определяет границу раздела передачи двух соседних слов путем сравнения длительности паузы между двумя соседними синхроимпул ьсами кода с периодом опорных синхроимпульсов 40 (вход 7), следующих с частотой, близкой к, частоте синхроимпульсов кода. При значительном отличии длительности паузы между синхроимпульсами кода от периода опорных синхроимпульсов, что соответствует па уэе в передаче информации, на выходе блока 4 выделения паузы формируется импульс паузы. Импульсом паузы производится перезапись информации иэ регистра 1 сдвига в буферный регистр 2., 50По мере поступления последовательного кода на вход 9 и синхроимпульсов кода на вход 8 осуществляется прием информации в регистр 1 сдвига, Разрядность регистра 1 сдвига выбрана большей на два 55 разряда, чем разрядность принимаемого кода, и значение кода дополнительных разрядов определяет правильность работы преобразователя, Эти два разряда кода совместно с импульсом паузы поступают на блок 3 управления, на первом выходе которого формируется импульс начальной установки регистра 1 сдвига, а на втором -сигнал конца преобразования,Если число синхроимпульсов кода между двумя импульсами паузы равно номинальному (и= Й), то в дополнительныхоаэрядах и+ 1 и и+ 2 регистра 1 сдвигаоказывается записанным код "10", по которому из импульса паузы формируется сигнал конца преобразования,подтверждающий правильность преобразования и возможность дальнейшего использования информации,Если число синхроимпульсов кода меньше номинального (иЙ), то в дополнительных разрядах оказывается записанным код"00", по которому сигнаг, конца преобразования не формируется, В обоих случаях формируется импульс начальной установкирегистра 1 сдвига по сигналу импульса паузы и тем самым регистр 1 сдвига подготавливается к приему нового слова.Если число синхроимпульсов кода больше номинального (пМ), то как только в дополнительных разрядах оказывается код"01" или "11", производится досрочное формирование импульса начальной установкирегистра 1 сдвигаТаким образом. блок 3 управления в зависимости от кода в дополнительных разрядах регистра 1 либо осуществляетформирование импульса начальной установки, либо последовательное формирование импульсов конца преобразования иначальной установки, причем при трех разновидностях контрольной длины принимаемого слова между двумя импульсами паузы(меньшей, равной или больше номинальной)в дополнительных разрядах регистра 1 оказывается соответствующий этому случаюкод "00" или "01" и по этим кодам и импульсупаузы формируется либо импульс начальной установки (код "00"), либо импульс записи в буферный регистр 2 и сигнал "Конецпреобразования" с последующим формированием импульса начальной установки (код"01") или код "10" ("11"), по которому производится формирование импульса начальнойустановки,Таким образом, при длине слова, большей номинальной, ситуация после обнуления внутри цикла (до импульса паузы)сводится к ситуации приема кода с разрядностью, меньшей чем номинальная. На первый вход контроллера 5 обмена поступаютсинхроимпульсы с входа " частота которыхпонижается счетчиком-делителем 16 до частоты, определяемой требуемой скоростьюввода информации на внешнее устройство, 1656685и через элемент И 12 подаются на счетный вход счетчика 14 интервала. Если на второй вход контроллера 5 обмена не проходят импульсы конца преобразования с блока 3 управления, что свидетельствует об отсутствии синхроимпульсов кода на входе 8 преобразователя, то счетчик 14 интервала считает до появления на его выходе сигнала лог,"1", и, соответственно, сигнала лог,"0" на выходе элемента НЕ 15, которые разрешают или запрещают прохождение импул; - сов через элементы И 12 и 13 соответственно. При наличии импульсов на втором входе контроллера 5 обмена счетчик 14 периодически обнуляется, не успевая досчитать до появления лог."1" на его выходе. Импульсы, проходящие через элемент ИЛИ б, определяются частотой прихода информационных слов (сигналами "Конец преобразования"). При пропадании импульсов на время, большее, чем интервал анализа, определяемый частотой входных импульсов на входе 7 и коэффициентами пересчета счетчиков 16 и 14, частота импульсов, проходящих через элемент ИЛИ 6, определяе 1- ся частотой входных импульсов и коэффициентом пересчета счетчика 16.Таким образом, при наличии принимаемого кода в буферном регистре 2 хранится принятая информация, а вывод осуществляется синхронно с окончанием приема кода, При отсутствии принимаемого кода на интервале анализа после его окончания происходит периодическое обнуление буферного регистра 2, в вывод осуществляется синхронно с импульсами обнуления,Таким образом, на выходе преобразователя существует сигнал, сопровождающий принятую информацию, или дополнительно сигнал, сопровождающий выдачу нулевого значения кода при отсутствии сигнала на входе преобразователя.5 Формула изобретения1. Преобразователь последовательногокода в параллельный по авт. св. М 1262732.о т л и ч а ю щ и й с я тем, что, с целью расширения области применения преобра зователя за счет сохранения его работоспособности при отсутствии входного сигнала, в преобразователь дополнительно введены элемент ИЛИ и контроллер обмена, выход которого соединен с входом обнуления бу ферного регистра и с первым входом элемента ИЛИ, первый вход контроллера обмена объединен с первым входом блока выделения паузы, вторые входы контроллера обмена и элемента ИЛИ обьединены и 20 подключены к второму выходу блока управления, выход элемента ИЛИ является управ.ляющим выходом преобразователя.2. Преобразователь по п. 1, о т л и ч а ющ и й с я тем, что контроллер обмена выпол нен на элементах И, счетчике интервала.элементе НЕ и счетчике-делителе, выход которого соединен с первыми входами первого и второго элементов И, выкод счетчика интервала соединен непосредственно с вто рым входом второго элемента И и черезэлемент НЕ с вторым входом первого элемента И, выход которого соединен со счетным входом счетчика интервала, счетный вход счетчика-делителя и вход обнуления 35 счетчика интервала являются соответственно первым и вторым входами контроллера, выход второго элемента И является выходом контроллера.1656685 дактор Е.Копча ррек дри Заказ 2057 Тираж 461 По ВНИИПИ Государственного комитета по изобретениям 113035, Москва, Ж, Раушская набПроизводственн тельский комбинат "Патент", г, Ужгород, ул Гагарина, 101 Составитель Б.Ходо Техред М.Моргентал дписноеи открытиям при ГКНТ ССС

СмотретьЗаявка

4637805, 05.12.1988

ПРЕДПРИЯТИЕ ПЯ А-7162

СКОРНЯКОВ АНДРЕЙ БОРИСОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: кода, параллельный, последовательного

Опубликовано: 15.06.1991

Код ссылки

<a href="https://patents.su/4-1656685-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Дельта-сигма-кодер

Следующий патент: Преобразователь двоичного кода в позиционно-знаковый код

Случайный патент: Секатор