Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1464292

Автор: Скорняков

Текст

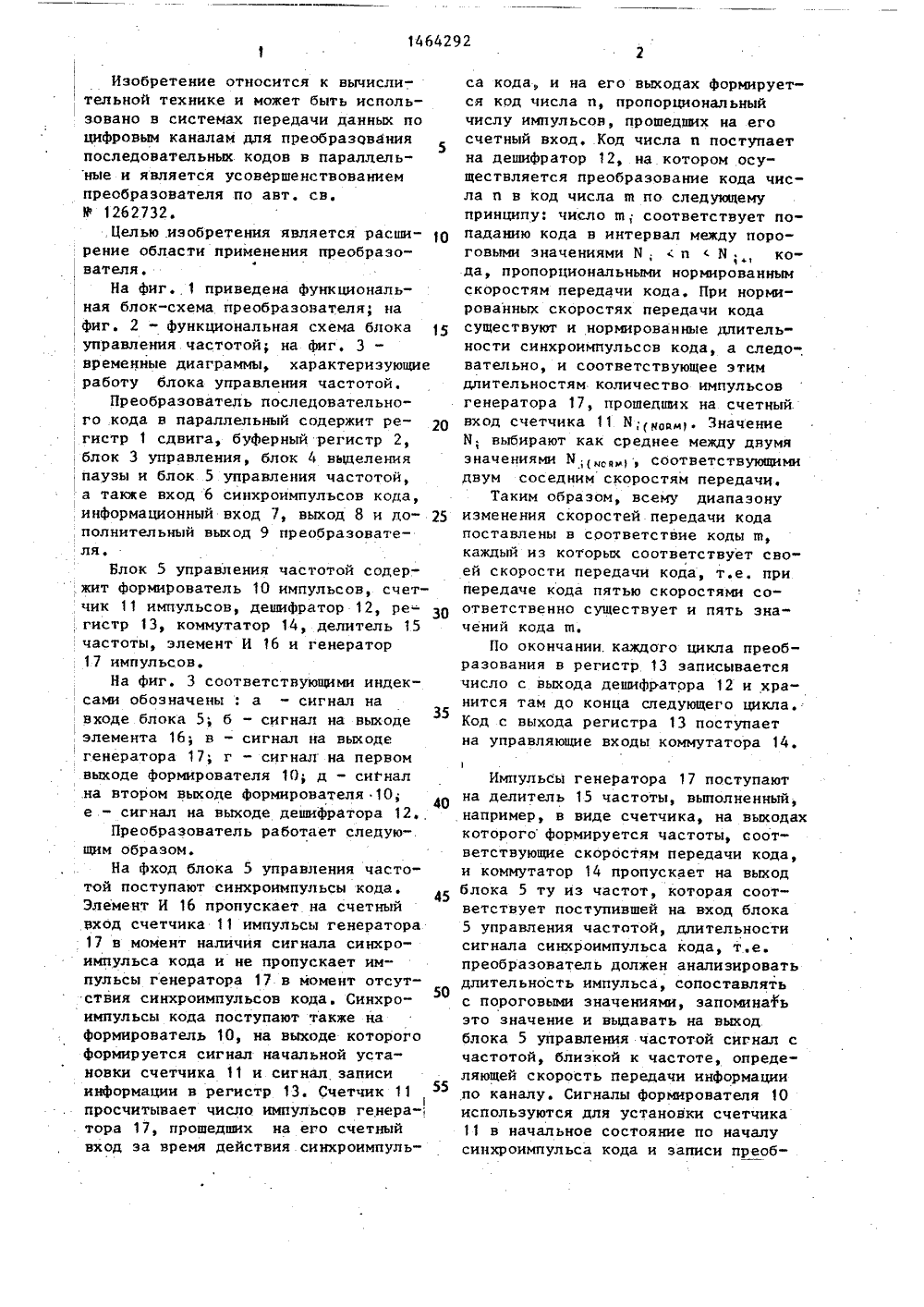

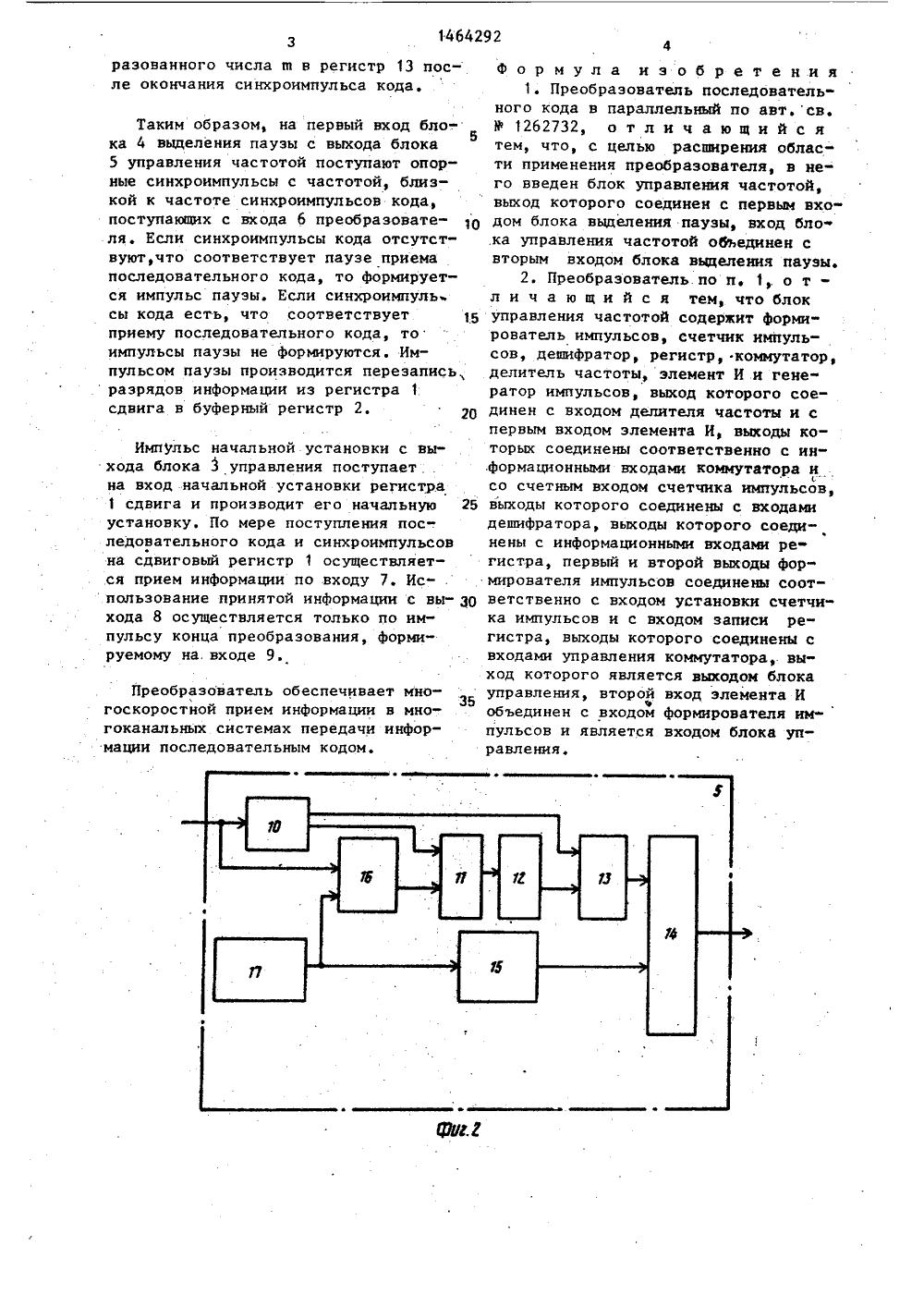

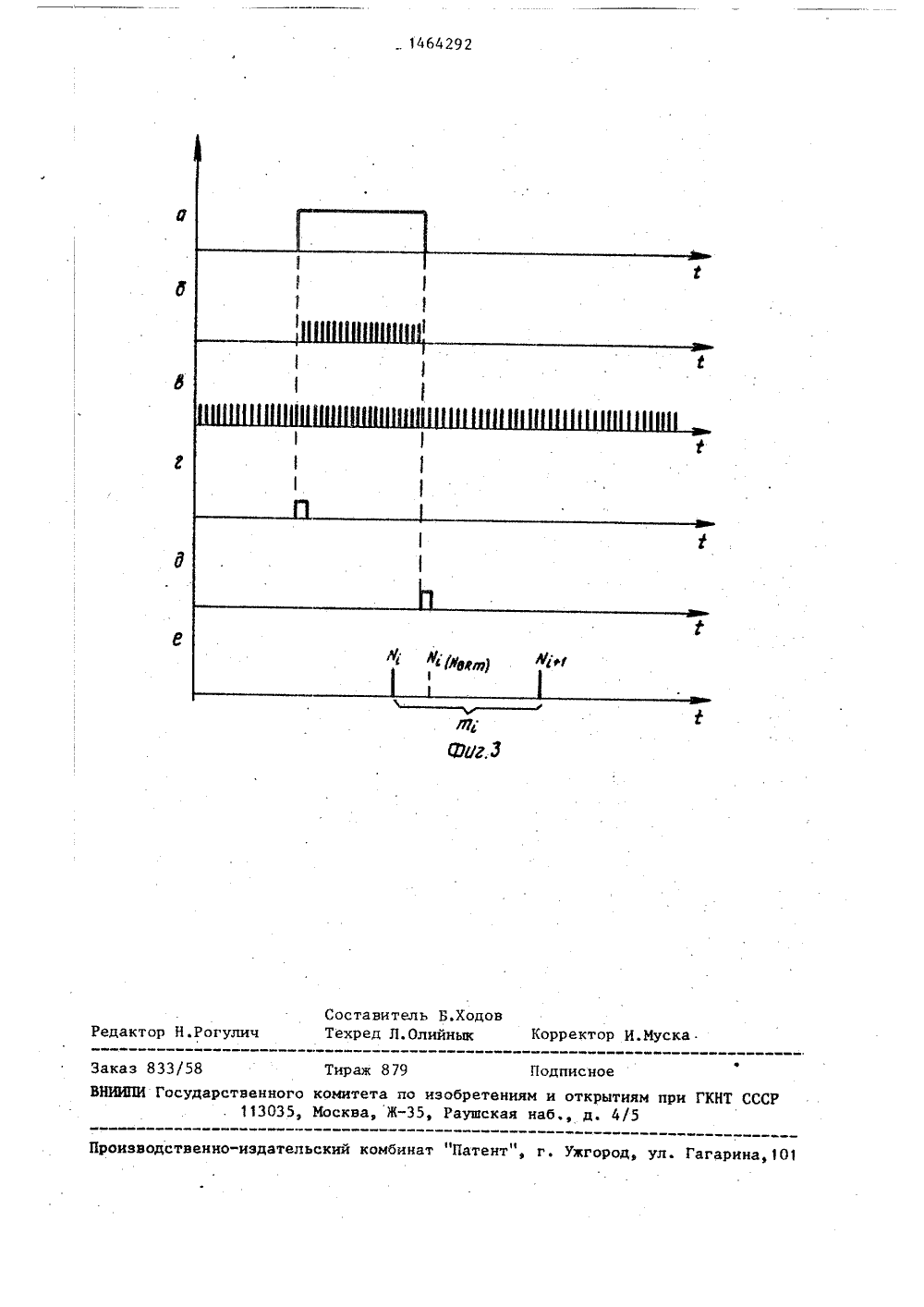

(19) (1) 4 Н 03 М 7/00 ЕТЕ ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ОПИСАНИЕ ИЗО АВТОРСКОМУ СВИДЕТЕЛЬСТ(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ(57) Изобретение относится квычислительной технике и может быть использовано в системах передачи данных по цифровым каналам для преобразования последовательных кодов впараллельные. ИзобретЕние позволяетпутем введения многоскоростного приема информации расширить область применения преобразователя. Преобразователь последовательного кода в параллельный содержит регистр 1 сдвига, буферный регистр 2, блок 3 управления, блок 4 выделения паузы иблок 5 управления частотой, содержащий формирователь импульсов, счетчикимпульсов, дешифратор) регистр, коммутатор, делитель частоты, элементИ и генератор импульсов. 2 з.п. ф-лы,3 ил,Изобретение относится к вычислительной технике и может быть использовано в системах передачи данных поцифровым каналам для преобразованияпоследовательньк кодов в параллельные и является усовершенствованиемпреобразователя по авт. св.В 1262732.Целью изобретения является расширение области применения преобразо, вателя.На фиг. 1 приведена функциональная блок-схема преобразователя наФФиг. 2 - функциональная схема блока. управления частотой; на Фиг. 3 -временные диаграммы, характеризующиеработу блока управления частотой.Преобразователь последовательного кода в параллельный содержит регистр 1 сдвига, буферный регистр 2,, блок 3 управления, блок 4 выделенияпаузы и блок 5 управления частотой,а также вход 6 синхроимпульсов кода,информационный вход 7, выход 8 и дополнительный выход 9 преобразователя,Блок 5 управления частотой содержит формирователь 10 импульсов, счетчик 11 импульсов, дешифратор 12, ре, гистр 13, коммутатор 14, делитель 15частоты, элемент И 16 и генератор17 импульсов.На фиг. 3 соответствующими индексами обозначены : а - сигнал навходе блока 5; б - сигнал на выходе35элемента 16; в - сигнал на вькодегенератора 17; г - сигнал на первомвыходе формирователя 10; д - сигнална втором вькоде формирователя 10;е - сигнал на выходе дешифратора 12.Преобразователь работает следующим образом,На фход блока 5 управления частотой поступают синхроимпульсы кода,Элемент И 16 пропускает на счетныйвход счетчика 11 импульсы генератора17 в момент наличия сигнала синхроимпульса кода и не пропускает импульсы генератора 17 в момент отсутствия синхроимпульсов кода. Синхро 50импульсы кода поступают также наформирователь 10, на выходе которогоформируется сигнал начальной установки счетчика 11 и сигнал записиинформации в регистр 13. Счетчик 111просчитывает число импульсов генера-;. тора 17, прошедших на его счетныйвход за время действия синхроимпульса кода, и на его выходах формируется код числа и, пропорциональный числу импульсов, прошедших на его счетный вход. Код числа и поступает на дешифратор 12, на котором осуществляется преобразование кода числа и в код числа ш по следующему принципу: число ш; соответствует попаданию кода в интервал между пороговыми значениями И,. :и с Л;кода, пропорциональными нормированным скоростям передачи кода, При нормированных скоростях передачи кода существуют и нормированные длительности синхроимпульсов кода, а следовательно, и соответствующее этим длительностям, количество импульсов генератора 17, прошедших на счетный вход счетчика 11 И;М 1. Значение Я; выбирают как среднее между двумя значениями И соответствующими двум соседним скоростям передачИ.Таким образом, всему диапаэону изменения скоростей передачи кода поставлены в соответствие коды в, каждый иэ которых соответствует своей скорости передачи кода, т.е. при передаче кода пятью скоростями соответственно существует и пять значений кода ш.По окончании. каждого цикла преобразования в регистр 13 записывается число с выхода дешифратора 12 и хранится там до конца следующего цикла. Код с выхода регистра 13 поступает на управляющие входы коммутатора 14.1Импульсы генеРатора 17 поступают на делитель 15 частоты, выполненный, например, в виде счетчика, на выходах которого формируется частоты, соответствующие скоростям передачи кода, и коммутатор 14 пропускает на выход блока 5 ту из частот, которая соответствует поступившей на вход блока 5 управления частотой, длительности сигнала синхроимпульса кода, т.е.преобразователь должен анализировать длительность импульса, сопоставлять с пороговыми значениями, запоминать это значение и выдавать на выход блока 5 управления частотой сигнал с частотой, близкой к частоте, определяющей скорость передачи информации по каналу. Сигналы Формирователя 1 О используются для установки счетчика 11 в начальное состояние по началу синхроимпульса кода и записи преобразованного числа в в регистр 13 после окончания синхроимпульса кода.Таким образом, на первый вход блока 4 выделения паузы с выхода блока 5 управления частотой поступают опорные синхроимпульсы с частотой, близкой к частоте синхроимпульсов кода, поступающих с входа 6 преобразователя. Если синхроимпульсы кода отсутствуют,что соответствует паузе приема последовательного кода, то формируется импульс паузы. Если синхроимпуль . сы кода есть, что соответствует 1.5 приему последовательного кода, то импульсы паузы не формируются. Импульсом паузы производится перезапись, разрядов информации из регистра 1. сдвига в буферный регистр 2.20Импульс начальной установки с выхода блока 3 управления поступает на вход начальной установки регистра 1 сдвига и производит его начальную 25 установку. По мере поступления последовательного кода и синхроимпульсов на сдвиговый регистр 1 осуществляется прием информации по входу 7. Ис- . пользование принятой информации с вы- З 0 хода 8 осуществляется только по импульсу конца преобразования, формируемому на.входе 9Преобразователь обеспечивает многоскоростной прием информации в многоканальных системах передачи информации последовательным кодом,Формула изобретения1. Преобразователь последовательного кода в параллельный по авт.св. У 1262732, о т л и ч а ю щ и й с я тем, что, с целью расширения области применения преобразователя, в него введен блок управления частотой, выход которого соединен с первым входом блока выделения паузы, вход бло ка управления частотой обьедииен с вторым входом блока выделения паузы.2. Преобразователь.по и, 1,. о тл и ч а ю щ и й с я тем, что блок управления частотой содержит формирователь импульсов, счетчик импульсов, дешифратор, регистр, коммутатор, делитель частоты, элемент И и генератор импульсов, выход которого соединен с входом делителя частоты и с первым входом элемента И, выходы которых соединены соответственно с информационными входами коммутатора и со счетным входом счетчика импульсов, выходы которого соединены с входами дешифратора, выходы которого соединены с информационными входами регистра, первый и второй выходы формирователя импульсов соединены соответственно с входом установки счетчика импульсов и с входом записи регистра, выходы которого соединены с входами управления коммутатора, выход которого является выходом блока управления, второй вход элемента И объединен с входом формирователя импульсов и является входом блока управления.. 1464292 Составитель Б.Ходоведактор Н.Рогулич Техред Л.Олийнык орректор И.Муск Заказ 833/58 Тираж 879 ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ113 О 35, Москва, Ж, Раушская наб д. 4/5 изводственно-издательский комбинат "Патент Ужгород, ул. Гагарина,

СмотретьЗаявка

4155416, 02.12.1986

ПРЕДПРИЯТИЕ ПЯ А-7162

СКОРНЯКОВ АНДРЕЙ БОРИСОВИЧ

МПК / Метки

МПК: H03M 7/00

Метки: кода, параллельный, последовательного

Опубликовано: 07.03.1989

Код ссылки

<a href="https://patents.su/4-1464292-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Преобразователь код-напряжение

Следующий патент: Устройство для формирования интегральных характеристик модулярного кода

Случайный патент: Способ определения местоположения повреждения обсадной колонны