Перестраиваемый демодулятор дискретных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

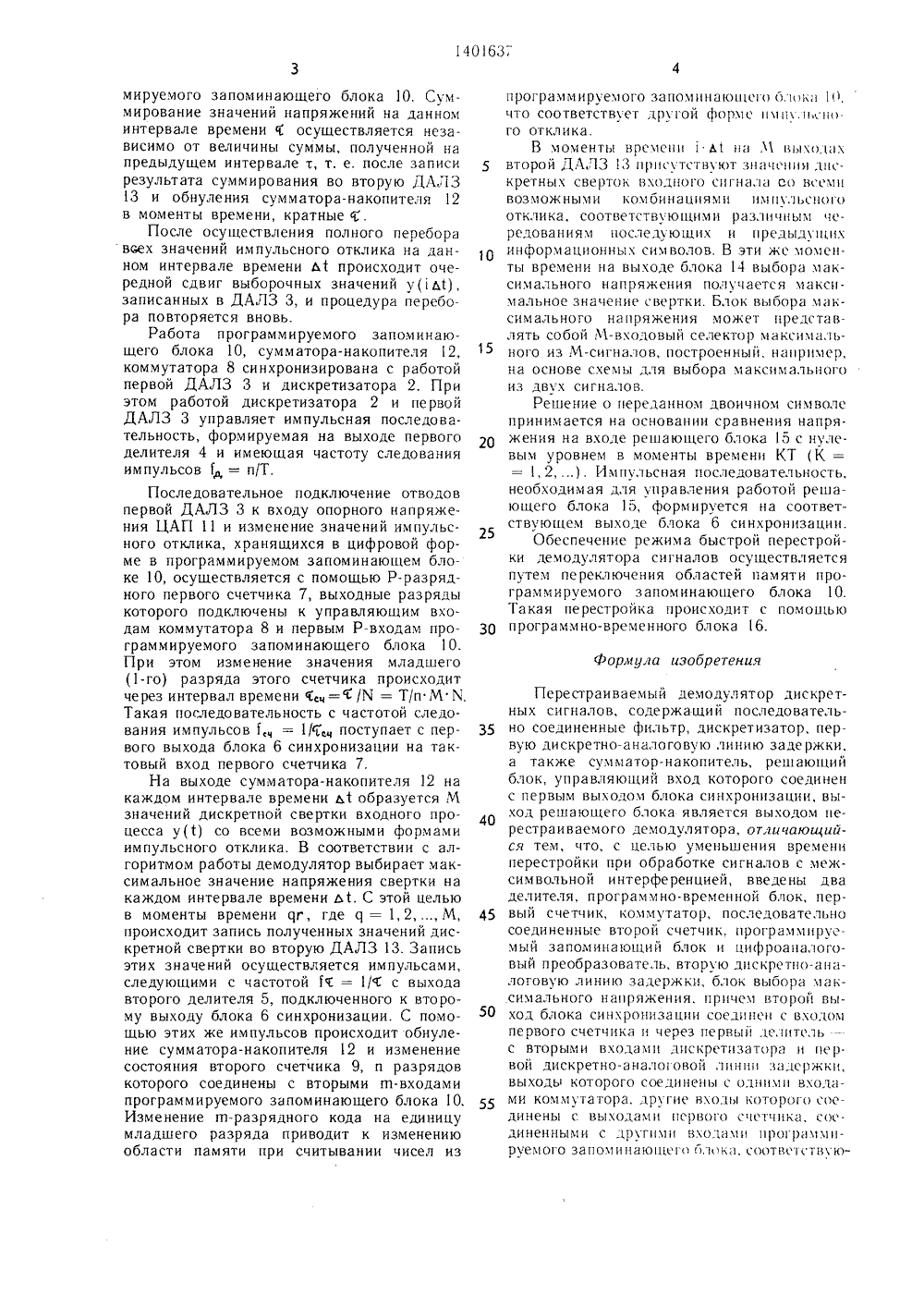

,ЯО 1401637 А 1 4 1. 2//22 ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ии инст укинская,ОДУЛЯ ике связ нтной об гн алов ением и условия го канал СУДАРСТВЕННЫЙ КОМИТЕТ СССРО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИ(54) ПЕРЕСТРАИВАЕМЫЙ ДЕМТОР ДИСКРЕТНЫХ СИГНАЛОВ(57) Изобретение относится к техни может использоваться для когереработки двоичных дискретных сиканалах связи с частотным уплотнмежсимвольной интерференцией вбыстрой перестройки работы с одно на другой. Цель изобретения - уменьшение времени перестройки при обработке сигналов с межсим вольной интерференцией. Устр-во содержит фильтр 1, дискретизатор 2, дискретно-аналоговую линию задержки (ЛЗ) 3, блок 6 синхронизации, сумматор- накопитель 12, решающий блок 15. Для достижения цели в устр-во введены делители 4 и 5, счетчики 7, 9, программно-временной блок 16, коммутатор 8, программируемый запоминающий блок 10, ЦАП 11, дискретно- аналоговую ЛЗ 13, блок 14 выбора макс. напряжения. Обеспечение режима быстрой перестройки демодулятора сигналов осуществляется путем переключения областей памяти программируемого запоминающего блока 10. Такая перестройка происходит с с помощью программно-временного блока 16. 1 ил.1401637 5 10 15 20 25 30 35 40 45 55 Изобретение относится к технике связи и может использоваться для когерентной обработки двоичных дискретных сигналов в каналах связи с частотным уплотнением и с межсимвольной интерференцией в условиях быстрой перестройки работы с одного канала на другой.Цель изобретения - уменьшение времени перестройки при обработке сигналов с межсимвольной интерференцией.На чертеже изображена структурная электрическая схема предложенного перестраиваемого демодулятора.Перестраиваемый демодулятор содержит фильтр 1, дискретизатор 2, первую дискретно-аналоговую линию 3 задержки, первый делитель 4, второй делитель 5, блок 6 синхронизации, первый счетчик 7, коммутатор 8, второй счетчик 9, программируемый запоминающий блок 10, цифроаналоговый преобразователь 11, сумматор-накопитель 12, вторую дискретно-аналоговую линию 13 задержки, блок 14 выбора максимального напряжения, решающий блок 15, программно- временной блок 16. Перестраиваемый демодулятор работает следующим образом.Аддитивная смесь у) полезного сигнала и шума поступает на вход фильтра 1, полоса пропускания ЬР которого определяется из условия ЬГ)2/д 1, где д 1 - интервал дискретизации. С выхода дискретизатора 2 последовательность выборочных у(1 дт) (1 = 1, 2, ) значений из процесса у(т) поступает на первую дискретно-аналоговую линию 3 задержки, имеющую Х отводов, причем М = г: п, где п - количество отсчетных значений при дискретизации на длительности Т информационного символа. Время задержки между двумя соседними отводами дискретно-аналоговой линии 3 задержки (ДАЛЗ) равно интервалу дискретизации Д 1 = Т/и, а общее время задержки сигнала в первой ДАЛЗ 3 составляет величину Мь(= 1.Т.За время д 1 осуществляются операции дискретной свертки выборочных значений У (1 - )дт ( = 1,2, ), хранящихся в ДАЛЗ на 1-м интервале Ь 1 со всеми возможными видами сигналов, форма которых зависит от комбинаций (1. - 1) предыдущего и (1=1) последующего символов. Для этого на каждом интервале времени= Ы/М, где М = 2,1" ), происходит формирование одного из возможных видов импульсного отклика, соответствующего определенной комбинации предыдущих и последующих символов. Для получения на этом интервале времени Т значения дискретной свертки М выборочных значений входного процесса с М выборочными значениями одной формы импульсного отклика к М отводам первой ДАЛЗ 3 подключается через коммутатор 8 вход опорного напряжения цифроаналогового преобразователя (ЦАП) 11, выход которого соединен с сумматором-накопителем 12.На выходе сумматора-накопителя 12 образуются на каждом интервале времени гзначения дискретной свертки. В качествекоммутатора могут быть использованы микросхемы К 590 КН 6, а роль сумматора-накопителя может выполнять, например, интегратор со сбросом.Все возможные виды импульсных откликов согласованного фильтра записаны впрограммируемом запоминающем блоке 10,причем каждый отклик представлен Я значениями чисел, имеющих 1 разрядов. Процедура перебора всех возможных вариантовимпульсного отклика осуществляется следующим образом,На первом интервале 1 последовательново времени с частотой 1/%, = М/ч. происходитсчитывание 1-разрядных чисел из программируемого запоминающего блока 10 и соответственное изменение коэффициента передачи ЦАП 11, выполняющего функции блока взвешивания, Одновременно (синхронно)происходит подключение отводов первойДАЛЗ 3 с помогцью коммутатора 8 к входуопорного напряжения ЦАП 11.Таким образом, первое значение первойформы импульсного отклика умножается напервое выборочное значение у(1 в 1) Ь(=-1), хранящееся на интервале 1 дт напервом отводе ДАЛЗ 3; второе значение импульсного отклика умножается на второе выборочное значение у (1 - 2) Ь( ( = 2), хранящееся на втором отводе ДАЛЗ 3 и т. д.до М-го значения импульсного отклика.С помощью сумматора-накопителя 12 Хзначений результатов перемножения указанных напряжений суммируются и на его выходе формируется первое значение дискретной свертки входного процесса у) с первой формой импульсного отклика.На втором интервале, также с частотой1/,= М/С, происходит считывание 1-разрядных чисел из программируемого запоминающего блока 1 О, но из другой области памяти,соответствующей второй форме импульсногоотклика. Осугцествляется синхронное подключение отводов ДАЛЗ 3 к входу опорного напряжения ЦАП 11. Таким образом, первое значение второй формы импульсного отклика умножается на первое выборочное значение у (1 - 1) Ь(; второе значение второй формы отклика умножается на второе выборочное значение у (1 - 2)Ь( и т д Полученные результаты суммируются также с помощью сумматора- накопителя 12.На третьем и следующих (до М-го) интервалах времени процедура вычисления значений свертки повторяется с изменением лишь областей считывания чисел из програм 140163;15 20 25 30 Формула изобретения 40 45 50 мируемого запоминающего блока 10. Суммирование значений напряжений на данном интервале времени 1 осуществляется независимо от величины суммы, полученной на предыдущем интервале т, т. е. после записи результата суммирования во вторую ДАЛЗ 13 и обнуления сумматора-накопителя 12 в моменты времени, кратные ч,.После осуществления полного перебора ваех значений импульсного отклика на данном интервале времени Ь 1 происходит очередной сдвиг выборочных значений у(1 д 1), записанных в ДАЛЗ 3, и процедура перебора повторяется вновь.Работа программируемого запоминающего блока 10, сумматора-накопителя 12, коммутатора 8 синхронизирована с работой первой ДАЛЗ 3 и дискретизатора 2. При этом работой дискретизатора 2 и первой ДАЛЗ 3 управляет импульсная последовательность, формируемая на выходе первого делителя 4 и имеющая частоту следования импульсов 1 д -- и/Т.Последовательное подключение отводов первой ДАЛЗ 3 к входу опорного напряжения ЦАП 11 и изменение значений импульсного отклика, хранящихся в цифровой форме в программируемом запоминающем блоке 10, осуществляется с помощью Р-разрядного первого счетчика 7, выходные разряды которого подключены к управляющим входам коммутатора 8 и первым Р-входам программируемого запоминающего блока 1 О. При этом изменение значения младшего (1-го) разряда этого счетчика происходит через интервал времени 1,=/1 х 1 = Т/и М 1 Х 1. Такая последовательность с частотой следования импульсов 1, = 1/, поступает с первого выхода блока 6 синхронизации на тактовый вход первого счетчика 7.На выходе сумматора-накопителя 12 на каждом интервале времени д 1 образуется М значений дискретной свертки входного процесса у(1) со всеми возможными формами импульсного отклика. В соответствии с алгоритмом работы демодулятор выбирает максимальное значение напряжения свертки на каждом интервале времени ь(, С этой целью в моменты времени с)г, где с 1 = 1,2, , М, происходит запись полученных значений дискретной свертки во вторую ДАЛЗ 13. Запись этих значений осуществляется импульсами, следующими с частотой 1 х. = 1/ с выхода второго делителя 5, подключенного к второму выходу блока 6 синхронизации. С помощью этих же импульсов происходит обнуление сумматора-накопителя 12 и изменение состояния второго счетчика 9, и разрядов которого соединены с вторыми гп-входами программ и руем ого за пом инаю щего блока 10. Изменение тп-разрядного кода на единицу младшего разряда приводит к изменению области памяти при считывании чисел из программируемого запоминдющсго блока 1, что соответствует другой формс пчп),п пюго отклика.В моменты времени 1 А 1 пд .Ч выходах второй ДАЛЗ 13 прил тствуют зндчсппя дщкретных сверток входного сигнала оо вссхп возможными комбинациями им пуп ьспого отклика, соответствующими различным чсредованиям последующих и предыдущих информационных символов. В эти жс моменты времени на выходе блока 14 выбора максимального напряжения получается максимальное значение свертки. Блок выбора максимального напряжения может представлять собой М-входовый селектор максимального из М-сигналов, построенный, например, на основе схемы для выбора максимального из двух сигналов.Решение о переданном двоичном символе принимается на основании сравнения напряжения на входе решающего блока 15 с нулевым уровнем в моменты времени КТ (К = = 1, 2,). Импульсная последовательность, необходимая для управления работой решающего блока 15, формируется на соответствующем выходе блока 6 синхронизации.Обеспечение режима быстрой перестройки демодулятора сигналов осуществляется путем переключения областей памяти программируемого запоминающего блока 10. Такая перестройка происходит с помощью программно-временного блока 16. Перестраиваемый демодулятор дискретных сигналов, содержащии последовательно соединенные фильтр, дискретизатор, первую дискретно-аналоговую линию задержки, а также сумматор-накопитель, решающий блок, управляющий вход которого соединен с первым выходом блока синхронизации, выход решающего блока является выходом перестраиваемого демодулятора, отличающийся тем, что, с целью уменьшения времени перестройки при обработке сигналов с межсимвольнойй интерференцией, введе ны два делителя, программно-временной блок, первый счетчик, коммутатор, последовательно соединенные второй счетчик, программируемый запоминающий блок и цифроаналоговый преобразователь, вторую дискретно-аналоговую линию задержки, блок выбора чаксимального напряжения, причем второй выход блока синхронизации соедпнсн с входом первого счетчика и через первый дс,штсль - с вторыми входами дискрстпздторд и псрвой дискретно-аналоговой линии здлсржкп, выходь которого соединены с одними входами коммутатора. другие входы которого соединены с выходами псрвого счстчикд, сосдиненными с другими входдчи про рдчмпруемого запомипаюгцсго блмкд, соотвстствую щие входы которого соединены с выходами программно-временного блока, выход цифроаналогового преобразователя соединен с первым входом сумматора-накопителя, выход которого соединен с первым входом второй дискретно-аналоговой линии задержки, выходы которой соединены с входами блока выбора максимального напряжения, выходом соединенного с вторым входом решающего блока, третий выход блока синхронизации через второй делитель соединен с вторыми входами второй дискретно-аналоговой линии задержки, сумматора и входом второго счетчика, выход коммутатора соединен с соответствующим входом цифроаналогового преобразователя.Составитель Н. ЛазареваРедактор А.шандор Техред И. Верес Корректор О. КравцоваЗаказ 25456 Тираж 660 ПодписноеВ 1 ИИ 1 Р Государственного когиигета СССз по делан изобретений. и открытий3035, Москва, Ж 35, 1 аушская наб., д. 4/51 ропзводственнс-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

4162460, 24.12.1986

ЛЕНИНГРАДСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. М. И. КАЛИНИНА

БАРАНЕЦКИЙ ВИКТОР ВАСИЛЬЕВИЧ, ЛУКИНСКАЯ СОФЬЯ СЕРГЕЕВНА, МАКАРОВ СЕРГЕЙ БОРИСОВИЧ, УЛАНОВ АНАТОЛИЙ МИХАЙЛОВИЧ, ХАЗАНКИН ЕВГЕНИЙ ГРИГОРЬЕВИЧ, ЦИКИН ИГОРЬ АНАТОЛЬЕВИЧ

МПК / Метки

МПК: H04L 27/22

Метки: демодулятор, дискретных, перестраиваемый, сигналов

Опубликовано: 07.06.1988

Код ссылки

<a href="https://patents.su/4-1401637-perestraivaemyjj-demodulyator-diskretnykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Перестраиваемый демодулятор дискретных сигналов</a>

Предыдущий патент: Устройство для детектирования сигналов многопозиционной частотной телеграфии

Следующий патент: Устройство для автоматического набора номера

Случайный патент: Горный компас