Система передачи и приема асинхронных цифровых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1317674

Автор: Тунев

Текст

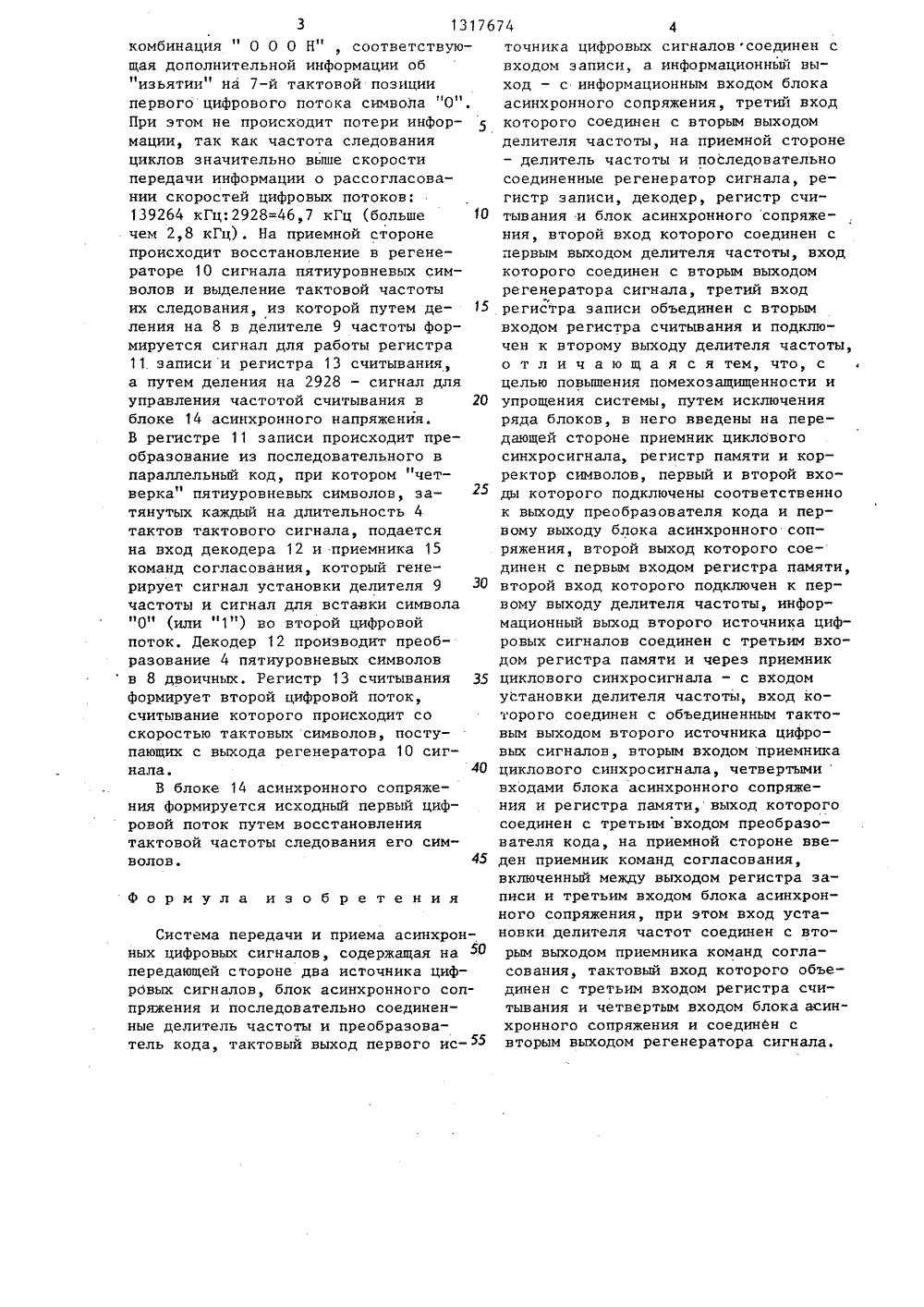

(51) 4 Н 04 1 3/00 фйар, н ф йв,у ОПИСАНИЕ ИЗОБРЕТЕНИЯ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(54) СИСТЕМА ПЕРЕДАЧИ И ПРИЕМААСИНХРОННЫХ ЦИФРОВЫХ СИГНАЛОВ(57) Изобретение относится к электросвязи и обеспечивает повышение помехозащищенности и упрощения системыпутем исключения ряда блоков. Устройство содержит на передающей стороне источники цифровых сигналов,блок асинхронного сопряжения, делитель частоты, преобразователь кода,приемник циклового синхросигнала,регистр памяти и корректор символов;на приемной стороне - делитель частоты, регенератор сигнала, регистрзаписи, декодер, регистр считывания,блок асинхронного сопряжения, приемник команд согласования, включенныймежду выходом регистра записи итретьим входом блока асинхронногосопряжения. 1 табл., 2 ил.131767Изобретение относится к электросвязи и может использоваться для передачи двух асинхронных потоков по одному каналу связи, оборудованному регенераторами пятиуровневого сигнала.Цель изобретения - повышение помехозащищенности и упрощение системы,На фиг.1 изображена структурная электрическая схема передающей стороны системы на Фиг.2 - схема приемной стороны предложенной системы.Система передачи и приема асинхронных цифровых сигналов содержит на передающей стороне источники 1 и 2 цифровых сигналов, блок 3 асинхронного сопряжения, делитель 4 частоты, преобразователь 5 кода, приемник 6 циклового синхросигнала, регистр 7 памяти и корректор 8 символов, на приемной стороне - делитель 9 частоты, регенератор 10 сигнала, регистр 11 записи, декодер 12, регистр 13 считывания, блок 14 асин.25 хронного сопряжения, приемник 15 команд согласования.1Система передачи и приема асинхронных цифровых потоков работает следующим образом, 30Источник 1 генерирует тактовый и информационный сигналы, Последний записывается в блоке 3 асинхронного сопряжения со скоростью следования символов тактового сигнала, а считывается со скоростью сигнала, формируемого на тактовом выходе источника 2 к на информационном выходе которого вырабатывается сигнал, который содержит, согласно рекомендации МККТТ С 751, в структуре цикла длиной 2928 бит синхросигнал вида 111110100000. Приемник 6 циклового синхросигнала осуществляет поиск последнего сигнала во втором цифровом потоке и Формирует 45 сигнал установки делителя 4 частоты, в котором из тактового сигнала путем деления на 8 Формируется сигнал, который для регистра 7 памяти является сигналом частоты считывания, а при делении на 2928 - сигнал огибающей команд согласования для блока 3 асинхронного сопряжения, в котором происходит преобразование скорости следования символов первого цифрового потока. Согласно рекомендации МККТТ С.751 тактовые частоты цифровых потоков от четверичных систем передачи могут отличаться на 2 х 139264.10 кГц -4 22,8 кГц,Таким образом, если скорость следования символов в первом цифровом потоке ниже, чем ва втором, то при считывании в блоке 3 асинхронного сопряжения в информационном сигнале необходимо делать вставки дополнительных тактов, а при большей скорости избыточную информацию необходимо передавать параллельно основному сигналу.В блоке 3 асинхронного сопряжения происходит посимвольное считывание, информации первого цифрового потока, кроме 7-й тактовой позиции, из которой "измывается" символ "0" (или "1") а последующие символы считываются на такт раньше, затем в регистре 7 памяти преобразуются в параллельный код таким образом, что на вход преобразователя 5 кода поочередно от каждого цифрового потока поступают "слова", состоящие из 8 символов, каждый из которых затянут на 4 такта тактового сигнала, Преобразователь 5 кода формирует пятиуровневый сигнал в виде кода 8 В 4 Я 1 с численным значением 8 В 4 Ц 1 алгоритмом кодопреобразования запрещены комбинации, которые могут быть использованы для передачи дополнительной информации со скоростью следования циклов, например, на первых 8 позициях циклового синхросигнала во втором цифровом потоке или, что равнозначно, на 1 4-й тактовых позициях выходного сигнала преобразователя 5 кода, Все требуемые команды по согласованию скорости и передачи избыточной информации первого цифрового патока сведены в таблицу, где им придано соответствующее обозначение из числа "запрещенных" блоков кода.8 В 4(1.1 При одинаковых скоростях цифровых потоков в блоке 3 асинхронного сопряжения один раз в цикл Формируется команда, по которой в корректоре 8 символов на 14-й тактовой позициях комбинация символов "=Н" заменяется через цикл на " - Н".Нри разных скоростях цифровых потоков передаче дополнительной информации непосредственно предшествует передача в течение двух циклов подряд команды одного знака. Так, с, блока 3 асинхронного сопряжения в корректоре 8 символов сформирована13176 Формула изобретения Система передачи и приема асинхронных цифровых сигналов, содержащая на 50 передающей стороне два источника цифрбвых сигналов, блок асинхронного соппряжения и последовательно соединенные делитель частоты и преобразователь кода, тактовый выход первого ис 3комбинация " О О 0 Н" , соответствующая дополнительной информации об "изьятии" на 7-й тактовой позиции первого цифрового потока символа "О", При этом не происходит потери информации, так как частота следования циклов значительно выше скорости передачи информации о рассогласовании скоростей цифровых потоков: 139264 кГц:2928=46,7 кГц (больше чем 2,8 кГц). На приемной стороне происходит восстановление в регенераторе 10 сигнала пятиуровневых символов и выделение тактовой частоты их следования, из которой путем де ления на 8 в делителе 9 частоты формируется сигнал для работы регистра 11 записи и регистра 13 считывания, а путем деления на 2928 - сигнал для управления частотой считывания в 20 блоке 14 асинхронного напряжения. В регистре 11 записи происходит преобразование из последовательного в параллельный код, при котором "четверка" пятиуровневых символов, затянутых каждый на длительность 4 тактов тактового сигнала, подается на вход декодера 12 и приемника 15 команд согласования, который генерирует сигнал установки делителя 9 30 частоты и сигнал для вставки символацОц (или "1") во второи цифровои поток. Декодер 12 производит преобразование 4 пятиуровневых символов в 8 двоичных. Регистр 13 считывания 35 Формирует второй цифровой поток, считывание которого происходит со скоростью тактовых символов, поступающих с выхода регенератора 10 сигнала. 40В блоке 14 асинхронного сопряжения Формируется исходный первый цифровой поток путем восстановления тактовой частоты следования его символов. 45 74 4точника цифровых сигналов соединен с входом записи, а информационнытй выход - с информационным входом блока асинхронного сопряжения, третий вход которого соединен с вторым выходом делителя частоты, на приемной стороне - делитель частоты и последовательно соединенные регенератор сигнала, регистр записи, декодер, регистр считывания и блок асинхронного сопряжения, второй вход которого соединен с первым выходом делителя частоты, вход которого соединен с вторым выходом регенератора сигнала, третий вход регистра записи объединен с вторым входом регистра считывания и подключен к второму выходу делителя частоты, о т л и ч а ю щ а я с я тем, что, с целью повышения помехозащищенности и упрощения системы, путем исключения ряда блоков, в него введены на передающей стороне приемник циклового синхросигнала, регистр памяти и корректор символов, первый и второй входы которого подключены соответственно к выходу преобразователя кода и первому выходу блока асинхронного сопряжения, второй выход которого соединен с первым входом регистра памяти, второй вход которого подключен к первому выходу делителя частоты, информационный выход второго источника цифровых сигналов соединен с третьим входом регистра памяти и через приемник циклового синхросигнала - с входом установки делителя частоты, вход которого соединен с объединенным тактовым выходом второго источника цифровых сигналов, вторым входом приемника циклового синхросигнала, четвертымивходами блока асинхронного сопряжения и регистра памяти, выход которого соединен с третьим входом преобразователя кода, на приемной стороне введен приемник команд согласования, включенный между выходом регистра записи и третьим входом блока асинхронного сопряжения, при этом вход установки делителя частот соединен с вторым выходом приемника команд согласования, тактовый вход которого объединен с третьим входом регистра считывания и четвертым входом блока асинхронного сопряжения и соединен с вторым выходом регенератора сигнала,1317674 Команда Двоичноеобозначение ОООО= Н Пропусктакта 0011 00 Вставка символа "0" 1110 . ОООН Вставка символа "1" 1101 ООНО 1100- НН цвайСоставитель Н.ЛазареваРедактор И.Рыбченко Техред В.Кадар Корректор С.Черни Заказ 2437/56 Тираж 638 ВНИИПИ государственного комитета СССР по делам изобретений и открытий 113035, Москва Ж, Раушская наб д.4/5

СмотретьЗаявка

4002931, 06.01.1986

ПРЕДПРИЯТИЕ ПЯ М-5209

ТУНЕВ ДМИТРИЙ ГЕННАДЬЕВИЧ

МПК / Метки

МПК: H04J 3/00

Метки: асинхронных, передачи, приема, сигналов, цифровых

Опубликовано: 15.06.1987

Код ссылки

<a href="https://patents.su/4-1317674-sistema-peredachi-i-priema-asinkhronnykh-cifrovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Система передачи и приема асинхронных цифровых сигналов</a>

Предыдущий патент: Приемное устройство стереофонического сигнала

Следующий патент: Преобразователь двоичного кода в трехпозиционный код

Случайный патент: Газораспределительное устройствопрямоточного типа