Приемник сигналов модулированных одновременно по частоте и фазе

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

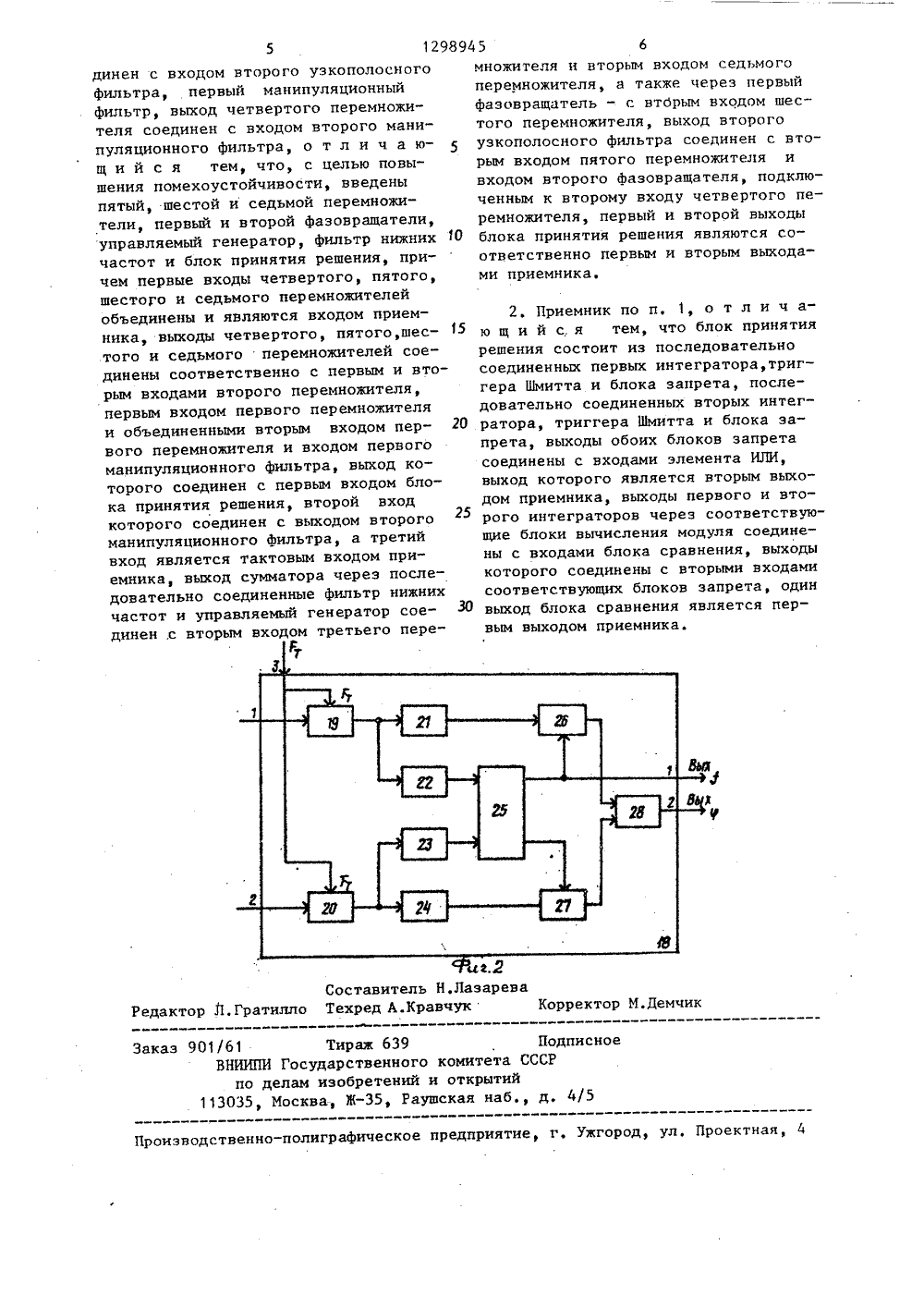

1298945 3 ЧЧ зп(+ - -ьу) .Н 2 При этом напряжениена втором входе блока 18 отсутствует, т.е. Ч, - О.(1(5По знаку напряжения Ч определяется фаза входного сигнала, а по результату сравнения Ч и Ч,р принит( (Рг мается решение о том, что йа входе приемника присутствует сигнал с час тотой Ю, .В случае поступления входного сигнала с частотой ИгЧ-О, Ч -Ч зп(+ 2)15(По знаку напряжения Ч определяется фаза входного сигнала а по ре(Р зультату сравнения Ч и Ч приниРг мается решение о том, что частота 20 входного сигнала ОТаким образом, если Ч Ч , тот( (1(а ф принимается решение, что входной сигнал имеет частоту И(, а если Ч, сЧ9( Фаф то принимается решение, что входной 25 сигнал имеет частоту ыг.Блок 18 принятия решения работает следующим образом. На его входы поступают напряжения с выхода манипуляционных фильтров 14 и 15. 30Пусть входной сигнал имеет частоту д(ТогдаЧ Ч зп(+ - -ьч91 2 35Ч-О.С помощью интеграторов 19 и 20 производится интегрирование значений Чи Ч(р еПериод интегрирования определяет ся тактовыми импульсами частоты Р .и равен длительности единичного символа входного сигнала. Принятие решения о частоте . вход ного сигнала производится с помощью блоков 22 и 23 вычисления модулей и блока 25. Для этого с помощью блоков 22 и 23 вычисляются модули напряжений на выходах интеграторов 19 и 20 и на блоке 25 производится их сравнение. При этом, если напряжение на первом входе блока 25 будет больше, чем на втором входе, что соответствует случаю, когда на входе имеется сигнал с частотой Ы(, то на первом выходе блока 25 появится положительный импульс, а на втором выходе - отрицательный импульсПоложительньп импульс с первого выхода блока 25 поступает на первьп выход блока 18 принятия решения и выход устройства. Положительный импульс на первом выходе блока 18 принятия решения означает, что входной сигнал имеет частоту И(Если на втором входе блока напряжение окажется больше, чем на первом входе, то на ее первом выходе будет отрицательный импульс, а на втором выходе - положительный импульс. Отрицательный импульс с первого выхо- да блока 25 поступает на выход устройства и означает, что входной сигнал имеет частоту ы .Принятие решения о фазе входного сигнала осуществляется с помощью триггера Шмитта 21 и блока 2 б при поступлении входного сигнала с частотой сд( Ф с помощью триггера Шмитта 24 и блока 2 при поступлении входного сигнала с частотой Иг .Это происходит следующим образом.При поступлении входного сигнала с частотой У на втором входе блока 2 б будет положительный импульс, который открывает эту схему,Знак напряжения на выходе интегратора 19 определяется с помощью триггера Шмитта 21. Если фаза входного сигнала равна "О", то на выходе триг" гера Шмитта 21 будет положительноео напряжение, если фаза равна 180 - - отрицательное напряжение. Это напряжение через открытый элемент ИЛИ 28 проходит на второй выход блока 18 принятия решения, На втором входе элемент ИЛИ 28 в этот момент сигнал отсутствует, так как блок 2 будет закрыт отрицательным импульсом с второго выхода блока 25.Аналогично, при поступлении входного сигнала с частотой Я на выход блока 18 принятия решения с выхода триггера Шмитта 24 проходит напряжение, знак которого соответствует . фазе входного сигнала. Формула изобретения 1. Приемник сигналов, модулированных одновременно по частоте и фазе, содержащий первый и второй пере- множители, выходы которых соединены с входами сумматора, выход которого через последовательно соединенные первый узкополосный фильтр, делитель частоты и третий перемножитель сое1298945 Составитель Н,ЛазареваРедактор Й,Гратилло Техред А.Кравчук Корректо мчи Подписикомитета СССРоткрытийская наб., д, 4/5 639енноготений5, Рауш каз 901/61 Тираж ВНИИПИ Государст по делам изобр 113035, Москва, Ж Проектная, 4 полиграфическое предприятие, г, Ужго Производс динен с входом второго узкополосного фильтра, первый манипуляционный фильтр, выход четвертого перемножителя соединен с входом второго манипуляционного фильтра, о т л и ч а ющ и й с я тем, что, с целью повышения помехоустойчивости, введены пятый, шестой и седьмой перемножители, первый и второй фазовращатели, управляемый генератор, фильтр нижних 10 частот и блок принятия решения, причем первые входы четвертого, пятого, шестоГо и седьмого перемножителей объединены и являются входом приемника, выходы четвертого, пятого,шес того и седьмого перемножителей соединены соответственно с первым и вторым входами второго перемножителя, первым входом первого перемножителя и объединенными вторым входом пер вого перемножителя и входом первого манипуляционного фильтра, выход которого соединен с первым входом блока принятия решения, второй вход которого соединен с выходом второго25 манипуляционного фильтра, а третий вход является тактовым входом приемника, выход сумматора через последовательно соединенные фильтр нижних частот и управляемый генератор сое динен .с вторым входом третьего перемножителя и вторым входом седьмогоперемножителя, а также через первыйфазовращатель - с втбрым входом шестого перемножителя, выход второгоузкополосного фильтра соединен с вторым входом пятого перемножителя ивходом второго фазовращателя, подключенным к второму входу четвертого перемножителя, первый и второй выходыблока принятия решения являются соответственно первым и вторым выходами приемника,2, Приемник по п, 1, о т л и ч аю щ и й с, я тем, что блок принятия решения состоит из последовательно соединенных первых интегратора,триггера Шмитта и блока запрета, последовательно соединенных вторых интегратора, триггера Шмитта и блока запрета, выходы обоих блоков запрета соединены с входами элемента ИЛИ, выход которого является вторым выходом приемника, выходы первого и второго интеграторов через соответствующие блоки вычисления модуля соединены с входами блока сравнения, выходы которого соединены с вторыми входами соответствующих блоков запрета, один выход блока сравнения является первым выходом приемника.

СмотретьЗаявка

3975289, 11.11.1985

ВОЙСКОВАЯ ЧАСТЬ 32103

АБДАЛОВ ЯЗИТ ТАМИМОВИЧ, ЖЕСТКОВ АЛЕКСАНДР МИХАЙЛОВИЧ, ЗЕЛЕНЦОВ ВЯЧЕСЛАВ АЛЕКСЕЕВИЧ, МАЙСЮРА СЕРГЕЙ ДМИТРИЕВИЧ

МПК / Метки

МПК: H04L 27/32

Метки: модулированных, одновременно, приемник, сигналов, фазе, частоте

Опубликовано: 23.03.1987

Код ссылки

<a href="https://patents.su/4-1298945-priemnik-signalov-modulirovannykh-odnovremenno-po-chastote-i-faze.html" target="_blank" rel="follow" title="База патентов СССР">Приемник сигналов модулированных одновременно по частоте и фазе</a>

Предыдущий патент: Устройство формирования частотно-модулированных сигналов

Следующий патент: Устройство автоподстройки несущей частоты

Случайный патент: Держатель буксирного троса