Устройство для моделирования процессов движения поездов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

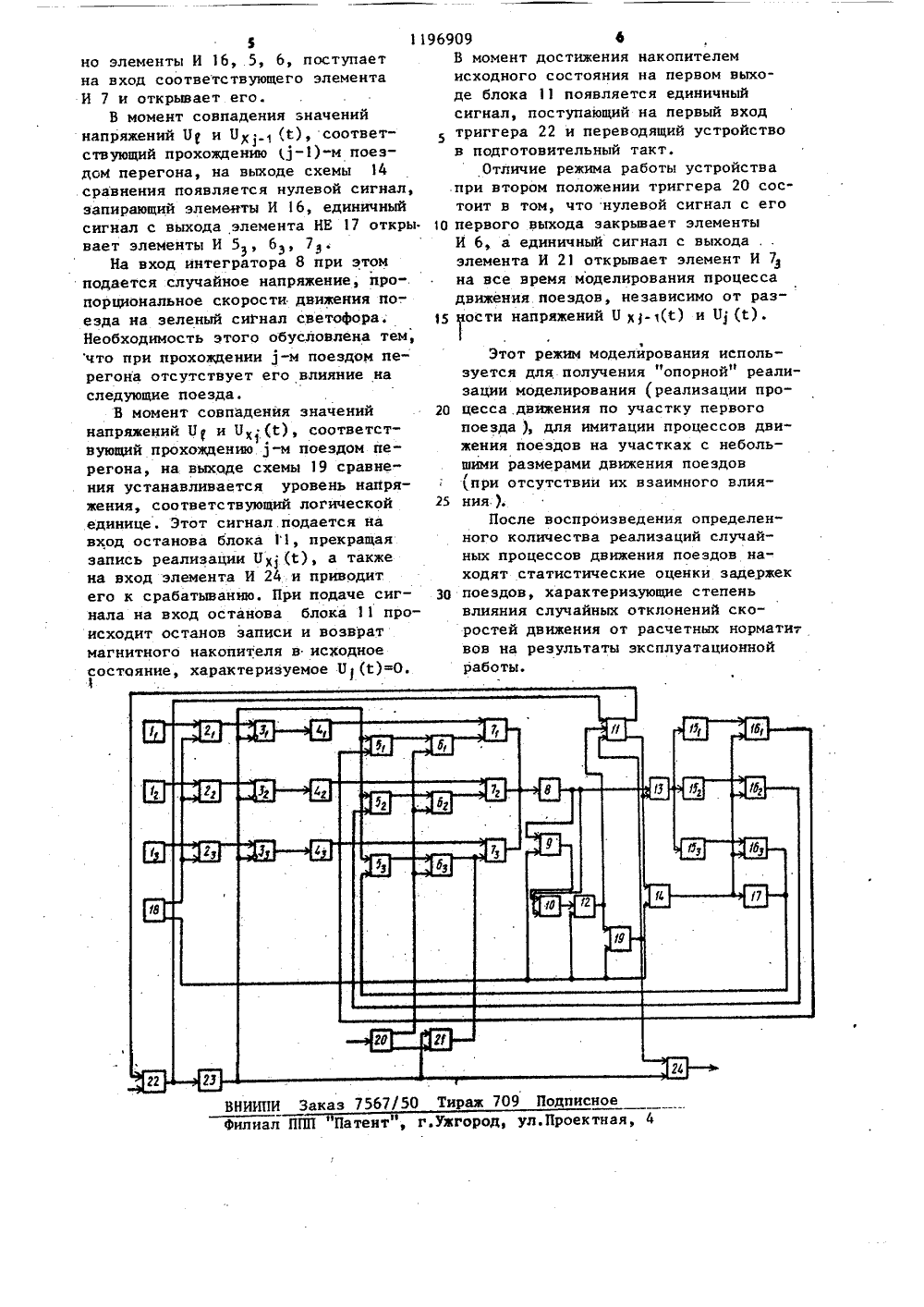

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК 7 Е ИЗОБРЕ НИЯ ИСА ТЕЛЬСТВУ ТОРСКОМУ(21) (22) (46) (71) ения,и ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТЮ 3792370/24-2408.06.8407.12.85. Вюл. У 45Московский ордена Ленина и ордена Трудового Красного Знамени институт инженеров железнодорожного транспорта(56) Авторское свидетельство СССР В 451104, кл. О 06 Р 520, 1971.Авторское свидетельство СССР У 1018130,.кл. 6 06 С 7/52, 1982. (54)(57) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ ПРОЦЕССОВ ДВИЖЕНИЯ ПОЕЗДОВ, содержащее группу генераторов случайных напряжений, группу сумматоров, группу запоминающих блоков, интегратор, запоминающий блок, источник опорных напряжений, пять групп элементов И по три элемента И в каждой, элемент НЕ, две схемы. сравнения, первый.и второй триггеры, элемент задержки, два элемента И, группу амплитудных дискриминаторов, дифференциальный уснлитель, первый выход источника опорных напряжений подключен к первым входам сумматоров: группы, выходы генераторов случайных напряжений соединены с вторыми входами сумматоров группы, входы которых соединены соответственно с прямыми входами элементов И первой группы, инверсные входы которых соединены с выходом элемента задержки, первыми входами первого и второго элементов И, выходы элементов И первой группы подключены к входам соответствующих запоминающих блоков группы, выходы которых соединены с первыми входами элементов И второй группы, вторые входы которых подключены соответственно к выходам элементов И третьей группы, выходы элементов И второй группы соединены с входом интегратора, выход которого подключен к первому входу дифференциального усилителя, второй вход которого соединенс первым выходом запоминающего блока и первым входом первой схемы сравнения, второй вход которой подключен к второму выходу источника опорных напряжений и первомувходу второй схемы сравн вход разрешения считьвання запои нающего блока подключен к первому выходу первого триггера и входу элемента задержки, вход запрещения считьвания запоминающего блока соединенс выходом второй схемы сравнения и вторым входом второго элемента И, второй выход запоминающего блока соединен с первым входом первого триггера, второй вход которого является входом запуска устройства, первые входы элементов И четвертой группы соединены с выходом элемента задержки, выходы элементов И четвертой .группы подключены соответственно к первым входам элементов И третьей группы, вторые входы которых соединены с первым выходом второго триггера, второй выход которого подключен к .второму входу первого элемента И, выхбд которого соединен с вторым вхо.дом третьего элемента И второй группы выход дифференциального усилителя соединен с входами амплитудных дискриминаторов группы, выходы кото рых подключены соответственно к первым входам элементов И пятой группы,вторые входы которых соединены с выходом первой схемы сравнения и входомэлемента НЕ, выход которого соединенс вторым входом третьего элемента Ичетвертой группы элементов И, выходыэлементов И пятой группы соединеныс вторыми входами элементов Ичетвертой группй соответственно, выходвторого элемента И является выходомустройства, счетный вход второготриггера является входом переключениярежимов работы устройства, о т -л и ч а ю щ е е с я тем, что, с целью повышения точности моделирования,оно дополнительно содержит третьюсхему сравнения, третий элемент И,196909сумматор, причем первый вход третьей схемы сравнения подключен квыходу интегратора, второй входтретьей схемы сравнения соединен свторым выходом источника опорныхнапряжений, выход третьей схемысравнения подключен к первому входу третьего элемента И, второйвход которого соединен с выходоминтегратора, выход третьего элемента И соединен с первым входом сумматора, второй вход которого соединенс вторым выходом источника опорных напряжений, выход сумматораподключен к информационному входу запоминающего блока н второму входу второй схемы сравнения.1Изобретение относится к вычислительной технике и может быть использовано при моделировании сложных процессов движения транспортных средств, а также при составлении графиков движения поездов.Цель изобретения - повышение точности, моделирования.На чертеже представлена схема устройства для моделирования процессов движения поездов.Устройство содержит группу генераторов 1 случайных напряжений, группу сумматоров 2, первую группу элементов И 3, первую группу запоминающих блоков 4, четвертую группу элементов И 5, третью 6 и вторую 7 группы элементов И, интегратор 8, третью схему 9 сравнения, третий элемент И 10, первый запоминающий блок 11, второй сумматор 12, дифференциальный усилитель 13, первую схему 14 сравнения, группу амплитудных дискриминаторов 15, пятую группу элементов И 16, элемент НЕ 17, источник 18 опорных напряжений, вторую схему 19 сравнения, второй триггер 20, первый элемент И 21, первый триггер 22, элемент 23 задержки, вто. рой элемент И 24.Устройство для моделирования процессов движения поездов работает следующим образом. 3Триггер 20 имеет два положенияи задает режимы работы устройства.В первом положении на первом выходетриггера 20 имеется единичный сигнал,а на втором - нулевой. При этомустройство имитирует процессы движения поездов с учетом их взаимноговлияния, т.е, на различные ( зеленые,желтые или красные ) показания путе 10 вых светофоров.Во втором положении на первомвыходе триггера 20 имеется нулевойсигнал, а на втором - единичный.В этом случае устройство моделирует15 процесс движения поезда на зеленыепоказания светофоров . Необходимостьиспользования данного режима работысвязана с тем, что воспроизведенныйустройством процесс движения первого20 поезда является опорной реализацией моделирования,Устройство при первом положениитриггера 20 работает следующим образом.25 Каждый из генераторов 1 вырабатывает значения случайных напряжений,пропорциональные отклонениям отрасчетной величины скорости движе"ния поезда на зеленое (1 З), желтое30 (1 ) и красное (1 ) показание путейвого светофора. Эти напряжения подаются на входы соответствующих сумматоров 2, где происходит суммирова30 з 1196ние постоянных напряжений, пропорцио.нальных расчетным значениям скоростидвижения поезда, со случайныминапряжениями, пропорциональными отклонениям скорости поезда от Норматива.Устройство работает тактами. Вподготовительном такте на.выходахтриггера 22, элемента 23 задержки,интегратора 8, запоминающего блока 011, дифференциального усилителя 13,амплитудных дискриминаторов 15,схем 9 и 9 сравнения имеютсянулевые сигналы, а на выходе схемы14 сравнения - единичный сигнал,элементы И 3 открыты по инверсномувходу, элементы И 5, 6, 16 и 24 закрыты. При этом случайные напряженияс выходов сумматоров 2 через соответствующие элементы И 3 подаются20на блоки 4 запоминания.Единичный сигнал с Выхода триггера 20 поступает на вторые входыэлементов И 6.В момент времени, соответствующийотправлению 1-го поезда на перегон,запускающий импульс опрокидываеттриггер 22 и на его выходе появляетсяединичный сигнал, поступающий напервый вход блока 1 памяти и навход элемента 23 задержки.Йа втором входе блока 11 начинает"ся воспроизведение реализации напряжения Б (й), имитирующего процессдвижения хвоста Ц)-го поезда.Напряжение Пх ,(й) подается навход дифференциального усилителя 13и на вход схемы 14 сравнения. На выходе усилителя 13 определяется раз"ность а 1(с) напряжения Пх, (й) инапряжения(г.), имитирующего 401-1процесс движения головы 1-го поезда,с выхода интегратора 8, поступающаяна входы амплитудных дискриминатороВ,При подаче сигнала на вход элемента 23 задержки им формируется интервал времени, пропорциональный реальному интервалу времени между моментами отправления (1-)-го и 1-го поездов.По окончании этого интервала на 0выходе элемента 23 появляется единичный сигнал, поступивший на входы элементов И 3, 5, 21 и 24. При подачеэтого сигнала на входы элементов И 3происходит их запирание. Выходы сумма-торов 2 отключаются от входов блоков 4, в которых фиксируются случайные напряжения, пропорциональные 909 4скорости движения поезда на различные сигналы путевых светофоров,В момент появления на выходе элемента 23 единичного сигнала на выходе усилителя 13 имеется некоторое напряжение АП(1), пропорциональное расстоянию между хвостом (1-1)-го и головой 3-го поездов. В зависимости от величины этого напряжения происходит срабатывание соответствующего амплитудного дискриминатора 15 и на его выходе появляется единичный сигнал.Этот сигнал открывает соответствующйй элемент И 16, сигнал с его выхода открывает определенный элемент И 5. Единичный сигнал с выхода последнего подается на первый вход соответствующего элемента И 6, открывая его.При подаче сигнала с выхода эле-мента И 6 на второй вход соответствующего элемента И 7 напряжение с выхода запоминающего блока 4 подается на вход интегратора 8. На выходе последнего генерируется реализация линейно нарастающего напряжения 1 (й), имитируя процесс движения головы 1-го поезда на соответствующее показание путевого светофора. Напряжение (С) с выхода интег 1ратора 8 подается иа первый вход схемы 9 сравнения, где производится его сравнение с опорным напряжением д, пропорциональным длине поезда,В момент совпадения напряжений Б(й) н 1 и срабатывает схема 9 сравнения и единичный сигнал с ее выхода открывает элемент И 10. При этом напряжеиие (й) поступает на вход сумматора 12. На его выходе определяется разность напряжений Би Бр, поступающая на информационный вход блока 11, где происходит ее запоминание.Вычисленная в усилителе 13 разность напряженийк1и О (й) подается на входы амплитудных дискриминаторов 15 и сравнивается с эталонными напряжениями, пропорциональными длине одного, двух и трех блок-участков, что соответствует движению поезда на красное, желтое или зеленое показания светофора,На основании результатов сравнения срабатывает один из амплитудных дискриминаторов 15 группы, а сигнал с его выхода, открывая последователь5но элементы И 16, 5, 6, поступаетна вход соответствующего элементаИ 7 и открывает его.В момент совпадения значенийнапряжений Б и О 1 й), соответствующий прохожденйю Д)-м поездом перегона, на выходе схемы 14сравнения появляется нулевой сигнал,запирающий элементы И 16, единичныйсигнал с выхода элемента НЕ 17 откры.вает элементы И 5 р 6,На вход интегратора 8 при этомподается случайное напряжение, пропорциональное скорости движения по-.езда на зеленый сигнал светофора.Необходимость этого обусловлена тем,что при прохождении 1-м поездом перегона отсутствует его влияние наследующие поезда.В момент совпадения значенийнапряжений Юи 11 (й), соответствующий прохождению 1-м поездом перегона, на выходе схемы 19 сравнения устанавливается уровень напряжения, соответствующий логическойединице. Этот сигнал подается навход останова блока 11, прекращаязапись реализации 01(й), а такжена вход элемента И 24 и приводитего к срабатыванию. При подаче сигнала на вход останова блока 11 происходит останов записи и возвратмагнитного накопителя в исходноесостояние, характеризуемое 01(й)=0. 196909 аВ момент достижения накопителемисходного состояния на первом выходе блока 11 появляется единичныйсигнал, поступающий на первый входтриггера 22 и переводящий устройствов подготовительный такт.Отличие режима работы устройствапри втором положении триггера 20 состоит в том, что нулевой сигнал с его 1 О первого выхода эакрывает элементыИ 6, а единичный сигнал с выходаэлемента И 21 открывает элемент И 7на все время моделирования процессадвижения. поездов, независимо от раз 1 ности напряжений О ат.(т) и п (т). Этот режим моделирования используется для получения "опорной" реализации моделирования (реализации про цесса.движения по участку первогопоезда ), для имитации процессов движения поездов на участках с небольшими размерами движения поездов/при отсутствии их взаимного влия ния ),После воспроизведения определенного количества реализаций случайных процессов движения поездов находят статистические оценки задержек ЗО поездов, характеризующие степеньвлияния случайных отклонений скоростей движения от расчетных норматитвов на результаты эксплуатационнойработы.

СмотретьЗаявка

3792370, 08.06.1984

МОСКОВСКИЙ ОРДЕНА ЛЕНИНА И ОРДЕНА ТРУДОВОГО КРАСНОГО ЗНАМЕНИ ИНСТИТУТ ИНЖЕНЕРОВ ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА

ДРУЖИНИН ГЕОРГИЙ ВАСИЛЬЕВИЧ, КАРПОВ ЛЕОНИД АНАТОЛЬЕВИЧ, ГРИБКОВ ВИКТОР ИВАНОВИЧ

МПК / Метки

МПК: G06G 7/52

Метки: движения, моделирования, поездов, процессов

Опубликовано: 07.12.1985

Код ссылки

<a href="https://patents.su/4-1196909-ustrojjstvo-dlya-modelirovaniya-processov-dvizheniya-poezdov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования процессов движения поездов</a>

Предыдущий патент: Устройство для определения среднего значения

Следующий патент: Устройство для вычисления коэффициента запаса статической устойчивости узла нагрузки электрической сети

Случайный патент: Захватное устройство подъемного крана для гидротехнических затворов